MAX6846–MAX6849 Low-Power, Adjustable Battery Monitors with Hysteresis and Integrated µP Reset General Description

... (to disable system operation). These devices also have an independent µP supervisor that monitors VCC and provides an active-low reset output. A manual reset function is available to reset the µP with a pushbutton. The MAX6846–MAX6849 are ideal for single-cell lithiumion (Li+) or multicell alkaline/ ...

... (to disable system operation). These devices also have an independent µP supervisor that monitors VCC and provides an active-low reset output. A manual reset function is available to reset the µP with a pushbutton. The MAX6846–MAX6849 are ideal for single-cell lithiumion (Li+) or multicell alkaline/ ...

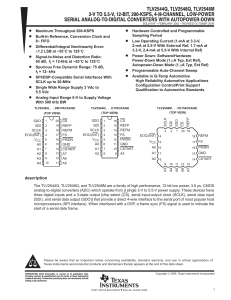

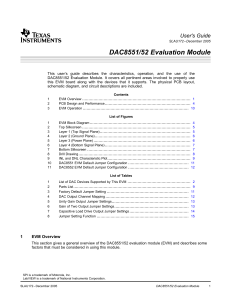

3-V to 5.5-V, 12-Bit, 200-KSPS, 4-/8-Channel

... Configuration data is stored in one 12-bit configuration register (CFR) (see Table 2 for CFR bit definitions). Once configured after first power up, the information is retained in the H/W or S/W power down state. When the device is being configured, a write CFR cycle is issued by the host processor. ...

... Configuration data is stored in one 12-bit configuration register (CFR) (see Table 2 for CFR bit definitions). Once configured after first power up, the information is retained in the H/W or S/W power down state. When the device is being configured, a write CFR cycle is issued by the host processor. ...

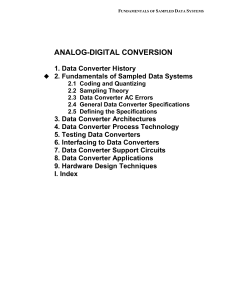

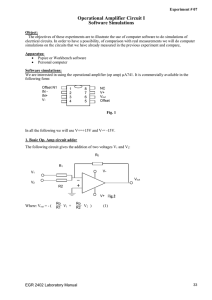

Full PowerPoint

... • Now we can find “propagation delay” tp; the time between the input reaching 50% of its final value and the output to reaching 50% of final value. • Today’s case, using “perfect input” (50% reached at t=0): 0.5 = e-tp tp = - ln 0.5 = 0.69 It takes 0.69 time constants, or 0.69 RC. • We can find the ...

... • Now we can find “propagation delay” tp; the time between the input reaching 50% of its final value and the output to reaching 50% of final value. • Today’s case, using “perfect input” (50% reached at t=0): 0.5 = e-tp tp = - ln 0.5 = 0.69 It takes 0.69 time constants, or 0.69 RC. • We can find the ...

BD9488F : LED / LCD Drivers

... ○When the DC signal is used, ADIM_P will be pulled up more than 4.2V, and the signal input to the pin ADIM. ADIM_P In the driver module with more than two BD9488, and the analog dimming is performed by ADIM the duty signal, the architecture will be shown in the right figure. That can reduce the LED ...

... ○When the DC signal is used, ADIM_P will be pulled up more than 4.2V, and the signal input to the pin ADIM. ADIM_P In the driver module with more than two BD9488, and the analog dimming is performed by ADIM the duty signal, the architecture will be shown in the right figure. That can reduce the LED ...

Long Delay Timers - Lattice Semiconductor

... the user for sequencer and/or general I/O control. In order to expand the timers and allow for building very long delays, a prescaled, CPLD clock signal is brought out from a timer (Timer4), through OUT16, an open-drain output pin, and is then routed externally to the FPGA fabric as a base timing si ...

... the user for sequencer and/or general I/O control. In order to expand the timers and allow for building very long delays, a prescaled, CPLD clock signal is brought out from a timer (Timer4), through OUT16, an open-drain output pin, and is then routed externally to the FPGA fabric as a base timing si ...

GE 80A GigaDLynx : Non-Isolated DC-DC Power Modules Preliminary Data Sheet

... The 80A Digital GigaDLynxTM power modules are non-isolated dc-dc converters that deliver up to 80A of output current. These modules operate over a wide range of input voltage (VIN =4.5Vdc - 14Vdc) and provide a precisely regulated output voltage from 0.6Vdc to 2Vdc, programmable via an external resi ...

... The 80A Digital GigaDLynxTM power modules are non-isolated dc-dc converters that deliver up to 80A of output current. These modules operate over a wide range of input voltage (VIN =4.5Vdc - 14Vdc) and provide a precisely regulated output voltage from 0.6Vdc to 2Vdc, programmable via an external resi ...

MAX6948B High-Efficiency PWM LED Driver with Boost EVALUATION KIT AVAILABLE

... load current at up to 28V. The converter is stable under all load conditions from 5V up to 28V and includes open-circuit detection to prevent damage to the IC. An I2C-programmable 10-bit pulse-width modulation (PWM) signal enables 1024 levels of WLED intensity. The five GPIO ports function as logic ...

... load current at up to 28V. The converter is stable under all load conditions from 5V up to 28V and includes open-circuit detection to prevent damage to the IC. An I2C-programmable 10-bit pulse-width modulation (PWM) signal enables 1024 levels of WLED intensity. The five GPIO ports function as logic ...

MAX5842 Quad, 12-Bit, Low-Power, 2-Wire, Serial Voltage-Output DAC General Description

... occurs in the same high pulse as a START condition (Figure 3). This condition is not a legal I2C format; at least one clock pulse must separate any START and STOP conditions. Repeated START Conditions A REPEATED START (S r ) condition may indicate a change of data direction on the bus. Such a change ...

... occurs in the same high pulse as a START condition (Figure 3). This condition is not a legal I2C format; at least one clock pulse must separate any START and STOP conditions. Repeated START Conditions A REPEATED START (S r ) condition may indicate a change of data direction on the bus. Such a change ...

LTM4615 - Triple Output, Low Voltage

... to control the master ramp rate, or an external ramp can be applied to the master regulator’s track pin to control it. Slave operation is performed by putting a resistor divider from the master output to ground, and connecting the center point of the divider to this pin on the slave regulator. If tr ...

... to control the master ramp rate, or an external ramp can be applied to the master regulator’s track pin to control it. Slave operation is performed by putting a resistor divider from the master output to ground, and connecting the center point of the divider to this pin on the slave regulator. If tr ...

Analog-to-Digital Conversion via Time

... voltage comparators, and switch capacitor networks to perform their signal processing. When compared to digital circuitry, these analog circuit blocks consume significant power, occupy large silicon areas, and operate at relatively slow data processing speeds. A signal processing methodology is prop ...

... voltage comparators, and switch capacitor networks to perform their signal processing. When compared to digital circuitry, these analog circuit blocks consume significant power, occupy large silicon areas, and operate at relatively slow data processing speeds. A signal processing methodology is prop ...

AN4812, Initializing the MPC5777M Clock Generation Module and

... (ME_MCTL). If the power level (PWRLVL field within the various mode configuration registers) is different between the current and target modes, the PCS mechanism is enabled causing the system clock frequency to ramp down and/or up in multiple steps. For example, consider two modes with two different ...

... (ME_MCTL). If the power level (PWRLVL field within the various mode configuration registers) is different between the current and target modes, the PCS mechanism is enabled causing the system clock frequency to ramp down and/or up in multiple steps. For example, consider two modes with two different ...

D4 HP Dimmer User’s Manual Rev 1.01

... switches or using RDM. Whichever method is used last takes precedence. The unit maintains the last used setting over power cycles, and checks on power up to see if switches have been changed while the unit was off. Smoothing (Dimmer Response Time) When the LED Curve is selected, one of six different ...

... switches or using RDM. Whichever method is used last takes precedence. The unit maintains the last used setting over power cycles, and checks on power up to see if switches have been changed while the unit was off. Smoothing (Dimmer Response Time) When the LED Curve is selected, one of six different ...

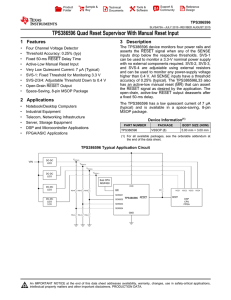

STM1810

... feature a debounced manual reset feature that asserts a reset if the RST pin is pulled low for more than 1.5 µs. When used to initiate manual reset, RST debounces signals from devices such as mechanical switches. For devices with this feature, the release of the external switch triggers the reset pe ...

... feature a debounced manual reset feature that asserts a reset if the RST pin is pulled low for more than 1.5 µs. When used to initiate manual reset, RST debounces signals from devices such as mechanical switches. For devices with this feature, the release of the external switch triggers the reset pe ...

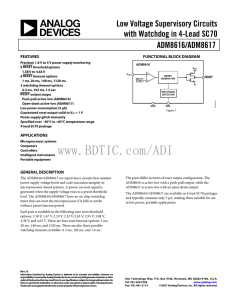

ADM8616 数据手册DataSheet 下载

... voltage supervision by controlling the microprocessors RESET input. Code execution errors are avoided during power-up, power-down, and brownout conditions by asserting a RESET signal when the supply voltage is below a preset threshold and by allowing supply voltage stabilization with a fixed timeout ...

... voltage supervision by controlling the microprocessors RESET input. Code execution errors are avoided during power-up, power-down, and brownout conditions by asserting a RESET signal when the supply voltage is below a preset threshold and by allowing supply voltage stabilization with a fixed timeout ...

MAX5841 Quad, 10-Bit, Low-Power, 2-Wire, Serial Voltage-Output DAC General Description

... occurs in the same high pulse as a START condition (Figure 3). This condition is not a legal I2C format; at least one clock pulse must separate any START and STOP conditions. Repeated START Conditions A REPEATED START (S r ) condition may indicate a change of data direction on the bus. Such a change ...

... occurs in the same high pulse as a START condition (Figure 3). This condition is not a legal I2C format; at least one clock pulse must separate any START and STOP conditions. Repeated START Conditions A REPEATED START (S r ) condition may indicate a change of data direction on the bus. Such a change ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.