Atmel AT42QT1012 One-channel Toggle-mode QTouch Touch Sensor IC with Power Management Functions

... load; driving the QT1012 VDD pin directly from another logic gate or a microcontroller port will serve as both power and “forced recalibration”. The source resistance of most CMOS gates and microcontrollers is low enough to provide direct power without a problem. ...

... load; driving the QT1012 VDD pin directly from another logic gate or a microcontroller port will serve as both power and “forced recalibration”. The source resistance of most CMOS gates and microcontrollers is low enough to provide direct power without a problem. ...

TSC2000 数据资料 dataSheet 下载

... bus. All peripheral functions are controlled through the registers and onboard state machines. The TSC2000 consists of the following blocks (refer to the block diagram on the front page): • Touch Screen Interface ...

... bus. All peripheral functions are controlled through the registers and onboard state machines. The TSC2000 consists of the following blocks (refer to the block diagram on the front page): • Touch Screen Interface ...

PCA9515A 1. General description I

... more devices or longer length can be accommodated. It can also be used to run two buses, one at 5 V and the other at 3.3 V or a 400 kHz and 100 kHz bus, where the 100 kHz bus is isolated when 400 kHz operation of the other is required. Two or more PCA9515As cannot be put in series. The PCA9515A desi ...

... more devices or longer length can be accommodated. It can also be used to run two buses, one at 5 V and the other at 3.3 V or a 400 kHz and 100 kHz bus, where the 100 kHz bus is isolated when 400 kHz operation of the other is required. Two or more PCA9515As cannot be put in series. The PCA9515A desi ...

50 µA, 550 kHz Rail-to

... The ESD protection on the inputs can be depicted as shown in Figure 4-2. This structure was chosen to protect the input transistors, and to minimize input bias current (IB). The input ESD diodes clamp the inputs when they try to go more than one diode drop below VSS. They also clamp any voltages tha ...

... The ESD protection on the inputs can be depicted as shown in Figure 4-2. This structure was chosen to protect the input transistors, and to minimize input bias current (IB). The input ESD diodes clamp the inputs when they try to go more than one diode drop below VSS. They also clamp any voltages tha ...

Atmel LED Driver-MSL2162 Datasheet Brief EEPROM, and SPI Bus

... LED string intensity control for up to eight interconnected devices. Frame-byframe control allows active area dimming and phase shifted PWM timing for improved backlight performance. The advanced PWM engine synchronizes PWM dimming to the video signals for reduced motion blur and waterfall noise. Th ...

... LED string intensity control for up to eight interconnected devices. Frame-byframe control allows active area dimming and phase shifted PWM timing for improved backlight performance. The advanced PWM engine synchronizes PWM dimming to the video signals for reduced motion blur and waterfall noise. Th ...

Multiple Input Single Output (MISO)

... Figure 3-3: Schematic of MISO Flyback Converter Design..................................................................... 9 Figure 3-4: Simulation Result of the output voltage and one of the primary winding current of the MISO Flyback Converter ..................................................... ...

... Figure 3-3: Schematic of MISO Flyback Converter Design..................................................................... 9 Figure 3-4: Simulation Result of the output voltage and one of the primary winding current of the MISO Flyback Converter ..................................................... ...

Installation Manual

... Dry: Do not allow water or other fluids to splash or drip on to the inverter. Cool: Ambient, air temperature should be between 0°C and 50°C (32°F and 122°F). Power linearly derates from 100% at 25°C to 70% at 50°C. Ventilated: Provide a minimum of 5 inches (13cm) of clearance at the DC end of invert ...

... Dry: Do not allow water or other fluids to splash or drip on to the inverter. Cool: Ambient, air temperature should be between 0°C and 50°C (32°F and 122°F). Power linearly derates from 100% at 25°C to 70% at 50°C. Ventilated: Provide a minimum of 5 inches (13cm) of clearance at the DC end of invert ...

LM139/LM239/LM339/LM2901/LM3302 Low Power Low Offset

... Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than −0.3 VDC (or 0.3 VDCbelow the magnitude of the negative powe ...

... Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than −0.3 VDC (or 0.3 VDCbelow the magnitude of the negative powe ...

SM72240 SolarMagic 5-Pin Microprocessor Reset Circuit (Rev. C)

... Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been de ...

... Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been de ...

V108i Series Handbook (HA136435 Iss 1)

... 1. Automatic resetting means that, once the alarm has been acknowledged, it will automatically clear when it is no longer true. 2. Manual resetting means that the alarm must first clear before it can be reset. 3. In blocking mode, after power on, the process value must first enter a good state befor ...

... 1. Automatic resetting means that, once the alarm has been acknowledged, it will automatically clear when it is no longer true. 2. Manual resetting means that the alarm must first clear before it can be reset. 3. In blocking mode, after power on, the process value must first enter a good state befor ...

USB3290 Small Footprint Hi-Speed USB 2.0 Device PHY with UTMI

... reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described se ...

... reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described se ...

Lower Power Synthesis - VADA

... The Bus-Invert method proposed here uses one extra control bit called invert. By convention then invert = 0 the bus value will equal the data value. When invert = 1 the bus value will be the inverted data value. The peak power dissipation can then be decreased by half by coding the I/O as follow 1. ...

... The Bus-Invert method proposed here uses one extra control bit called invert. By convention then invert = 0 the bus value will equal the data value. When invert = 1 the bus value will be the inverted data value. The peak power dissipation can then be decreased by half by coding the I/O as follow 1. ...

Atmel AVR1300: Using the Atmel AVR XMEGA ADC

... The ADC conversion block has a 12-stage pipelined architecture capable of sampling several signals in parallel. There are four input selection multiplexers with individual configurations. The separate configuration settings for the four multiplexers can be viewed as virtual channels, with one set of ...

... The ADC conversion block has a 12-stage pipelined architecture capable of sampling several signals in parallel. There are four input selection multiplexers with individual configurations. The separate configuration settings for the four multiplexers can be viewed as virtual channels, with one set of ...

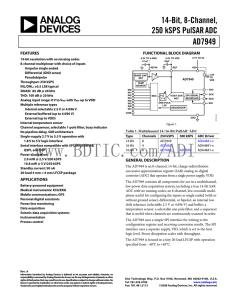

AD7949 数据手册DataSheet下载

... connected as close to REF as possible. See the Reference Decoupling section. Internal Reference Output/Reference Buffer Input. See the Voltage Reference Output/Input section. When using the internal reference, the internal unbuffered reference voltage is present and needs decoupling with a 0.1μF cap ...

... connected as close to REF as possible. See the Reference Decoupling section. Internal Reference Output/Reference Buffer Input. See the Voltage Reference Output/Input section. When using the internal reference, the internal unbuffered reference voltage is present and needs decoupling with a 0.1μF cap ...

AM4964 Description A Product Line of

... The CT pin will have a capacitor connected to ground. It is a multi-function pin providing timing for the lock detect and auto-restart. Different rates of charge and discharge of CT capacitor depending on the mode of operation (fan operation status) give the lock-detect time (tLCKDET) and lock time ...

... The CT pin will have a capacitor connected to ground. It is a multi-function pin providing timing for the lock detect and auto-restart. Different rates of charge and discharge of CT capacitor depending on the mode of operation (fan operation status) give the lock-detect time (tLCKDET) and lock time ...

FDMF6706C – Extra-Small, High-Performance, High- Frequency DrMOS Module FD MF6706C

... gate drive design. The 3-state gate drive has both logic HIGH level and LOW level, along with a 3-state shutdown window. When the PWM input signal enters and remains within the 3-state window for a defined hold-off time (tD_HOLD-OFF), both GL and GH are pulled LOW. This feature enables the gate driv ...

... gate drive design. The 3-state gate drive has both logic HIGH level and LOW level, along with a 3-state shutdown window. When the PWM input signal enters and remains within the 3-state window for a defined hold-off time (tD_HOLD-OFF), both GL and GH are pulled LOW. This feature enables the gate driv ...

Pro-Solo mkII Manual

... Gate is the most common signal used for telling a synth when to play its note. The high level Gate is suitable for most synths, such as Roland, SCI, ARP, Oberheim. The low level gate may be needed for synths that require a lower gate voltage such as the SH-101. S-trig no pull-up ...

... Gate is the most common signal used for telling a synth when to play its note. The high level Gate is suitable for most synths, such as Roland, SCI, ARP, Oberheim. The low level gate may be needed for synths that require a lower gate voltage such as the SH-101. S-trig no pull-up ...

PCAL9554B; PCAL9554C 1. General description Low-voltage 8-bit I

... conflicts. NXP I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in ACPI power switches, sensors, push buttons, LEDs, fan control, etc. In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5. ...

... conflicts. NXP I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in ACPI power switches, sensors, push buttons, LEDs, fan control, etc. In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5. ...

LTM8031 - Ultralow Noise EMC 36V, 1A DC/DC uModule Regulator

... minimum recommended values for the associated operating conditions. Applying capacitor values below those indicated in Table 1 is not recommended, and may result in undesirable operation. Using larger values is generally acceptable, and can yield improved dynamic response, if it is necessary. Again, ...

... minimum recommended values for the associated operating conditions. Applying capacitor values below those indicated in Table 1 is not recommended, and may result in undesirable operation. Using larger values is generally acceptable, and can yield improved dynamic response, if it is necessary. Again, ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.