TL072

... the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein: A. Life support devices or systems are devices or systems which: 1. are intended to implant into the body, or 2. support or sustain life and whose failure to perform when properly used in accordance w ...

... the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein: A. Life support devices or systems are devices or systems which: 1. are intended to implant into the body, or 2. support or sustain life and whose failure to perform when properly used in accordance w ...

HMMC-3102 DC-1 GHz Packaged Divide-by-Prescaler

... If an RF signal with sufficient signal to noise ratio is present at the RF input lead, the prescaler will operate and provide a divided output equal the input frequency divided by the divide modulus. Under certain “ideal” conditions where the input is well matched at the right input frequency, the c ...

... If an RF signal with sufficient signal to noise ratio is present at the RF input lead, the prescaler will operate and provide a divided output equal the input frequency divided by the divide modulus. Under certain “ideal” conditions where the input is well matched at the right input frequency, the c ...

LT5503

... Modulation Accuracy Insensitive to Carrier Input Power Modulator I/Q Inputs Internally Biased Available in 20-Lead FE Package ...

... Modulation Accuracy Insensitive to Carrier Input Power Modulator I/Q Inputs Internally Biased Available in 20-Lead FE Package ...

MXa Owner`s Manual

... on each channel will light for about three seconds, during which the output relays will stay open to mute the speakers. After the turn-on muting interval, the “PROT” LEDs turn off, the green “PWR” LEDs light, and the output relays close to enable the speaker outputs. Even during the muting interval, ...

... on each channel will light for about three seconds, during which the output relays will stay open to mute the speakers. After the turn-on muting interval, the “PROT” LEDs turn off, the green “PWR” LEDs light, and the output relays close to enable the speaker outputs. Even during the muting interval, ...

MAX8833 Dual, 3A, 2MHz Step-Down Regulator General Description Features

... The MAX8833 high-efficiency, dual step-down regulator is capable of delivering up to 3A at each output. The device operates from a 2.35V to 3.6V supply, and provides output voltages from 0.6V to 0.9 x VIN, making it ideal for on-board point-of-load applications. Total output error is less than ±1% o ...

... The MAX8833 high-efficiency, dual step-down regulator is capable of delivering up to 3A at each output. The device operates from a 2.35V to 3.6V supply, and provides output voltages from 0.6V to 0.9 x VIN, making it ideal for on-board point-of-load applications. Total output error is less than ±1% o ...

MAX14840E/MAX14841E 40Mbps, +3.3V, RS-485 Half-Duplex Transceivers General Description

... to a defined logic level. Leakage currents up to 10FA from the high-impedance output of a controller could cause DE and RE to drift to an incorrect logic state. Additionally, parasitic circuit board capacitance could cause coupling of VCC or GND to DE and RE. These factors could improperly enable th ...

... to a defined logic level. Leakage currents up to 10FA from the high-impedance output of a controller could cause DE and RE to drift to an incorrect logic state. Additionally, parasitic circuit board capacitance could cause coupling of VCC or GND to DE and RE. These factors could improperly enable th ...

MAX15050/MAX15051 High-Efficiency, 4A, 1MHz, Step-Down Regulators General Description

... to 5.5V, making them ideal for on-board point-of-load and postregulation applications. Total output-voltage accuracy is within ±1% over load, line, and temperature. The MAX15050/MAX15051 feature 1MHz fixed-frequency PWM operation. The MAX15050 features pulse-skip mode to improve light-load efficienc ...

... to 5.5V, making them ideal for on-board point-of-load and postregulation applications. Total output-voltage accuracy is within ±1% over load, line, and temperature. The MAX15050/MAX15051 feature 1MHz fixed-frequency PWM operation. The MAX15050 features pulse-skip mode to improve light-load efficienc ...

A Fully Integrated CMOS Phase-Locked Loop With 30MHz to 2GHz

... to high-Q LC oscillators. Careful design techniques need to be used to reduce the jitter or phase noise. An 8-stage ring oscillator was designed as shown in Figure 2. A fully differential mode was used to reduce the power supply and substrate noise. The VCO circuit based on this CMOS ring oscillator ...

... to high-Q LC oscillators. Careful design techniques need to be used to reduce the jitter or phase noise. An 8-stage ring oscillator was designed as shown in Figure 2. A fully differential mode was used to reduce the power supply and substrate noise. The VCO circuit based on this CMOS ring oscillator ...

T401 - T402 Operating Instructions 383E-64618

... With the binary input connected to 0V (=low) relay control parameter set „B“ is active. With the binary input left open (=high) relay control parameter set „A“ is active. Hold-Function: When selected; if the input frequency goes above the upper limit value (or below the lower limit value) the relay ...

... With the binary input connected to 0V (=low) relay control parameter set „B“ is active. With the binary input left open (=high) relay control parameter set „A“ is active. Hold-Function: When selected; if the input frequency goes above the upper limit value (or below the lower limit value) the relay ...

AD7839 - Analog Devices

... VSS to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V, –17 V Digital Inputs to GND . . . . . . . . . . . . . . –0.3 V, VCC + 0.3 V VREF(+) to VREF(–) . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +18 V VREF(+) to GND . . . . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V VR ...

... VSS to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V, –17 V Digital Inputs to GND . . . . . . . . . . . . . . –0.3 V, VCC + 0.3 V VREF(+) to VREF(–) . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +18 V VREF(+) to GND . . . . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V VR ...

PPT

... binary input combinations. • For each binary combination of the input variables, there is one possible output. ...

... binary input combinations. • For each binary combination of the input variables, there is one possible output. ...

74LVT14 3.3 V hex inverter Schmitt trigger

... 3.3 V hex inverter Schmitt trigger Rev. 02 — 25 April 2008 ...

... 3.3 V hex inverter Schmitt trigger Rev. 02 — 25 April 2008 ...

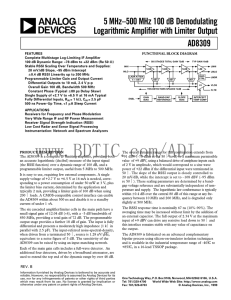

AD8309 数据手册DataSheet 下载

... references. Note that (1) is mathematically incomplete in representing the behavior of a demodulating log amp such as the AD8309, where VIN has an alternating sign. However, the basic principles are unaffected. ...

... references. Note that (1) is mathematically incomplete in representing the behavior of a demodulating log amp such as the AD8309, where VIN has an alternating sign. However, the basic principles are unaffected. ...

LTC6800 - Rail-to-Rail, Input and Output

... Whenever the differential input VIN changes, CH must be charged up to the new input voltage via CS. This results in an input charging current during each input sampling period. Eventually, CH and CS will reach VIN and, ideally, the input current would go to zero for DC inputs. In reality, there are ...

... Whenever the differential input VIN changes, CH must be charged up to the new input voltage via CS. This results in an input charging current during each input sampling period. Eventually, CH and CS will reach VIN and, ideally, the input current would go to zero for DC inputs. In reality, there are ...

LTC6915 - Linear Technology

... Note 5: The PSRR measurement accuracy depends on the proximity of the power supply bypass capacitor to the device under test. Because of this, the PSRR is 100% tested to relaxed limits at final test. However, their values are guaranteed by design to meet the data sheet limits. Note 6: Supply current ...

... Note 5: The PSRR measurement accuracy depends on the proximity of the power supply bypass capacitor to the device under test. Because of this, the PSRR is 100% tested to relaxed limits at final test. However, their values are guaranteed by design to meet the data sheet limits. Note 6: Supply current ...

MAX536/MAX537 Calibrated, Quad, 12-Bit Voltage-Output DACs with Serial Interface _______________General Description

... Guaranteed by design. Crosstalk is defined as the glitch energy at any DAC output in response to a full-scale step change on any other DAC. Digital inputs at 2.4V; with digital inputs at CMOS levels, IDD decreases slightly. All input signals are specified with tR = tF ≤ 5ns. Logic input swing is 0V ...

... Guaranteed by design. Crosstalk is defined as the glitch energy at any DAC output in response to a full-scale step change on any other DAC. Digital inputs at 2.4V; with digital inputs at CMOS levels, IDD decreases slightly. All input signals are specified with tR = tF ≤ 5ns. Logic input swing is 0V ...

MC33812, Multifunctional Ignition and Injector Driver

... other single/dual cylinder small engine control applications. The IC consists of three integrated low-side drivers, one pre-driver, a +5.0 V, voltage pre-regulator, an MCU watchdog circuit, an ISO 9141 K-Line interface, and a parallel interface for MCU communication. The three low-side drivers are p ...

... other single/dual cylinder small engine control applications. The IC consists of three integrated low-side drivers, one pre-driver, a +5.0 V, voltage pre-regulator, an MCU watchdog circuit, an ISO 9141 K-Line interface, and a parallel interface for MCU communication. The three low-side drivers are p ...

SE555Q - Diodes Incorporated

... Monostable operation is initiated when TRIG voltage falls below the trigger threshold. Once initiated, the sequence ends only if TRIG is high for at least 10μs before the end of the timing interval. When the trigger is grounded, the comparator storage time can be as long as 10μs, which limits the mi ...

... Monostable operation is initiated when TRIG voltage falls below the trigger threshold. Once initiated, the sequence ends only if TRIG is high for at least 10μs before the end of the timing interval. When the trigger is grounded, the comparator storage time can be as long as 10μs, which limits the mi ...

Analog Devices : Multiplier Application Guide

... Output Offset refers to the offset voltage at the output-amplifier stage. This is usually minimized at manufacture and can be trimmed where high accuracy is desired. Remember that the output offset will drift with temperature. Linearity error , or nonlinearity , is th e maximum difference between ac ...

... Output Offset refers to the offset voltage at the output-amplifier stage. This is usually minimized at manufacture and can be trimmed where high accuracy is desired. Remember that the output offset will drift with temperature. Linearity error , or nonlinearity , is th e maximum difference between ac ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.