HMC595 数据资料DataSheet下载

... at high incident power levels. The device can control signals from DC to 3 GHz and is especially suited for Cellular/3G infrastructure, WiMAX and WiBro applications with only 0.3 dB typical insertion loss. The design provides a 3 watt power handling and +65 dBm third order intercept at +8 Volt bias. ...

... at high incident power levels. The device can control signals from DC to 3 GHz and is especially suited for Cellular/3G infrastructure, WiMAX and WiBro applications with only 0.3 dB typical insertion loss. The design provides a 3 watt power handling and +65 dBm third order intercept at +8 Volt bias. ...

Minimum-energy sub-threshold self

... that the leakage energy contribution parts differ by a factor of µd + kcomoh , where µd is a parameter which denotes the average computation time of the asynchronous circuit and is in the range [0, 1], and kcomoh is the asynchronous communication overhead. This difference in the leakage energy part ...

... that the leakage energy contribution parts differ by a factor of µd + kcomoh , where µd is a parameter which denotes the average computation time of the asynchronous circuit and is in the range [0, 1], and kcomoh is the asynchronous communication overhead. This difference in the leakage energy part ...

LMC6482 - UTK-EECS

... Human body model, 1.5kΩ in series with 100pF. All pins rated per method 3015.6 of MIL-STD-883. This is a Class 1 device rating. Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings. Applies to both single-supply and split-supply operation ...

... Human body model, 1.5kΩ in series with 100pF. All pins rated per method 3015.6 of MIL-STD-883. This is a Class 1 device rating. Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings. Applies to both single-supply and split-supply operation ...

AD9260 数据手册DataSheet下载

... offers a complete single-chip 16-bit sampling ADC with a 2.5 MHz output data rate in a 44-lead MQFP. Selectable Internal Decimation Filtering—The AD9260 provides a high performance decimation filter with 0.004 dB pass-band ripple and 85 dB of stop-band attenuation. The filter is configurable with op ...

... offers a complete single-chip 16-bit sampling ADC with a 2.5 MHz output data rate in a 44-lead MQFP. Selectable Internal Decimation Filtering—The AD9260 provides a high performance decimation filter with 0.004 dB pass-band ripple and 85 dB of stop-band attenuation. The filter is configurable with op ...

TXS0206A SD Card Voltage-Translation

... Charged-device model (CDM), per JEDEC specification JESD22C101 (2) ...

... Charged-device model (CDM), per JEDEC specification JESD22C101 (2) ...

Papers - Department of Electrical Engineering

... the sizes of the corresponding capacitors can be reduced. Notice that the first integrator is the “fastest” in a feedforward design, while the first integrator is the “slowest” in the multiple-feedback modulator. Thus, the integrating capacitor of the first integrator in a feedforward loop filter wi ...

... the sizes of the corresponding capacitors can be reduced. Notice that the first integrator is the “fastest” in a feedforward design, while the first integrator is the “slowest” in the multiple-feedback modulator. Thus, the integrating capacitor of the first integrator in a feedforward loop filter wi ...

LT1204 - 4-Input Video Multiplexer with 75MHz Current Feedback Amplifier

... peaking can be tolerated, larger bandwidths can be obtained by lowering the feedback resistor. For gains of 2 or less, the 0.1dB bandwidth is greater than 30MHz for all loads and supply voltages. At high gains (low values of RG) the disabled output resistance drops slightly due to loading of the int ...

... peaking can be tolerated, larger bandwidths can be obtained by lowering the feedback resistor. For gains of 2 or less, the 0.1dB bandwidth is greater than 30MHz for all loads and supply voltages. At high gains (low values of RG) the disabled output resistance drops slightly due to loading of the int ...

$doc.title

... The cost of this fixture ranges from 550 per fixture, dedicated to a 20-pin device in quantities of 1-10, to as low as 385 per fixture of the same type in quantities over 100. This is not substantially higher than the cost of a dedicated fixture; which is estimated at 200- 500. The factor to conside ...

... The cost of this fixture ranges from 550 per fixture, dedicated to a 20-pin device in quantities of 1-10, to as low as 385 per fixture of the same type in quantities over 100. This is not substantially higher than the cost of a dedicated fixture; which is estimated at 200- 500. The factor to conside ...

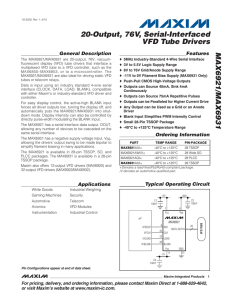

MAX6921/MAX6931 20-Output, 76V, Serial-Interfaced VFD Tube Drivers General Description

... three inputs (DIN, CLK, LOAD) and a data output (DOUT, MAX6921 only). This interface is used to write output data to the MAX6921/MAX6931 (Figure 4) (Table 1). The serial interface data word length is 20 bits, D0–D19. The functions of the four serial interface pins are: • CLK input is the interface c ...

... three inputs (DIN, CLK, LOAD) and a data output (DOUT, MAX6921 only). This interface is used to write output data to the MAX6921/MAX6931 (Figure 4) (Table 1). The serial interface data word length is 20 bits, D0–D19. The functions of the four serial interface pins are: • CLK input is the interface c ...

Datasheet

... The waveform on this node is a copy of the internal oscillator. It can be used for synchronisation purposes between various PWM controllers. When the internal clock is low, SW is pulled down to approximately a forward diode voltage. An external RC must be connected on this node in order to generate ...

... The waveform on this node is a copy of the internal oscillator. It can be used for synchronisation purposes between various PWM controllers. When the internal clock is low, SW is pulled down to approximately a forward diode voltage. An external RC must be connected on this node in order to generate ...

sn74lvcc3245a.pdf

... B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators ...

... B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators ...

RT FLOW RATE TOTALISER - Southeastern Automation

... AC or DC powering & Remote switches (remote keys) ...

... AC or DC powering & Remote switches (remote keys) ...

TAS5111A 数据资料 dataSheet 下载

... necessary. The RESET must be asserted LOW before the valid PWM signal is removed. When TI TDAA modulators are used with TI TDAA back ends, the correct timing control of RESET and PWM_xP is performed by the modulator. ...

... necessary. The RESET must be asserted LOW before the valid PWM signal is removed. When TI TDAA modulators are used with TI TDAA back ends, the correct timing control of RESET and PWM_xP is performed by the modulator. ...

Clock Tree 101 - Timing Basics

... § Clock Generators – an integrated circuit that different applications, the most common timing uses a reference clock or crystal to generate components are: multiple output clocks at one or multiple frequencies;; § Crystals – a piece of quartz or other mater ...

... § Clock Generators – an integrated circuit that different applications, the most common timing uses a reference clock or crystal to generate components are: multiple output clocks at one or multiple frequencies;; § Crystals – a piece of quartz or other mater ...

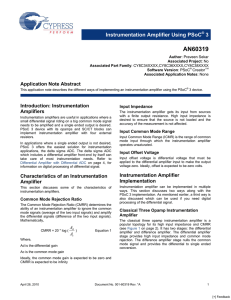

5 8 1 1 9 4 2 BOOST INSTRUMENT AMP CMR WITH COMMON

... does not change. Therefore the voltage across RG remains constant and, since no current flows in the op amp inputs, there is no current change in RFB1 or RFB2, and the differential output voltage, V1-V2, does not change. Ideally then, with a perfect difference amplifier, the common-mode gain is zero ...

... does not change. Therefore the voltage across RG remains constant and, since no current flows in the op amp inputs, there is no current change in RFB1 or RFB2, and the differential output voltage, V1-V2, does not change. Ideally then, with a perfect difference amplifier, the common-mode gain is zero ...

LT6600-2.5

... Similarly, the voltages VOUT+ and VOUT– appearing at Pins 4 and 5 of the LT6600-2.5 are the filter outputs. The difference between VOUT+ and VOUT– is the differential output voltage. The average of VOUT+ and VOUT– is the common mode output voltage. ...

... Similarly, the voltages VOUT+ and VOUT– appearing at Pins 4 and 5 of the LT6600-2.5 are the filter outputs. The difference between VOUT+ and VOUT– is the differential output voltage. The average of VOUT+ and VOUT– is the common mode output voltage. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.