MS Word format

... computer. If the cable is secure, try pressing the black button on the back of the radio to toggle between “Normal” and “Crossover” modes (this button should be in the Normal position). If this fails, reboot the computer, replace the Ethernet cable with a new one, and press the black button if neces ...

... computer. If the cable is secure, try pressing the black button on the back of the radio to toggle between “Normal” and “Crossover” modes (this button should be in the Normal position). If this fails, reboot the computer, replace the Ethernet cable with a new one, and press the black button if neces ...

ADIML RIT Analog Circuitry - Edge - Rochester Institute of Technology

... VI which makes setting parameters easy (top level module performs no protocol or bit setting operations) Easy interface with Dynamic Signal Analyzer and 6501 USB DAQ ...

... VI which makes setting parameters easy (top level module performs no protocol or bit setting operations) Easy interface with Dynamic Signal Analyzer and 6501 USB DAQ ...

WPS-445124-02

... ground continuity between the top layer and bottom ground planes. Mounting holes near the unit will help secure the board to the chassis, minimize ground current loops and improve thermal conductivity in case the board is not soldered to the chassis. Quarter-wave stubs at the gate and drain for bias ...

... ground continuity between the top layer and bottom ground planes. Mounting holes near the unit will help secure the board to the chassis, minimize ground current loops and improve thermal conductivity in case the board is not soldered to the chassis. Quarter-wave stubs at the gate and drain for bias ...

AD7836 数据手册DataSheet 下载

... Level-Triggered Chip Select Input (active low). The device is selected when this input is low. Parallel Data Inputs. The AD7836 can accept a straight 14-bit parallel word on DB0 to DB13 where DB13 is the MSB and DB0 is the LSB. Address inputs. A0, A1 and A2 are decoded to select one of the five inpu ...

... Level-Triggered Chip Select Input (active low). The device is selected when this input is low. Parallel Data Inputs. The AD7836 can accept a straight 14-bit parallel word on DB0 to DB13 where DB13 is the MSB and DB0 is the LSB. Address inputs. A0, A1 and A2 are decoded to select one of the five inpu ...

MAX3524 Low-Noise, High-Linearity Broadband Amplifier General Description

... The LNA input is single-ended. The RF input signal is coupled to RFIN through a DC blocking capacitor. The LNA outputs drive a differential load, such as a mixer, through DC blocking capacitors. The equivalent input LNA impedance is 330Ω resistive in parallel with 1.8pf, as shown in Figure 2. The ap ...

... The LNA input is single-ended. The RF input signal is coupled to RFIN through a DC blocking capacitor. The LNA outputs drive a differential load, such as a mixer, through DC blocking capacitors. The equivalent input LNA impedance is 330Ω resistive in parallel with 1.8pf, as shown in Figure 2. The ap ...

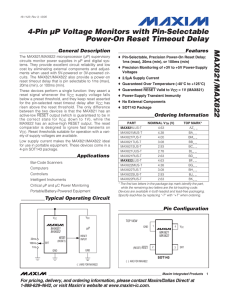

MAX821/MAX822 4-Pin µP Voltage Monitors with Pin-Selectable Power-On Reset Timeout Delay General Description

... Negative-Going VCC Transients While designed to issue a reset to the microprocessor (µP) during power-up, power-down, and brownout conditions, the MAX821/MAX822 are relatively immune to short-duration, negative-going VCC transients (glitches). Figure 1 shows the maximum transient duration vs. reset ...

... Negative-Going VCC Transients While designed to issue a reset to the microprocessor (µP) during power-up, power-down, and brownout conditions, the MAX821/MAX822 are relatively immune to short-duration, negative-going VCC transients (glitches). Figure 1 shows the maximum transient duration vs. reset ...

lab1

... from the Fairchild library of devices (Fairchild.olb). For PMOS, make sure that the bulk is connected to Source (VDD). 2 Using time-domain analysis in the PSPICE program, determine the gain of the CMOS amplifier. Use the following setting: Run to Time=5m; Maximum step size=1u. 3 Determine if Vin and ...

... from the Fairchild library of devices (Fairchild.olb). For PMOS, make sure that the bulk is connected to Source (VDD). 2 Using time-domain analysis in the PSPICE program, determine the gain of the CMOS amplifier. Use the following setting: Run to Time=5m; Maximum step size=1u. 3 Determine if Vin and ...

Campbell - Microelectronics Research and Communications

... function of these parameters. How well does the resistance state get retained during operation as a ‘resistor’ in a circuit? Quite often, due to the nature of the amorphous materials, the resistance values have a large spread. This overlap prevents reliable use of multistate programming with the ...

... function of these parameters. How well does the resistance state get retained during operation as a ‘resistor’ in a circuit? Quite often, due to the nature of the amorphous materials, the resistance values have a large spread. This overlap prevents reliable use of multistate programming with the ...

Op amps explained - Experimentalists Anonymous

... connected to a common point. Connect the output of the function generator to channel A of the oscilloscope and to the input of the follower. Connect the output of the filter (junction of C and R) to channel B of the oscilloscope. Set channel A and B on the oscilloscope to the same frequency and volt ...

... connected to a common point. Connect the output of the function generator to channel A of the oscilloscope and to the input of the follower. Connect the output of the filter (junction of C and R) to channel B of the oscilloscope. Set channel A and B on the oscilloscope to the same frequency and volt ...

A Simple Bar Graph Pressure Display

... arrangement of 6 green, 2 yellow, and 2 red LEDs, which can serve as an early warning of excessive filter degradation. Amplifier Design: The dual op amp shown in Figure 2 was chosen because it operates well in applications where the common-mode input is near ground. It also features operation from a ...

... arrangement of 6 green, 2 yellow, and 2 red LEDs, which can serve as an early warning of excessive filter degradation. Amplifier Design: The dual op amp shown in Figure 2 was chosen because it operates well in applications where the common-mode input is near ground. It also features operation from a ...

CMOS Eight-Transistor Memory Cell for Low-Power High

... S3.incoroprated released the commercial product SAVAGEXP [25] in year 2000 based on a 0.18 µm TSMC single-poly and six layer of metal CMOS technology [24] which operated at clock cycle of 200 MHz. All different geometries of embedded memories within the product are laid out based on single-poly and ...

... S3.incoroprated released the commercial product SAVAGEXP [25] in year 2000 based on a 0.18 µm TSMC single-poly and six layer of metal CMOS technology [24] which operated at clock cycle of 200 MHz. All different geometries of embedded memories within the product are laid out based on single-poly and ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331

... achieved by varying the duty cycle of the electronic switch keeping the frequency of operation constant (F. L. Luo, 1999, F. L. Luo, 1998, F. L. Luo, 1999, F. L. Luo, 2000, S. P. Natarajan, 2013). These converters in general have complex non-linear models with parameter variation problems. PI contro ...

... achieved by varying the duty cycle of the electronic switch keeping the frequency of operation constant (F. L. Luo, 1999, F. L. Luo, 1998, F. L. Luo, 1999, F. L. Luo, 2000, S. P. Natarajan, 2013). These converters in general have complex non-linear models with parameter variation problems. PI contro ...

AD5821A 数据手册DataSheet 下载

... DAC at data rates of up to 400 kHz. After a read operation, the contents of the input register are reset to all 0s. An I2C bus operates with one or more master devices that generate the serial clock (SCL) and read and write data on the serial data line (SDA) to and from slave devices such as the AD5 ...

... DAC at data rates of up to 400 kHz. After a read operation, the contents of the input register are reset to all 0s. An I2C bus operates with one or more master devices that generate the serial clock (SCL) and read and write data on the serial data line (SDA) to and from slave devices such as the AD5 ...

T M P

... The laboratory transformer, shown below, has two primary windings (terminals 1-2 and 3-4) and a single winding for the secondary (terminals 5-7) with a center tap (terminal 6). The taps allow the user to operate the transformer with two different primary voltages. The lower primary terminals 3 and 4 ...

... The laboratory transformer, shown below, has two primary windings (terminals 1-2 and 3-4) and a single winding for the secondary (terminals 5-7) with a center tap (terminal 6). The taps allow the user to operate the transformer with two different primary voltages. The lower primary terminals 3 and 4 ...

MAX3815.pdf

... A squelching function can be created by sending the CLKLOS output through an inverter to the OUTON pin. This will squelch the CML outputs whenever the clock signal is removed. A loss-of-signal LED indicator can be incorporated into the circuit as well (see Figure 3). ...

... A squelching function can be created by sending the CLKLOS output through an inverter to the OUTON pin. This will squelch the CML outputs whenever the clock signal is removed. A loss-of-signal LED indicator can be incorporated into the circuit as well (see Figure 3). ...

OP177 Ultraprecision Operational Amplifier

... different output voltages. This nonlinearity causes errors in high closed-loop gain circuits. ...

... different output voltages. This nonlinearity causes errors in high closed-loop gain circuits. ...

A Web-Based Platform for Experimental Investigation of Electric

... Common Gateway Interface ŽCGI. is a very popular standard protocol for communication between a web server and an external program, typically referred to as a CGI program. The primary role of a CGI program is to dynamically create data on demand, such as a web page or image, for the web server to ret ...

... Common Gateway Interface ŽCGI. is a very popular standard protocol for communication between a web server and an external program, typically referred to as a CGI program. The primary role of a CGI program is to dynamically create data on demand, such as a web page or image, for the web server to ret ...

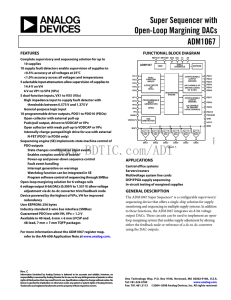

ADM1067 数据手册DataSheet 下载

... sequencing device that offers a single-chip solution for supply monitoring and sequencing in multiple supply systems. In addition to these functions, the ADM1067 integrates six 8-bit voltage output DACs. These circuits can be used to implement an openloop margining system that enables supply adjustm ...

... sequencing device that offers a single-chip solution for supply monitoring and sequencing in multiple supply systems. In addition to these functions, the ADM1067 integrates six 8-bit voltage output DACs. These circuits can be used to implement an openloop margining system that enables supply adjustm ...