* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download lab1

Electrical ballast wikipedia , lookup

Immunity-aware programming wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power inverter wikipedia , lookup

Electrical substation wikipedia , lookup

Negative feedback wikipedia , lookup

Public address system wikipedia , lookup

Three-phase electric power wikipedia , lookup

Audio power wikipedia , lookup

Switched-mode power supply wikipedia , lookup

History of the transistor wikipedia , lookup

Surge protector wikipedia , lookup

Stray voltage wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage optimisation wikipedia , lookup

Alternating current wikipedia , lookup

Current source wikipedia , lookup

Buck converter wikipedia , lookup

Mains electricity wikipedia , lookup

Regenerative circuit wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Two-port network wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Rectiverter wikipedia , lookup

Opto-isolator wikipedia , lookup

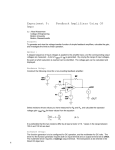

Simulation – 1 MOSFET current mirror and CMOS amplifier (Simulation) 1. 2. OBJECTIVES Simulate a current mirror. Simulate a CMOS amplifier. Simulation of PMOS current mirror We would like to analyze the circuit given in Fig. 1. This circuit consists of two PMOS transistors in which one of them is in saturation. It is important that other remains in the saturation region for this mirror to work. IRF9140 PMOS Iref R 10k IRF9140 VDD 15Vdc PMOS Iout RL 1k Fig. 1 Assemble the circuit below using PSPICE. The PMOS transistor can be found in EVALAA.olb library. IRF9140 is listed there. Using bias-point analyses determine Iref and Iout. You would notice that Iout is very close to Iref. 1 Now increase RL so that Iout decreases by a factor of 3 or more. Try to figure out why the current mirror stopped working. Note that the threshold voltage for the PMOS transistor is -3.387 V. 3. Simulation of a CMOS amplifier- The schematic shown in Fig. 2 works as a CMOS amplifier when properly biased. Here, you would recall that in the language of PSPICE, VOFF stands for offset DC voltage and VAMPL is the amplitude of AC voltage that rides the DC voltage. 1 PMOS NDC652P/FAI 5Vdc VOFF = 2.378V VAMPL = 1m VDD V Vin FREQ = 1k NDC651N/FAI NMOS AC = 0 0 Fig. 2 Fig. 2 It is not difficult to understand why it amplifies an input signal (Vin) when proper biasing is provided. In fact this circuit is none other than a logic inverter. Figure 3 shows the transfer characteristics for the CMOS amplifier. The gain of the amplifier is defined as 𝐺𝑎𝑖𝑛 = ∆𝑉𝑜𝑢𝑡 ∆𝑉𝑖𝑛 As you can see in Fig. 3, for a given ∆Vin the value of ∆Vout is quite large provided the right region in the transfer characteristic (i.e. operating point) is chosen. Hence we have amplification. Transfer characteristic for CMOS amplifier Vout ∆Vout ∆Vin Vin Fig. 3 Using PSPICE, assemble the schematic given in Fig. 2. Here, Vin and VDD are available in the SOURCE library. Vin is VSIN of the SOURCE library. The value of the parameter VOFF has been 2 carefully chosen to get a decent amplification. The transistors NMOS and PMOS are obtained from the Fairchild library of devices (Fairchild.olb). For PMOS, make sure that the bulk is connected to Source (VDD). 2 Using time-domain analysis in the PSPICE program, determine the gain of the CMOS amplifier. Use the following setting: Run to Time=5m; Maximum step size=1u. 3 Determine if Vin and Vout are in phase or out of phase. 4 Change the biasing voltage (VOFF) by 10 mV and observe the change in the gain. 3