Data Sheet

... voltages above about 6V. The current in this zener must be limited to less than 100 µA. A resistor of 470 kΩ will limit the current to a safe value for input voltages as high 42V. Smaller values of resistor can be used at lower input voltages. The LM22677 also incorporates an input under voltage loc ...

... voltages above about 6V. The current in this zener must be limited to less than 100 µA. A resistor of 470 kΩ will limit the current to a safe value for input voltages as high 42V. Smaller values of resistor can be used at lower input voltages. The LM22677 also incorporates an input under voltage loc ...

Power-Conscious Design of the Cell Processor`s Synergistic

... increased to have more drive capability. When the target speed is not aggressive, the static implementation clearly uses less power than the dynamic implementation. However, when the target speed becomes more aggressive, the static implementation seems to hit a speed wall. The transistors in static ...

... increased to have more drive capability. When the target speed is not aggressive, the static implementation clearly uses less power than the dynamic implementation. However, when the target speed becomes more aggressive, the static implementation seems to hit a speed wall. The transistors in static ...

MAX1858 Dual 180° Out-of-Phase PWM Step-Down Controller with Power Sequencing and POR

... 18V and supports loads of 10A or higher. Input voltage ripple and total RMS input ripple current are reduced by synchronized 180° out-of-phase operation. The switching frequency is adjustable from 100kHz to 600kHz with an external resistor. Alternatively, the controller can be synchronized to an ext ...

... 18V and supports loads of 10A or higher. Input voltage ripple and total RMS input ripple current are reduced by synchronized 180° out-of-phase operation. The switching frequency is adjustable from 100kHz to 600kHz with an external resistor. Alternatively, the controller can be synchronized to an ext ...

Teaching Computer Control using Cause and Effect Relationships

... the student will change the voltage settings and the time settings. He/she will print, if poshow to set voltage and time before trying to use the tool to capture patterns. It is frustrating to sible, the patterns captured. Looking at the pattern with the student will give you the opportunity to gu ...

... the student will change the voltage settings and the time settings. He/she will print, if poshow to set voltage and time before trying to use the tool to capture patterns. It is frustrating to sible, the patterns captured. Looking at the pattern with the student will give you the opportunity to gu ...

FEATURES DESCRIPTION D

... Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported. (2) Input terminals are diode-clamped to the power-supply rails ...

... Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported. (2) Input terminals are diode-clamped to the power-supply rails ...

A Tutorial on Calculating Source Impedance Ratios

... For an overcurrent relay, when the SIR is high, the faulted circuit is dominated by the source impedance. The difference between the fault current magnitude for an in-zone fault and an out-of-zone fault can be smaller than the typical margins used for setting the pickup. For example, if we calculate ...

... For an overcurrent relay, when the SIR is high, the faulted circuit is dominated by the source impedance. The difference between the fault current magnitude for an in-zone fault and an out-of-zone fault can be smaller than the typical margins used for setting the pickup. For example, if we calculate ...

Ingeniería e Investigación Template - Revistas UNAL

... distribution systems in Colombian, have circuits, which are designed to operate at this voltage level. These are used to supply small towns and medium industries. A single line layout of this system is shown in figure 3. ...

... distribution systems in Colombian, have circuits, which are designed to operate at this voltage level. These are used to supply small towns and medium industries. A single line layout of this system is shown in figure 3. ...

LM25061 Positive Low Voltage Power Limiting Hot Swap Controller

... backplane or other "hot" power source, thereby limiting the voltage sag on the backplane’s supply voltage, and the dV/dt of the voltage applied to the load. Effects on other circuits in the system are minimized, preventing possible unintended resets. A controlled shutdown when the circuit card is re ...

... backplane or other "hot" power source, thereby limiting the voltage sag on the backplane’s supply voltage, and the dV/dt of the voltage applied to the load. Effects on other circuits in the system are minimized, preventing possible unintended resets. A controlled shutdown when the circuit card is re ...

Solution

... factors of 0.8 lagging, 1.0, and 0.8 leading. These calculations are done using an equivalent circuit referred to the primary side. ...

... factors of 0.8 lagging, 1.0, and 0.8 leading. These calculations are done using an equivalent circuit referred to the primary side. ...

How Do I Derate Three Phase Inputs For Single

... your application. The following are some basic guidelines to help you in determining whether or not your Variable Frequency Drive (VFD) is suitable for your application: Gather motor nameplate data including horsepower (HP), current (Amps), motor voltage, input line voltage and power source phase. D ...

... your application. The following are some basic guidelines to help you in determining whether or not your Variable Frequency Drive (VFD) is suitable for your application: Gather motor nameplate data including horsepower (HP), current (Amps), motor voltage, input line voltage and power source phase. D ...

Unit I

... Question No. 1 should be compulsory and cover the entire syllabus. This question should have objective or short answer type questions. It should be of 25 marks. Every unit should have two questions. However, student may be asked to attempt only 1 question from each unit. Each question should be 12.5 ...

... Question No. 1 should be compulsory and cover the entire syllabus. This question should have objective or short answer type questions. It should be of 25 marks. Every unit should have two questions. However, student may be asked to attempt only 1 question from each unit. Each question should be 12.5 ...

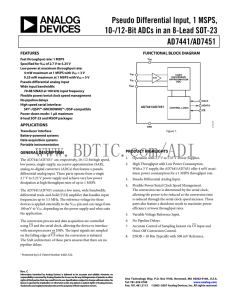

AD7441 数据手册DataSheet下载

... the application. The conversion process and data acquisition are controlled using CS and the serial clock, allowing the device to interface with microprocessors or DSPs. The input signals are sampled on the falling edge of CS when the conversion is initiated. The SAR architecture of these parts ensu ...

... the application. The conversion process and data acquisition are controlled using CS and the serial clock, allowing the device to interface with microprocessors or DSPs. The input signals are sampled on the falling edge of CS when the conversion is initiated. The SAR architecture of these parts ensu ...

ABCs of ADCs - Analog-to-Digital Converter Basics

... zero (000). As the input voltage increases towards VREF/8, the error also increases because the input is no longer zero, but the output code remains at zero because a range of input voltages is represented by a single output code. When the input reaches VREF/8, the output code changes from 000 to 00 ...

... zero (000). As the input voltage increases towards VREF/8, the error also increases because the input is no longer zero, but the output code remains at zero because a range of input voltages is represented by a single output code. When the input reaches VREF/8, the output code changes from 000 to 00 ...

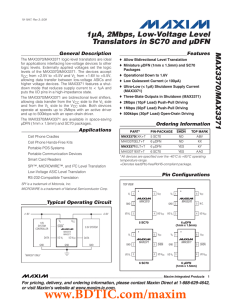

MAX3370 1µA, 2Mbps, Low-Voltage Level Translators in SC70 and µDFN General Description

... To reduce ripple and the chance of transmitting incorrect data, decouple VCC and VL to ground with a 0.1µF capacitor as close to the device as possible. ...

... To reduce ripple and the chance of transmitting incorrect data, decouple VCC and VL to ground with a 0.1µF capacitor as close to the device as possible. ...

35% Wiring

... We can nullify effects of variation and even speedup The performance loss due to fuzzy logic is minimal ...

... We can nullify effects of variation and even speedup The performance loss due to fuzzy logic is minimal ...

Inclass demo of Norton EC

... If not sure about dependent or independent sources, then for both Thevenin and Norton (a 1st or b 1st OK): a. find open circuit voltage VOC: the voltage across the 2 points of interest. Use KVL, NVM or MCM; NVM tends to give voltage directly, (which might be a bit more convenient, but depending on t ...

... If not sure about dependent or independent sources, then for both Thevenin and Norton (a 1st or b 1st OK): a. find open circuit voltage VOC: the voltage across the 2 points of interest. Use KVL, NVM or MCM; NVM tends to give voltage directly, (which might be a bit more convenient, but depending on t ...

Singing Tesla Coil: Building a Musically

... In 1891, Nikola Tesla invented one of his most famous devices, the Tesla coil. To be fair, electrical coils existed before Nikola Tesla. Ruhmkorff coils, named after Heinrich Ruhmkorff and designed by Nicholas Callan in 1836, converted low voltage DC to high voltage DC spikes. [9] Tesla began workin ...

... In 1891, Nikola Tesla invented one of his most famous devices, the Tesla coil. To be fair, electrical coils existed before Nikola Tesla. Ruhmkorff coils, named after Heinrich Ruhmkorff and designed by Nicholas Callan in 1836, converted low voltage DC to high voltage DC spikes. [9] Tesla began workin ...

A CMOS Low-Dropout Regulator With Current

... overall LDO stability is guaranteed for all load and feedback conditions. The unity-gain frequency of a typical LDO is limited by the parasitic pole generated by the output impedance of the error amplifier and gate capacitance of the regulation FET. This pole can be pushed to a higher frequency by u ...

... overall LDO stability is guaranteed for all load and feedback conditions. The unity-gain frequency of a typical LDO is limited by the parasitic pole generated by the output impedance of the error amplifier and gate capacitance of the regulation FET. This pole can be pushed to a higher frequency by u ...

living with the lab

... seconds due to a sudden addition of salty water. • At about 30 seconds, the salinity values stabilize (with continued random error at the new salinity level). • For this example, the deadtime compensation would be set to 12 seconds (30s - 18s). • This means that you would want to allow 12 seconds be ...

... seconds due to a sudden addition of salty water. • At about 30 seconds, the salinity values stabilize (with continued random error at the new salinity level). • For this example, the deadtime compensation would be set to 12 seconds (30s - 18s). • This means that you would want to allow 12 seconds be ...

ADVANTAGES DESCRIPTION

... The 73S8024RN smart card interface IC incorporates a LDO voltage regulator. The voltage output is controlled by the digital input 5V/#V. This regulator is able to provide either 3V or 5V card voltage from the power supply applied on the VPC pin. Digital circuitry is powered by the power supply appli ...

... The 73S8024RN smart card interface IC incorporates a LDO voltage regulator. The voltage output is controlled by the digital input 5V/#V. This regulator is able to provide either 3V or 5V card voltage from the power supply applied on the VPC pin. Digital circuitry is powered by the power supply appli ...