ORIGA™ SLE95051 Product Brief

... superior cryptography and functionality at reduced system cost compared to other solutions. It is based on Infineon’s long standing experience and market leadership in security solutions. It offers a cost effective level of physical hardware security, e.g. versus bus probing and memory analysis atta ...

... superior cryptography and functionality at reduced system cost compared to other solutions. It is based on Infineon’s long standing experience and market leadership in security solutions. It offers a cost effective level of physical hardware security, e.g. versus bus probing and memory analysis atta ...

1. Introduction - About the journal

... passive elements by utilizing modern functional block which internal chip structure performs several mathematical operations simultaneously. Moreover we are not restricted only to the commercially available devices but there are hypothetical as well [20]. Among all these active elements we prefer de ...

... passive elements by utilizing modern functional block which internal chip structure performs several mathematical operations simultaneously. Moreover we are not restricted only to the commercially available devices but there are hypothetical as well [20]. Among all these active elements we prefer de ...

Design Pittfalls and Fixes

... Overvoltage High voltages can damage transistors – Electrostatic discharge – Oxide arcing – Punchthrough – Time-dependent dielectric breakdown (TDDB) • Accumulated wear from tunneling currents Requires low VDD for thin oxides and short channels Use ESD protection structures where chip meets r ...

... Overvoltage High voltages can damage transistors – Electrostatic discharge – Oxide arcing – Punchthrough – Time-dependent dielectric breakdown (TDDB) • Accumulated wear from tunneling currents Requires low VDD for thin oxides and short channels Use ESD protection structures where chip meets r ...

10-bit, 125 MS/s, 40 mW Pipelined ADC in 0.18 μm CMOS

... This configuration relaxes the bandwidth requirement of the amplifiers without increasing their number, which further reduces the amplifier power consumption. Figure 8 shows the configuration and timing chart of the double-sampling FADAC. The sample phase and comparison phase of one network occur du ...

... This configuration relaxes the bandwidth requirement of the amplifiers without increasing their number, which further reduces the amplifier power consumption. Figure 8 shows the configuration and timing chart of the double-sampling FADAC. The sample phase and comparison phase of one network occur du ...

e-scooter battery state of charge estimation using arduino mega

... At last, because of the individuals who have contributed straightforwardly or in a roundabout way to the accomplishment of this venture whom I have not specified their name particularly. Without them, this undertaking would not successful ...

... At last, because of the individuals who have contributed straightforwardly or in a roundabout way to the accomplishment of this venture whom I have not specified their name particularly. Without them, this undertaking would not successful ...

A Frequency Compensation Scheme for LDO Voltage Regulators

... OWER management is a very important issue in portable electronic applications. The need for multiple on-chip voltage levels makes voltage regulators a critical part of an electronic system design. Portable electronic devices like cell phones require very efficient power management to increase the ba ...

... OWER management is a very important issue in portable electronic applications. The need for multiple on-chip voltage levels makes voltage regulators a critical part of an electronic system design. Portable electronic devices like cell phones require very efficient power management to increase the ba ...

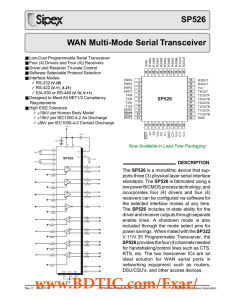

SP526 数据资料DataSheet下载

... characteristics will change to support the required signal levels. The mode of each driver in the different interface modes that can be selected is shown in Table 1. ...

... characteristics will change to support the required signal levels. The mode of each driver in the different interface modes that can be selected is shown in Table 1. ...

NCP1608 Critical Conduction Mode PFC Controller Utilizing a Transconductance Error

... pre-converters to comply with line current harmonic regulations. This controller operates in critical conduction mode (CrM) suitable for applications up to 350 W. Its voltage mode scheme enables it to obtain near unity power factor without the need for a line-sensing network. A high precision transc ...

... pre-converters to comply with line current harmonic regulations. This controller operates in critical conduction mode (CrM) suitable for applications up to 350 W. Its voltage mode scheme enables it to obtain near unity power factor without the need for a line-sensing network. A high precision transc ...

Noise - Massachusetts Institute of Technology

... channel bandwidth is 1 MHz, and the minimum SNR at the receiver output is 12 dB to achieve a BER of 1e-3 ...

... channel bandwidth is 1 MHz, and the minimum SNR at the receiver output is 12 dB to achieve a BER of 1e-3 ...

MAX4854H/MAX4854HL Quad SPST, High-Bandwidth, Signal Line Protection Switch General Description

... These devices feature overvoltage protection by putting the switch into high-impedance mode when the switch input exceeds VCC. These switches have low 27.5pF on-channel capacitance, which allows for 12Mbps switching of the data signals for USB 2.0 full speed/1.1 applications. The MAX4854H/MAX4854HL ...

... These devices feature overvoltage protection by putting the switch into high-impedance mode when the switch input exceeds VCC. These switches have low 27.5pF on-channel capacitance, which allows for 12Mbps switching of the data signals for USB 2.0 full speed/1.1 applications. The MAX4854H/MAX4854HL ...

Model Paper for LACCEI Proceedings

... The design of electronic systems is becoming highly complex given the integrated nature of these systems. The use of a top-down design methodology is highly prevalent among designers given the availability of a diverse set of system level design tools. Such design tools include VHDL, Verilog, or Sys ...

... The design of electronic systems is becoming highly complex given the integrated nature of these systems. The use of a top-down design methodology is highly prevalent among designers given the availability of a diverse set of system level design tools. Such design tools include VHDL, Verilog, or Sys ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331,

... 2) State II: During this state the switches, Sm2 and Sc1 are turned on, Sm1 and Sc2 are turned off, and the current iγis positive. The boost inductor and input dc source transfer energy to the CW voltage multiplier through different even diodes as described below. 2.a) In state II-a, D6 is conductin ...

... 2) State II: During this state the switches, Sm2 and Sc1 are turned on, Sm1 and Sc2 are turned off, and the current iγis positive. The boost inductor and input dc source transfer energy to the CW voltage multiplier through different even diodes as described below. 2.a) In state II-a, D6 is conductin ...

1) Damped Sinusoids (25 points)

... There is another answer to this question. If you assumed that the output of the first opamp could put out -15 (or anything from -15 to -13), and used the gain of the second opamp, (-10k/20k), to predict that the circuit could deliver a maximum of 7.5 volts at the output, then this is right too. b. T ...

... There is another answer to this question. If you assumed that the output of the first opamp could put out -15 (or anything from -15 to -13), and used the gain of the second opamp, (-10k/20k), to predict that the circuit could deliver a maximum of 7.5 volts at the output, then this is right too. b. T ...

V(t)

... So, the current peaks ahead in time (earlier) of the voltage There is a difference in phase of /2 (900) why? When there is not much charge on the capacitor it readily accepts more and current easily flows. However, the E-field and potential between the plates increase and consequently it becomes mo ...

... So, the current peaks ahead in time (earlier) of the voltage There is a difference in phase of /2 (900) why? When there is not much charge on the capacitor it readily accepts more and current easily flows. However, the E-field and potential between the plates increase and consequently it becomes mo ...

MAX1894/MAX1924 Advanced Li+ Battery-Pack Protectors General Description Features

... MOSFETs are connected in a common-source configuration that does not require external pullup resistors. The MAX1894/MAX1924 use only one current-sense resistor to achieve the protection features. All protection thresholds and delays do not require any external components and are trimmed at the facto ...

... MOSFETs are connected in a common-source configuration that does not require external pullup resistors. The MAX1894/MAX1924 use only one current-sense resistor to achieve the protection features. All protection thresholds and delays do not require any external components and are trimmed at the facto ...

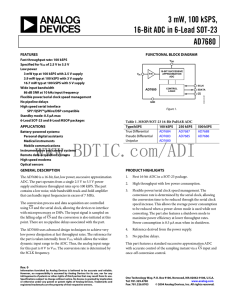

3 mW, 100 kSPS, 16-Bit ADC in 6-Lead SOT-23 AD7680

... SCLK to data valid hold time SCLK falling edge to SDATA high impedance Power up time from full power-down ...

... SCLK to data valid hold time SCLK falling edge to SDATA high impedance Power up time from full power-down ...