Si9185 Micropower 500 mA CMOS LDO Regulator with Error Flag

... guaranteed to be on when the SD pin voltage equals or is greater than 1.5 V. VOUT is guaranteed to be off when the SD pin voltage equals or is less than 0.4 V. During shutdown mode, the Si9185 will draw less than 2 µA current from the source. To automatically turn on VOUT whenever the input is appli ...

... guaranteed to be on when the SD pin voltage equals or is greater than 1.5 V. VOUT is guaranteed to be off when the SD pin voltage equals or is less than 0.4 V. During shutdown mode, the Si9185 will draw less than 2 µA current from the source. To automatically turn on VOUT whenever the input is appli ...

G. H. RAISONI COLLEGE OF ENGINEERING, NAGPUR Department

... Theory: Digital circuits are different from analog circuits. Almost all digital circuits are designed for two state operations. This means using only two non-adjacent points on the load line, typically saturation and cutoff. As a result the output voltage has only two states, either low or high. Thu ...

... Theory: Digital circuits are different from analog circuits. Almost all digital circuits are designed for two state operations. This means using only two non-adjacent points on the load line, typically saturation and cutoff. As a result the output voltage has only two states, either low or high. Thu ...

Chapter 2: Fundamentals of Sampled Data Systems

... referred to "ground," either occurring at the outputs of logic gates, or applied to their inputs. The digital numbers used are all basically binary; that is, each "bit," or unit of information has one of two possible states. These states are "off," "false," or "0," and "on," "true," or "1." It is al ...

... referred to "ground," either occurring at the outputs of logic gates, or applied to their inputs. The digital numbers used are all basically binary; that is, each "bit," or unit of information has one of two possible states. These states are "off," "false," or "0," and "on," "true," or "1." It is al ...

STWD100

... If the EN goes high after power-up in less than tWD from the moment that VCC exceeds the timer startup voltage, VSTART, the WDO will stay high for the same time period as EN, plus tWD (see Figure 10). If the EN goes high anytime during normal operation, the WDO will go high as well, but the minimum ...

... If the EN goes high after power-up in less than tWD from the moment that VCC exceeds the timer startup voltage, VSTART, the WDO will stay high for the same time period as EN, plus tWD (see Figure 10). If the EN goes high anytime during normal operation, the WDO will go high as well, but the minimum ...

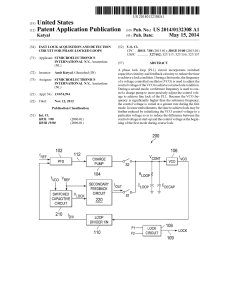

fvco VREF

... frequency-to -voltage converter circuit) in combination with a secondary feedback circuit 220 (also referred to herein as a ...

... frequency-to -voltage converter circuit) in combination with a secondary feedback circuit 220 (also referred to herein as a ...

BD00GA3MEFJ-LB

... ・Input capacitor CIN of VCC (VIN) should be placed very close to VCC(VIN) pin as possible, and used broad wiring pattern. Output capacitor COUT also should be placed close to IC pin as possible. In case connected to inner layer GND plane, please use several through hole. ・FB pin has comparatively hi ...

... ・Input capacitor CIN of VCC (VIN) should be placed very close to VCC(VIN) pin as possible, and used broad wiring pattern. Output capacitor COUT also should be placed close to IC pin as possible. In case connected to inner layer GND plane, please use several through hole. ・FB pin has comparatively hi ...

Lesson 6 – Capacitors and Capacitance

... from one point to another within the conductor, then current would flow as the electrons would be free to move to lower energy. (Because electrons are negatively charged, they move to higher voltage when they move to lower energy, which is just another way of saying that electrons are attracted by p ...

... from one point to another within the conductor, then current would flow as the electrons would be free to move to lower energy. (Because electrons are negatively charged, they move to higher voltage when they move to lower energy, which is just another way of saying that electrons are attracted by p ...

D4 HP Dimmer User’s Manual Rev 1.01

... Dimmer curves and Modes may be set manually using the Dimmer Curve and Mode DIP switches or using RDM. Whichever method is used last takes precedence. The unit maintains the last used setting over power cycles, and checks on power up to see if switches have been changed while the unit was off. Smoot ...

... Dimmer curves and Modes may be set manually using the Dimmer Curve and Mode DIP switches or using RDM. Whichever method is used last takes precedence. The unit maintains the last used setting over power cycles, and checks on power up to see if switches have been changed while the unit was off. Smoot ...

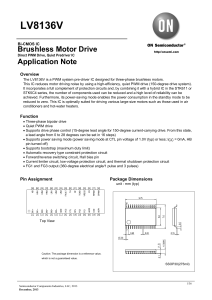

LV8136V - ONSemi

... Note: The Hall IC to be used must be of open collector or open drain type (no internal pull-up resistor connected to the output). ...

... Note: The Hall IC to be used must be of open collector or open drain type (no internal pull-up resistor connected to the output). ...

BD9488F : LED / LCD Drivers

... ○When the DC signal is used, ADIM_P will be pulled up more than 4.2V, and the signal input to the pin ADIM. ADIM_P In the driver module with more than two BD9488, and the analog dimming is performed by ADIM the duty signal, the architecture will be shown in the right figure. That can reduce the LED ...

... ○When the DC signal is used, ADIM_P will be pulled up more than 4.2V, and the signal input to the pin ADIM. ADIM_P In the driver module with more than two BD9488, and the analog dimming is performed by ADIM the duty signal, the architecture will be shown in the right figure. That can reduce the LED ...

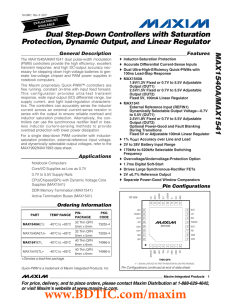

MAX1540A/MAX1541 Dual Step-Down Controllers with Saturation Protection, Dynamic Output, and Linear Regulator

... VCC, ON_ to GND.....................................................-0.3V to +6V SKIP, PGOOD_ to GND............................................-0.3V to +6V FB_, CSP_, ILIM_ to GND.........................................-0.3V to +6V TON, OVP/UVP, LSAT to GND ...................-0.3V to (VCC + 0.3V) ...

... VCC, ON_ to GND.....................................................-0.3V to +6V SKIP, PGOOD_ to GND............................................-0.3V to +6V FB_, CSP_, ILIM_ to GND.........................................-0.3V to +6V TON, OVP/UVP, LSAT to GND ...................-0.3V to (VCC + 0.3V) ...

SN74LVC1G11-Q1, Single 3-Input Positive

... TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguar ...

... TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguar ...

AC Electricity - UniMAP Portal

... • Able to define the terms peak and peak-to-peak as they apply to AC sinusoidal waveforms. • Able to convert between peak and peak-to-peak values. • Able to describe the meaning of root-mean-square (RMS) as it applies to AC sinusoidal waveforms. • Able to convert between RMS values and peak values. ...

... • Able to define the terms peak and peak-to-peak as they apply to AC sinusoidal waveforms. • Able to convert between peak and peak-to-peak values. • Able to describe the meaning of root-mean-square (RMS) as it applies to AC sinusoidal waveforms. • Able to convert between RMS values and peak values. ...

BD00GC0MEFJ-LB

... ・Input capacitor CIN of VCC (VIN) should be placed very close to VCC(VIN) pin as possible, and used broad wiring pattern. Output capacitor COUT also should be placed close to IC pin as possible. In case connected to inner layer GND plane, please use several through hole. ・FB pin has comparatively hi ...

... ・Input capacitor CIN of VCC (VIN) should be placed very close to VCC(VIN) pin as possible, and used broad wiring pattern. Output capacitor COUT also should be placed close to IC pin as possible. In case connected to inner layer GND plane, please use several through hole. ・FB pin has comparatively hi ...

Performance of Transmission Lines

... VS IS cos φS where V R , IR and cos φR are the receiving end voltage, current and power factor while V S , IS and cos φS are the corresponding values at the sending end. ...

... VS IS cos φS where V R , IR and cos φR are the receiving end voltage, current and power factor while V S , IS and cos φS are the corresponding values at the sending end. ...

DS4426 Quad-Channel, I C-Margining IDACs with Three Channels of Power-Supply Tracking

... sinking or sourcing an incorrect current before the system host controller has a chance to modify its setting. Note, however, that if power-supply tracking is enabled (see the Power-Supply Tracking Circuit section), then the DS4426 can still source current at power-up. When used in adjustable power- ...

... sinking or sourcing an incorrect current before the system host controller has a chance to modify its setting. Note, however, that if power-supply tracking is enabled (see the Power-Supply Tracking Circuit section), then the DS4426 can still source current at power-up. When used in adjustable power- ...

PCA9518A 1. General description Expandable 5-channel I

... While retaining all the operating modes and features of the I2C-bus system, it permits extension of the I2C-bus by buffering both the data (SDA) and the clock (SCL) lines, thus enabling virtually an unlimited number of buses of 400 pF. The I2C-bus capacitance limit of 400 pF restricts the number of ...

... While retaining all the operating modes and features of the I2C-bus system, it permits extension of the I2C-bus by buffering both the data (SDA) and the clock (SCL) lines, thus enabling virtually an unlimited number of buses of 400 pF. The I2C-bus capacitance limit of 400 pF restricts the number of ...

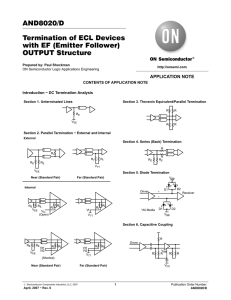

AND8020/D Termination of ECL Devices with EF (Emitter Follower) OUTPUT Structure

... rule of thumb is that the undershoot can be limited to less than 15% of the logic swing if the two way line delay is less than the rise time of the pulse. With an undershoot of <15%, the physics of the situation will result in an overshoot which will not cause saturation problems at the receiving in ...

... rule of thumb is that the undershoot can be limited to less than 15% of the logic swing if the two way line delay is less than the rise time of the pulse. With an undershoot of <15%, the physics of the situation will result in an overshoot which will not cause saturation problems at the receiving in ...

Dynamic Output Control (DOC ) Circuitry Technology and Applications

... TI’s DOC circuit. The DOC circuit limits overshoot and undershoot noise inherent in high-speed, high-current devices, while still providing propagation delays of less than 2 ns, maximum, at 2.5 V. Impedance Matching The design engineer must carefully consider a logic component’s output characteristi ...

... TI’s DOC circuit. The DOC circuit limits overshoot and undershoot noise inherent in high-speed, high-current devices, while still providing propagation delays of less than 2 ns, maximum, at 2.5 V. Impedance Matching The design engineer must carefully consider a logic component’s output characteristi ...

MAX15062 60V, 300mA, Ultra-Small, High-Efficiency, Synchronous Step-Down DC-DC Converters General Description

... operates over a 4.5V to 60V input voltage range. The converter delivers output current up to 300mA at 3.3V (MAX15062A), 5V (MAX15062B), and adjustable output voltages (MAX15062C). The device operates over the -40°C to +125°C temperature range and is available in a compact 8-pin (2mm x 2mm) TDFN pack ...

... operates over a 4.5V to 60V input voltage range. The converter delivers output current up to 300mA at 3.3V (MAX15062A), 5V (MAX15062B), and adjustable output voltages (MAX15062C). The device operates over the -40°C to +125°C temperature range and is available in a compact 8-pin (2mm x 2mm) TDFN pack ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.