LM211-Q1 数据资料 dataSheet 下载

... Supply voltage: VCC+ (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V VCC− (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −18 V VCC ...

... Supply voltage: VCC+ (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V VCC− (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −18 V VCC ...

±15kV ESD-Protected, Single/Dual/Octal, CMOS Switch Debouncers General Description Features

... The MAX6816/MAX6817/MAX6818 are single, dual, and octal switch debouncers that provide clean interfacing of mechanical switches to digital systems. They accept one or more bouncing inputs from a mechanical switch and produce a clean digital output after a short, preset qualification delay. Both the ...

... The MAX6816/MAX6817/MAX6818 are single, dual, and octal switch debouncers that provide clean interfacing of mechanical switches to digital systems. They accept one or more bouncing inputs from a mechanical switch and produce a clean digital output after a short, preset qualification delay. Both the ...

HMC-AUH232 数据资料DataSheet下载

... 43 GHz and provides a typical 3 dB bandwidth of 46 GHz. The amplifier provides 12 dB of small signal gain while requiring only 180 mA from a +5V supply. The HMC-AUH232 exhibits very good gain and phase ripple to 40 GHz, and can output up to 8V peak-to-peak with low jitter, making it ideal for use in ...

... 43 GHz and provides a typical 3 dB bandwidth of 46 GHz. The amplifier provides 12 dB of small signal gain while requiring only 180 mA from a +5V supply. The HMC-AUH232 exhibits very good gain and phase ripple to 40 GHz, and can output up to 8V peak-to-peak with low jitter, making it ideal for use in ...

An improved transformerless grid connected photovoltaic inverter

... achieve high efficiency over a wide load range. In order to obtain these advantages, an improved single-phase transformerless gridtied PV inverter topology is proposed in this paper. The main features of the proposed improved inverter are: (1) the efficiency of the inverter is improved by replacing th ...

... achieve high efficiency over a wide load range. In order to obtain these advantages, an improved single-phase transformerless gridtied PV inverter topology is proposed in this paper. The main features of the proposed improved inverter are: (1) the efficiency of the inverter is improved by replacing th ...

SP3490 数据资料DataSheet下载

... EXAR Corporation reserves the right to make changes to any products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no representation that the circuits are free of patent infringement. Charts and schedules contained herein are only for i ...

... EXAR Corporation reserves the right to make changes to any products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no representation that the circuits are free of patent infringement. Charts and schedules contained herein are only for i ...

MAX1844 High-Speed Step-Down Controller with Accurate Current Limit for Notebook Computers General Description

... Note 1: When the inductor is in continuous conduction, the output voltage will have a DC regulation level higher than the error comparator threshold by 50% of the ripple. In discontinuous conduction (SKIP = GND, light load), the output voltage will have a DC regulation level higher than the trip lev ...

... Note 1: When the inductor is in continuous conduction, the output voltage will have a DC regulation level higher than the error comparator threshold by 50% of the ripple. In discontinuous conduction (SKIP = GND, light load), the output voltage will have a DC regulation level higher than the trip lev ...

比较器系列ADCMP608 数据手册DataSheet 下载

... by keeping the capacitive load at or below the specified minimums. The output of the ADCMP608 is designed to directly drive one Schottky TTL, or three low power Schottky TTL loads, or the equivalent. For large fan outs, buses, or transmission lines, use an appropriate buffer to maintain the excellen ...

... by keeping the capacitive load at or below the specified minimums. The output of the ADCMP608 is designed to directly drive one Schottky TTL, or three low power Schottky TTL loads, or the equivalent. For large fan outs, buses, or transmission lines, use an appropriate buffer to maintain the excellen ...

Problem Set #7 solution

... (a) Assume the impressed voltage is zero, the initial charge on the capacitor is 10−5 coulomb, and the initial current is zero. Find Q(t), the charge on the capacitor, as a function of time. (b) Now assume an impressed voltage (varying with time) given by E(t) = 20 cos ωt. For what value of ω will ...

... (a) Assume the impressed voltage is zero, the initial charge on the capacitor is 10−5 coulomb, and the initial current is zero. Find Q(t), the charge on the capacitor, as a function of time. (b) Now assume an impressed voltage (varying with time) given by E(t) = 20 cos ωt. For what value of ω will ...

µPMICs for Multimedia Application Processors in a 3.0mm x 2.5mm WLP MAX8893A/MAX8893B/MAX8893C

... Note 1: LX has internal clap diodes to PGND and IN1. Applications that forward bias these diodes should take care not to exceed the IC’s package-dissipation limits. Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer boar ...

... Note 1: LX has internal clap diodes to PGND and IN1. Applications that forward bias these diodes should take care not to exceed the IC’s package-dissipation limits. Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer boar ...

unit iii analog multiplier and pll

... where R1 & C1 are external components connected to pi 8 and 9 respectively. The value of R1 and C1 are adjusted such that the free running frequency will be at the center of input frequency range. The capacitor C2 controlled between pin 7 and 10 appears as a portion of loop filter. It s value sh ...

... where R1 & C1 are external components connected to pi 8 and 9 respectively. The value of R1 and C1 are adjusted such that the free running frequency will be at the center of input frequency range. The capacitor C2 controlled between pin 7 and 10 appears as a portion of loop filter. It s value sh ...

BDTIC

... After the PFC stage, there is commonly a PWM stage to provide isolated DC output for end user. Some applications, especially computing, have the holdup time requirement. It means that PWM stage should be able to provide the isolated output even if AC input voltage become zero for a short holdup time ...

... After the PFC stage, there is commonly a PWM stage to provide isolated DC output for end user. Some applications, especially computing, have the holdup time requirement. It means that PWM stage should be able to provide the isolated output even if AC input voltage become zero for a short holdup time ...

171-M10 - Edwards Signaling

... protection, such as back-to-back zener diodes (Transorb) or an RC network, is recommended for such loads to ensure that maximum ratings of the switch are not exceeded. • Line capacitance and load capacitance. An in-line resistor can be added in series immediately before the load to limit the inrush ...

... protection, such as back-to-back zener diodes (Transorb) or an RC network, is recommended for such loads to ensure that maximum ratings of the switch are not exceeded. • Line capacitance and load capacitance. An in-line resistor can be added in series immediately before the load to limit the inrush ...

16-311 Intro to Robotics

... the sensor value periodically, with a period larger than the settling period for the switch. • In the previous slide, the settling period was 150ms • The downside to this method is that it reduces the rate at which you can read real changes. ...

... the sensor value periodically, with a period larger than the settling period for the switch. • In the previous slide, the settling period was 150ms • The downside to this method is that it reduces the rate at which you can read real changes. ...

TLC252, TLC252A, TLC252B, TLC252Y, TLC25L2, TLC25L2A, TLC25L2B

... TLC252/ 25_2 series include many areas that have previously been limited to BIFET and NFET product types. Any circuit using high-impedance elements and requiring small offset errors is a good candidate for cost-effective use of these devices. Many features associated with bipolar technology are avai ...

... TLC252/ 25_2 series include many areas that have previously been limited to BIFET and NFET product types. Any circuit using high-impedance elements and requiring small offset errors is a good candidate for cost-effective use of these devices. Many features associated with bipolar technology are avai ...

Multimode High-Frequency PWM Controller

... PFM mode, a shutdown current of less than 1 µA, a sleep-mode current of less than 100 µA and a full operating current of less than 2 mA at 1 MHz, it is ideal for building highly efficient, dc-to-dc converters. The TPS43000 operates over a wide input voltage range of 1.8 V to 9.0 V. Typical power sou ...

... PFM mode, a shutdown current of less than 1 µA, a sleep-mode current of less than 100 µA and a full operating current of less than 2 mA at 1 MHz, it is ideal for building highly efficient, dc-to-dc converters. The TPS43000 operates over a wide input voltage range of 1.8 V to 9.0 V. Typical power sou ...

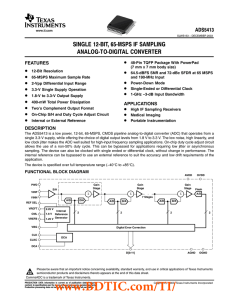

ADS5413 数据资料 dataSheet 下载

... The ADS5413 is a low power, 12-bit, 65-MSPS, CMOS pipeline analog-to-digital converter (ADC) that operates from a single 3.3-V supply, while offering the choice of digital output levels from 1.8 V to 3.3 V. The low noise, high linearity, and low clock jitter makes the ADC well suited for high-input ...

... The ADS5413 is a low power, 12-bit, 65-MSPS, CMOS pipeline analog-to-digital converter (ADC) that operates from a single 3.3-V supply, while offering the choice of digital output levels from 1.8 V to 3.3 V. The low noise, high linearity, and low clock jitter makes the ADC well suited for high-input ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.