High Precision, Low Noise OPERATIONAL AMPLIFIERS FEATURES DESCRIPTION

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

Transponder power supply, a transponder and a method for

... output terminal of the emergency circuit 203, by using the step down converter circuit 207, less energy is wasted, and therefore the charge in the emergency capacitor 105 may last ...

... output terminal of the emergency circuit 203, by using the step down converter circuit 207, less energy is wasted, and therefore the charge in the emergency capacitor 105 may last ...

TLV2322, TLV2322Y, TLV2324, TLV2324Y LinCMOS LOW-VOLTAGE LOW-POWER OPERATIONAL AMPLIFIERS

... standard warranty. Production processing does not necessarily include testing of all parameters. ...

... standard warranty. Production processing does not necessarily include testing of all parameters. ...

Linear Current Starved Delay Element

... realized only with variable capacitor, by changing its inverse control voltage, Vctrl, but the transfer function, tdelay=F(Vctrl), will be nonlinear. We do not propose this solution. b) Swing voltage, VSW: it is an input voltage level at which the state at the output of the clock buffer (inverter) c ...

... realized only with variable capacitor, by changing its inverse control voltage, Vctrl, but the transfer function, tdelay=F(Vctrl), will be nonlinear. We do not propose this solution. b) Swing voltage, VSW: it is an input voltage level at which the state at the output of the clock buffer (inverter) c ...

MAX1710/MAX1711/MAX1712 High-Speed, Digitally Adjusted Step-Down Controllers for Notebook CPUs General Description

... The MAX1710 achieves high efficiency at a reduced cost by eliminating the current-sense resistor found in traditional current-mode PWMs. Efficiency is further enhanced by an ability to drive very large synchronousrectifier MOSFETs. Single-stage buck conversion allows these devices to directly step d ...

... The MAX1710 achieves high efficiency at a reduced cost by eliminating the current-sense resistor found in traditional current-mode PWMs. Efficiency is further enhanced by an ability to drive very large synchronousrectifier MOSFETs. Single-stage buck conversion allows these devices to directly step d ...

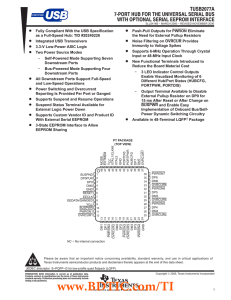

TUSB2077A 数据资料 dataSheet 下载

... The EXTMEM (terminal 47) enables or disables the optional EEPROM interface. When EXTMEM is high, the vendor and product IDs (VID and PID) use defaults, such that the message displayed during enumeration is General Purpose USB Hub. For this configuration, terminal 8 functions as the GANGED input term ...

... The EXTMEM (terminal 47) enables or disables the optional EEPROM interface. When EXTMEM is high, the vendor and product IDs (VID and PID) use defaults, such that the message displayed during enumeration is General Purpose USB Hub. For this configuration, terminal 8 functions as the GANGED input term ...

Applied Sciences t of LAB MANUAL

... on the low voltage side. The ammeter A is a low range ammeter and W is a low range and low power factor wattmeter. The high voltage side is kept opencircuited. AC supply at rated voltage is switched on to the transformer through DPIC switch. High range voltmeter V2 is connected across the secondary ...

... on the low voltage side. The ammeter A is a low range ammeter and W is a low range and low power factor wattmeter. The high voltage side is kept opencircuited. AC supply at rated voltage is switched on to the transformer through DPIC switch. High range voltmeter V2 is connected across the secondary ...

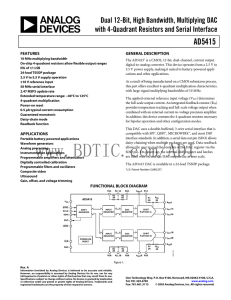

AD5415 数据手册DataSheet 下载

... when the device is in standalone mode, or on the rising edge of SYNC when in daisy-chain mode. Serial Clock Input. By default, data is clocked into the input shift register on the falling edge of the serial clock input. Alternatively, by means of the serial control bits, the device can be configured ...

... when the device is in standalone mode, or on the rising edge of SYNC when in daisy-chain mode. Serial Clock Input. By default, data is clocked into the input shift register on the falling edge of the serial clock input. Alternatively, by means of the serial control bits, the device can be configured ...

AD9863

... In half-duplex systems, the interface supports 24-bit parallel transfers or 12-bit interleaved transfers. In full-duplex systems, the interface supports a 12-bit interleaved ADC bus and a 12-bit interleaved TxDAC bus. The flexible I/O bus reduces pin count, also reducing the required package size on ...

... In half-duplex systems, the interface supports 24-bit parallel transfers or 12-bit interleaved transfers. In full-duplex systems, the interface supports a 12-bit interleaved ADC bus and a 12-bit interleaved TxDAC bus. The flexible I/O bus reduces pin count, also reducing the required package size on ...

TLV2342, TLV2342Y, TLV2344, TLV2344Y LinCMOS LOW-VOLTAGE HIGH-SPEED OPERATIONAL AMPLIFIERS

... Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. ...

... Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. ...

4-channel half-duplex m-lvds line transceivers

... Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also accommodating stubs on the bus. Receiver outputs are slew rate controlled to reduce EMI and crosstalk effect ...

... Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also accommodating stubs on the bus. Receiver outputs are slew rate controlled to reduce EMI and crosstalk effect ...

AD7466 数据手册DataSheet 下载

... the falling edge of CS, and the conversion is also initiated at this point. There are no pipeline delays associated with the part. The reference for the part is taken internally from VDD. This allows the widest dynamic input range to the ADC. Thus, the analog input range for the part is 0 V to VDD. ...

... the falling edge of CS, and the conversion is also initiated at this point. There are no pipeline delays associated with the part. The reference for the part is taken internally from VDD. This allows the widest dynamic input range to the ADC. Thus, the analog input range for the part is 0 V to VDD. ...

BQ24640 - Texas Instruments

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absol ...

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absol ...

Datasheet - Mouser Electronics

... RIN pin. In this mode, the high side output is fixed and the low side output is switching, corresponding to the input signal. The state of the output toggles between "L" and "Hi-Z". The frequency of the input PWM signal can be between 20kHz and 100kHz. The circuit may not operate properly for PWM fr ...

... RIN pin. In this mode, the high side output is fixed and the low side output is switching, corresponding to the input signal. The state of the output toggles between "L" and "Hi-Z". The frequency of the input PWM signal can be between 20kHz and 100kHz. The circuit may not operate properly for PWM fr ...

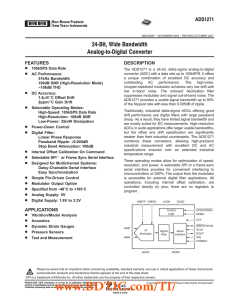

Analog-to-digital converter

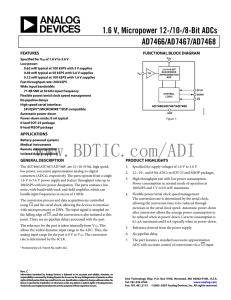

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).