Low Power, Buffered 24-Bit Sigma-Delta ADC AD7791

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

Informal Logic

... Example: a temperature/light sensor circuit that can correlate temperature and light readings to send a number of different types of alerts Example: a temperature sensor circuit that contains an Ethernet controller board that can be programmed to send raw data and/or a set of alerts ...

... Example: a temperature/light sensor circuit that can correlate temperature and light readings to send a number of different types of alerts Example: a temperature sensor circuit that contains an Ethernet controller board that can be programmed to send raw data and/or a set of alerts ...

AD795

... with the guarding schemes shown in Figures 31 and 32. Standard “G10” type printed circuit board material may not have high enough volume resistivity to hold leakages at the subpicoampere level particularly under high humidity conditions. One option that eliminates all effects of board resistance is ...

... with the guarding schemes shown in Figures 31 and 32. Standard “G10” type printed circuit board material may not have high enough volume resistivity to hold leakages at the subpicoampere level particularly under high humidity conditions. One option that eliminates all effects of board resistance is ...

Automatic Routine Speeds Power-Supply

... Fig. 2. The calibration setup block diagram for the ADM1041 controller IC shows the hardware and should have. The common-mode software needed to perform the trimming and system-monitoring functions. slope register is then programmed is employed and when the IC measurnal resistor divider network and ...

... Fig. 2. The calibration setup block diagram for the ADM1041 controller IC shows the hardware and should have. The common-mode software needed to perform the trimming and system-monitoring functions. slope register is then programmed is employed and when the IC measurnal resistor divider network and ...

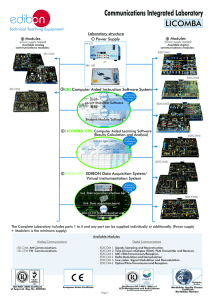

LICOMBA Communications Integrated Laboratory Laboratory structure Modules

... sampled. The transmitter sends "1" if the signal has increased since the last time it was sampled, or "0" if it has decreased. Later on the analog signal must be rebuilt at the receiver. This modulation has some drawbacks depending on various parameters, for example the variation slope of the analog ...

... sampled. The transmitter sends "1" if the signal has increased since the last time it was sampled, or "0" if it has decreased. Later on the analog signal must be rebuilt at the receiver. This modulation has some drawbacks depending on various parameters, for example the variation slope of the analog ...

Chapter 3: Capacitors, Inductors, and Complex Impedance ( )

... One of the most basic rules of electronics is that circuits must be complete for currents to flow. This week, we will introduce an exception to that rule. The capacitor is actually a small break in a circuit. Try measuring the resistance of a capacitor, you will find that it is an open circuit. Howe ...

... One of the most basic rules of electronics is that circuits must be complete for currents to flow. This week, we will introduce an exception to that rule. The capacitor is actually a small break in a circuit. Try measuring the resistance of a capacitor, you will find that it is an open circuit. Howe ...

12-Bit Input-Buffered 80 MSPS ADC with JESD204A Output Interface

... Analog section power down, JESD interface still active. This is referred to as fast recovery powerdown ...

... Analog section power down, JESD interface still active. This is referred to as fast recovery powerdown ...

LM158/LM258/LM358/LM2904 Low Power Dual Operational

... internal conductors and result in a destroyed unit. Large differential input voltages can be easily accomodated and, as input differential voltage protection diodes are not needed, no large input currents result from large differential input voltages. The differential input voltage may be larger tha ...

... internal conductors and result in a destroyed unit. Large differential input voltages can be easily accomodated and, as input differential voltage protection diodes are not needed, no large input currents result from large differential input voltages. The differential input voltage may be larger tha ...

Bounce Diagrams

... 1) The switch is closed: At time t=0, the switch is closed and the source end of the transmission line becomes energized. At this moment, the source sees only the impedance of the line. The effects of the load will not be felt at the source until t=2T, the time it takes for the signal to travel to t ...

... 1) The switch is closed: At time t=0, the switch is closed and the source end of the transmission line becomes energized. At this moment, the source sees only the impedance of the line. The effects of the load will not be felt at the source until t=2T, the time it takes for the signal to travel to t ...

07LAB1 - University of Guelph Physics

... voltmeter) in labs, it permits the visual display of a voltage signal (amplitude vs time), and can also be used to measure the average value, the root-mean-square (rms) value (which is usually used to compute power), frequency, and period of a sinusoidal or non-sinusoidal signal. The screen is divid ...

... voltmeter) in labs, it permits the visual display of a voltage signal (amplitude vs time), and can also be used to measure the average value, the root-mean-square (rms) value (which is usually used to compute power), frequency, and period of a sinusoidal or non-sinusoidal signal. The screen is divid ...

ADCMP606/ADCMP607 Rail-to-Rail, Very Fast, 2.5 V to 5.5 V

... Noninverting Output. Q is at logic high if the analog voltage at the noninverting input, VP, is greater than the analog voltage at the inverting input, VN, if the comparator is in compare mode. The metallic back surface of the package is electrically connected to VEE. It can be left floating because ...

... Noninverting Output. Q is at logic high if the analog voltage at the noninverting input, VP, is greater than the analog voltage at the inverting input, VN, if the comparator is in compare mode. The metallic back surface of the package is electrically connected to VEE. It can be left floating because ...

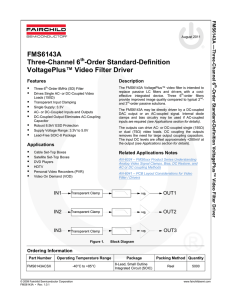

FMS6143A Three-Channel 6 -Order Standard-Definition VoltagePlus™ Video Filter Driver

... consideration must be given to providing an adequate heat sink for the device package for maximum heat dissipation. When designing a system board, determine how much power each device dissipates. Ensure that devices of high power are not placed in the same location, such as directly above (top plane ...

... consideration must be given to providing an adequate heat sink for the device package for maximum heat dissipation. When designing a system board, determine how much power each device dissipates. Ensure that devices of high power are not placed in the same location, such as directly above (top plane ...

Lab03 - Weber State University

... voltage divider to attenuate your input signal, don’t forget to factor the attenuation into your gain calculations. You can also put resistors at the emitters to improve the linearity (see Fig. 8.18 in the text). Apply a 1-kHz sinusoidal signal of 0.1V peak-to-peak to both inputs. Measure the amplit ...

... voltage divider to attenuate your input signal, don’t forget to factor the attenuation into your gain calculations. You can also put resistors at the emitters to improve the linearity (see Fig. 8.18 in the text). Apply a 1-kHz sinusoidal signal of 0.1V peak-to-peak to both inputs. Measure the amplit ...

"AGND" and "DGND"

... It is true that this arrangement may inject a small amount of digital noise onto the analog ground plane. These currents should be quite small, and can be minimized by ensuring that the converter output does not drive a large fanout (they normally can't, by design). Minimizing the fanout on the conv ...

... It is true that this arrangement may inject a small amount of digital noise onto the analog ground plane. These currents should be quite small, and can be minimized by ensuring that the converter output does not drive a large fanout (they normally can't, by design). Minimizing the fanout on the conv ...

inteli-power 9000 / 9100 trouble shooting guide

... small area and not enough ventilation is provided the converter will "shut down" reducing the output voltage and current to prevent heat damage to the components. Once the unit has cooled the system will resume normal operation. The units also incorporate reverse battery protection to protect the co ...

... small area and not enough ventilation is provided the converter will "shut down" reducing the output voltage and current to prevent heat damage to the components. Once the unit has cooled the system will resume normal operation. The units also incorporate reverse battery protection to protect the co ...

Analog-to-digital converter

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).