LT1011/LT1011A - Voltage Comparator

... and/or common mode voltages can be tolerated without damage to the comparator. Either or both inputs can be raised 40V above the negative supply, independent of the positive supply voltage. Internal forward biased diodes will conduct when the inputs are taken below the negative supply. In this condi ...

... and/or common mode voltages can be tolerated without damage to the comparator. Either or both inputs can be raised 40V above the negative supply, independent of the positive supply voltage. Internal forward biased diodes will conduct when the inputs are taken below the negative supply. In this condi ...

Decibel Conversion

... where A is the overall gain. Let us find the decibel equivalent of the overall gain. Adb = 20 log A = 20 log A1 A2 A3 Recall that the logarithm of a product of numbers is equal to, the sum of the logarithms of each number. ...

... where A is the overall gain. Let us find the decibel equivalent of the overall gain. Adb = 20 log A = 20 log A1 A2 A3 Recall that the logarithm of a product of numbers is equal to, the sum of the logarithms of each number. ...

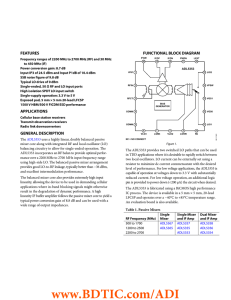

FEATURES FUNCTIONAL BLOCK DIAGRAM

... mixer core along with integrated RF and local oscillator (LO) balancing circuitry to allow for single-ended operation. The ADL5353 incorporates an RF balun to provide optimal performance over a 2200 MHz to 2700 MHz input frequency range using high-side LO. The balanced passive mixer arrangement prov ...

... mixer core along with integrated RF and local oscillator (LO) balancing circuitry to allow for single-ended operation. The ADL5353 incorporates an RF balun to provide optimal performance over a 2200 MHz to 2700 MHz input frequency range using high-side LO. The balanced passive mixer arrangement prov ...

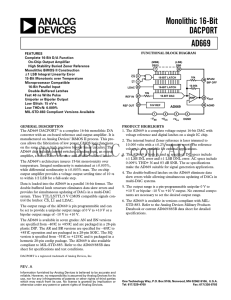

AD669 数据手册DataSheet 下载

... OFFSET ERROR: Offset error is a combination of the offset errors of the voltage-mode DAC and the output amplifier and is measured with all 0s loaded in the DAC. ...

... OFFSET ERROR: Offset error is a combination of the offset errors of the voltage-mode DAC and the output amplifier and is measured with all 0s loaded in the DAC. ...

SN65HVD11-HT 数据资料 dataSheet 下载

... Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absol ...

... Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absol ...

CDCM1802: Clock Buffer w/Programmable Divider, LVPECL I/O +

... Differential input clock. Input stage is sensitive and has a wide common mode range. Therefore, almost any type of differential signal can drive this input (LVPECL, LVDS, CML, HSTL). Since the input is high-impedance, it is recommended to terminate the PCB transmission line before the input (for exa ...

... Differential input clock. Input stage is sensitive and has a wide common mode range. Therefore, almost any type of differential signal can drive this input (LVPECL, LVDS, CML, HSTL). Since the input is high-impedance, it is recommended to terminate the PCB transmission line before the input (for exa ...

AD8603_DataSheet

... Chttp://www.mianfeiwendang.com/doc/ea0f083302a80ec7e2c19ac3F = 50 pF yields a phase margin of about 45° for the values shown in Figure 45. ...

... Chttp://www.mianfeiwendang.com/doc/ea0f083302a80ec7e2c19ac3F = 50 pF yields a phase margin of about 45° for the values shown in Figure 45. ...