AD8037

... clamp levels, signals with speeds up to 240 MHz can be applied to the clamp pins. The clamp values can also be set to any value within the output voltage range provided that VH is greater that VL. Due to these clamp characteristics, the AD8036 and AD8037 can be used in nontraditional applications su ...

... clamp levels, signals with speeds up to 240 MHz can be applied to the clamp pins. The clamp values can also be set to any value within the output voltage range provided that VH is greater that VL. Due to these clamp characteristics, the AD8036 and AD8037 can be used in nontraditional applications su ...

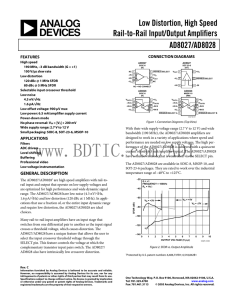

AD8027

... The AD8027/AD80281 are high speed amplifiers with rail-torail input and output that operate on low supply voltages and are optimized for high performance and wide dynamic signal range. The AD8027/AD8028 have low noise (4.3 nV/√Hz, 1.6 pA/√Hz) and low distortion (120 dBc at 1 MHz). In applications th ...

... The AD8027/AD80281 are high speed amplifiers with rail-torail input and output that operate on low supply voltages and are optimized for high performance and wide dynamic signal range. The AD8027/AD8028 have low noise (4.3 nV/√Hz, 1.6 pA/√Hz) and low distortion (120 dBc at 1 MHz). In applications th ...

AN-1148 Linear Regulators: Theory of

... current (IGND) as shown in Figure 4, neglecting the small IC bias currents which also flow to ground. It can be seen that the value of IGND is the load current IL divided by the gain of the pass transistor. The high gain of the Darlington in an NPN regulator means it requires very little drive to so ...

... current (IGND) as shown in Figure 4, neglecting the small IC bias currents which also flow to ground. It can be seen that the value of IGND is the load current IL divided by the gain of the pass transistor. The high gain of the Darlington in an NPN regulator means it requires very little drive to so ...

LTC5569 - 300MHz to 4GHz 3.3V Dual Active Downconverting Mixer.

... RFA/RFB (Pin 1/Pin 4): Single-Ended RF Inputs for the A and B Mixers, Respectively. These pins are internally connected to the primary winding of the integrated RF transformers, which have low DC resistance to ground. Series DC-blocking capacitors must be used if the RF sources have DC voltage prese ...

... RFA/RFB (Pin 1/Pin 4): Single-Ended RF Inputs for the A and B Mixers, Respectively. These pins are internally connected to the primary winding of the integrated RF transformers, which have low DC resistance to ground. Series DC-blocking capacitors must be used if the RF sources have DC voltage prese ...

A Resistively Degenerated Wide-Band Passive Mixer with Low

... resistance is increased since Cp1 is the dominant parasitic capacitance. The difference between the conventional and proposed passive Mixer is illustrated in Fig. 3. Another issue is that the RF current from preceding stage can not be perfectly separated, due to mismatches in the Mixer cores. All mi ...

... resistance is increased since Cp1 is the dominant parasitic capacitance. The difference between the conventional and proposed passive Mixer is illustrated in Fig. 3. Another issue is that the RF current from preceding stage can not be perfectly separated, due to mismatches in the Mixer cores. All mi ...

Second-order intermodulation mechanisms in CMOS downconverters

... where spectral components at higher frequencies, not of interest in this analysis, have been neglected. Equation (4) tells that, as far as direct or low-IF conversions are concerned, the second term is responsible for intermodulation, while the first one is a dc offset, and the other spectral compon ...

... where spectral components at higher frequencies, not of interest in this analysis, have been neglected. Equation (4) tells that, as far as direct or low-IF conversions are concerned, the second term is responsible for intermodulation, while the first one is a dc offset, and the other spectral compon ...

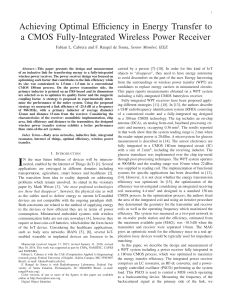

Achieving Optimal Efficiency in Energy Transfer to a CMOS Fully

... toward the RF source. Thus, the backscattering communication is used to provide information regarding the amount of power received at the load. Since the received power is estimated from the measured frequency, the sensitivity of the PSCO frequency to power consumption must be stronger than to other ...

... toward the RF source. Thus, the backscattering communication is used to provide information regarding the amount of power received at the load. Since the received power is estimated from the measured frequency, the sensitivity of the PSCO frequency to power consumption must be stronger than to other ...

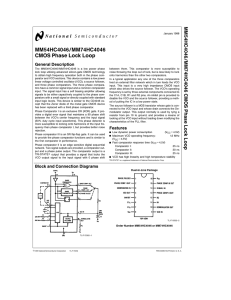

MM74HC4046 CMOS Phase Lock Loop - Elektronik

... This comparator is a simple S-R Flip-Flop which can function as a phase comparator Figure 8. It has some similar characteristics to the edge sensitive comparator. To see how this detector works assume input pulses are applied to the signal and comparator inputs as shown in Figure 9. When the signal ...

... This comparator is a simple S-R Flip-Flop which can function as a phase comparator Figure 8. It has some similar characteristics to the edge sensitive comparator. To see how this detector works assume input pulses are applied to the signal and comparator inputs as shown in Figure 9. When the signal ...

TDA8953 2 × 210 W class-D power amplifier

... and at the same time discharges the capacitor on pin PROT. When CPROT is fully discharged, the amplifier shuts down completely and an internal timer is started. The value of the protection capacitor (CPROT) connected to pin PROT can be between 10 pF and 220 pF (typically 47 pF). While OCP is activat ...

... and at the same time discharges the capacitor on pin PROT. When CPROT is fully discharged, the amplifier shuts down completely and an internal timer is started. The value of the protection capacitor (CPROT) connected to pin PROT can be between 10 pF and 220 pF (typically 47 pF). While OCP is activat ...

CDR`s circuit performance in sensing and recovering

... process of PCIe has been implemented in the mobile, workstation, server, embedded computing and communication platforms. PCIe have meets the requirements for high performance features with the inventions of two different generations PCIe. First generation of I/O interconnects with initial speed 2.5 ...

... process of PCIe has been implemented in the mobile, workstation, server, embedded computing and communication platforms. PCIe have meets the requirements for high performance features with the inventions of two different generations PCIe. First generation of I/O interconnects with initial speed 2.5 ...

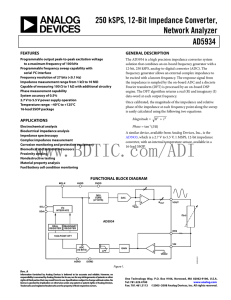

AD5934 数据手册DataSheet 下载

... Changes to System Description Section and Figure 14..............12 Changes to Figure 16 ......................................................................13 Changes to Frequency Sweep Command Sequence Section and ...

... Changes to System Description Section and Figure 14..............12 Changes to Figure 16 ......................................................................13 Changes to Frequency Sweep Command Sequence Section and ...

NCP1631PFCGEVB Interleaved PFC Stage Driven by the NCP1631 Evaluation Board User's

... approach has several merits like the ease of implementation, the use of more but smaller components or a better heat distribution. Also, Interleaving extends the power range of Critical Conduction Mode (CrM) that is an efficient and cost−effective technique (no need for low trr diodes). Even, as rep ...

... approach has several merits like the ease of implementation, the use of more but smaller components or a better heat distribution. Also, Interleaving extends the power range of Critical Conduction Mode (CrM) that is an efficient and cost−effective technique (no need for low trr diodes). Even, as rep ...

MURI Book 4

... a klystron is RT, then the maximum bandwidth attainable with a single-gap output is equal to the cavity R/Q multiplied by /2 and divided by RT. The single-gap distinction is important because as we shall see, extended interaction (multiple-gap) output circuits do not obey this rule and make possibl ...

... a klystron is RT, then the maximum bandwidth attainable with a single-gap output is equal to the cavity R/Q multiplied by /2 and divided by RT. The single-gap distinction is important because as we shall see, extended interaction (multiple-gap) output circuits do not obey this rule and make possibl ...

Operational Transconductance Amplifier Design for A 16

... For a 16 bit pipelined ADC that is clocked at 1 MHz, the required Op Amp must have unity gain frequency, ...

... For a 16 bit pipelined ADC that is clocked at 1 MHz, the required Op Amp must have unity gain frequency, ...

ncp1651 - Single Stage Power Factor Controller

... excellent voltage regulation, and transient response on the isolated DC output. The major disadvantage of the boost topology is that two power stages are required which lowers the systems efficiency, increases components count, cost, and increases the size of the power supply. ON Semiconductor’s NCP ...

... excellent voltage regulation, and transient response on the isolated DC output. The major disadvantage of the boost topology is that two power stages are required which lowers the systems efficiency, increases components count, cost, and increases the size of the power supply. ON Semiconductor’s NCP ...

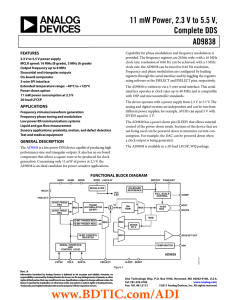

11 mW Power, 2.3 V to 5.5 V, Complete DDS AD9838

... output frequency accuracy and phase noise are determined by this clock. Frequency Select Input. FSELECT controls which frequency register, FREQ0 or FREQ1, is used in the phase accumulator. The frequency register to be used can be selected using the FSELECT pin or the FSEL bit. When the FSEL bit is u ...

... output frequency accuracy and phase noise are determined by this clock. Frequency Select Input. FSELECT controls which frequency register, FREQ0 or FREQ1, is used in the phase accumulator. The frequency register to be used can be selected using the FSELECT pin or the FSEL bit. When the FSEL bit is u ...

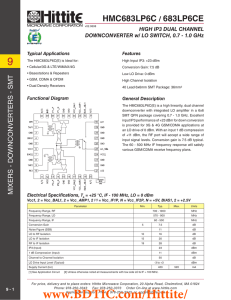

HMC683LP6C 数据资料DataSheet下载

... is provided for 3G & 4G GSM/CDMA applications at an LO drive of 0 dBm. With an input 1 dB compression of +11 dBm, the RF port will accept a wide range of input signal levels. Conversion gain is 7.5 dB typical. The 60 - 500 MHz IF frequency response will satisfy various GSM/CDMA receive frequency pla ...

... is provided for 3G & 4G GSM/CDMA applications at an LO drive of 0 dBm. With an input 1 dB compression of +11 dBm, the RF port will accept a wide range of input signal levels. Conversion gain is 7.5 dB typical. The 60 - 500 MHz IF frequency response will satisfy various GSM/CDMA receive frequency pla ...

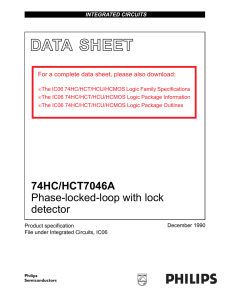

Phase-locked-loop with lock detector

... A lock detector is provided and this gives a HIGH level at pin 1 (LD) when the PLL is locked. The lock detector capacitor must be connected between pin 15 (CLD) and pin 8 (GND). The value of the CLD capacitor can be determined, using information supplied in Fig.32. The input signal can be directly c ...

... A lock detector is provided and this gives a HIGH level at pin 1 (LD) when the PLL is locked. The lock detector capacitor must be connected between pin 15 (CLD) and pin 8 (GND). The value of the CLD capacitor can be determined, using information supplied in Fig.32. The input signal can be directly c ...

AD797 Ultralow Distortion, Ultralow Noise Op Amp Data Sheet

... The architecture of the AD797 was developed to overcome inherent limitations in previous amplifier designs. Previous precision amplifiers used three stages to ensure high open-loop gain (Figure 30) at the expense of additional frequency compensation components. Slew rate and settling performance are ...

... The architecture of the AD797 was developed to overcome inherent limitations in previous amplifier designs. Previous precision amplifiers used three stages to ensure high open-loop gain (Figure 30) at the expense of additional frequency compensation components. Slew rate and settling performance are ...

CLC5523 Low Power, Variable Gain Amplifier

... Avmax would be even higher and the distortion would degrade further. It is for this reason that we recommend lower output amplitude if wide gain range are desired. Using a post-amp like the CLC404 or CLC409 would be the best way to preserve dynamic range and yield output amplitudes much higher than ...

... Avmax would be even higher and the distortion would degrade further. It is for this reason that we recommend lower output amplitude if wide gain range are desired. Using a post-amp like the CLC404 or CLC409 would be the best way to preserve dynamic range and yield output amplitudes much higher than ...

Superheterodyne receiver

In electronics, a superheterodyne receiver (often shortened to superhet) uses frequency mixing to convert a received signal to a fixed intermediate frequency (IF) which can be more conveniently processed than the original radio carrier frequency. It was invented by US engineer Edwin Armstrong in 1918 during World War I. Virtually all modern radio receivers use the superheterodyne principle. At the cost of an extra frequency converter stage, the superheterodyne receiver provides superior selectivity and sensitivity compared with simpler designs.