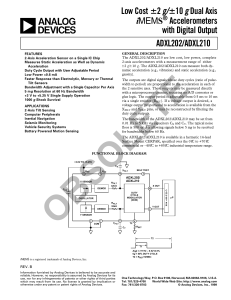

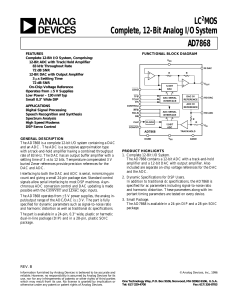

AD7868 LC2MOS Complete, 12-Bit Analog I/O

... for the ADC data outputs and power supply decoupling capacitors. It is comprised of a 12-bit successive approximation ADC with a track/hold amplifier, a 12-bit DAC with a buffered output and two 3 V buried Zener references, a clock oscillator and control logic. ADC CLOCK ...

... for the ADC data outputs and power supply decoupling capacitors. It is comprised of a 12-bit successive approximation ADC with a track/hold amplifier, a 12-bit DAC with a buffered output and two 3 V buried Zener references, a clock oscillator and control logic. ADC CLOCK ...

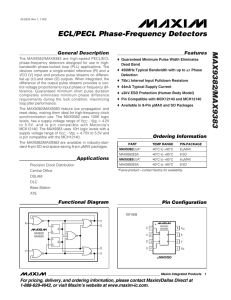

MAX9382/MAX9383 ECL/PECL Phase

... The MAX9382/MAX9383 are high-speed phase or frequency detectors. The MAX9382 is compatible with 100K logic and has a power-supply range of VCC - VEE = 4.2V to 5.5V. The MAX9383 is compatible with 10H logic with a power-supply range of VCC - VEE = 4.75V to 5.5V. Both devices are specified to function ...

... The MAX9382/MAX9383 are high-speed phase or frequency detectors. The MAX9382 is compatible with 100K logic and has a power-supply range of VCC - VEE = 4.2V to 5.5V. The MAX9383 is compatible with 10H logic with a power-supply range of VCC - VEE = 4.75V to 5.5V. Both devices are specified to function ...

LT1884 - Dual/Quad Rail-to-Rail Output, Picoamp Input Precision Op Amps

... LT1885 requires that the applications circuit and PC board layout do not introduce errors comparable to or greater than the 30µV offset. Temperature differentials across the input connections can generate thermocouple voltages of 10s of microvolts. PC board layouts should keep connections to the amp ...

... LT1885 requires that the applications circuit and PC board layout do not introduce errors comparable to or greater than the 30µV offset. Temperature differentials across the input connections can generate thermocouple voltages of 10s of microvolts. PC board layouts should keep connections to the amp ...

LT5524

... The LT5524 is a transconductance amplifier and its operation can be understood conceptually as consisting of two steps: First, the input signal voltage is converted to an output current. The intermodulation distortion (in dBc) of the LT5524 output current is determined by the input signal level, and ...

... The LT5524 is a transconductance amplifier and its operation can be understood conceptually as consisting of two steps: First, the input signal voltage is converted to an output current. The intermodulation distortion (in dBc) of the LT5524 output current is determined by the input signal level, and ...

ADA4310-1 数据手册DataSheet 下载

... than 10 dBm peak power should consider using an external line driver, such as the ADA4310-1. Figure 21 shows an example interface between the TxDAC® output and ADA4310-1 biased for single-supply operation. The TxDAC’s peak-to-peak differential output voltage swing should be limited to 2 V p-p, with ...

... than 10 dBm peak power should consider using an external line driver, such as the ADA4310-1. Figure 21 shows an example interface between the TxDAC® output and ADA4310-1 biased for single-supply operation. The TxDAC’s peak-to-peak differential output voltage swing should be limited to 2 V p-p, with ...

Rev. PrG

... Digital interface supply pin, Digital threshold levels are referenced to the voltage applied to this pin. Voltage ranges from 1.8V to 5.5V Serial data output. Serial Data Input. This device has a 24-bit shift register. Data is clocked into the register on the falling edge of the serial clock input. ...

... Digital interface supply pin, Digital threshold levels are referenced to the voltage applied to this pin. Voltage ranges from 1.8V to 5.5V Serial data output. Serial Data Input. This device has a 24-bit shift register. Data is clocked into the register on the falling edge of the serial clock input. ...

2.2.3 Astable Circuits Word Document

... The Schmitt NOT gate solution is a very simple, neat and reliable solution if a simple clock, or pulse generator is required. However if you want to have a different ‘on’ and ‘off’ time then this simple circuit cannot perform this action, and we need to consider a more complex solution. The second m ...

... The Schmitt NOT gate solution is a very simple, neat and reliable solution if a simple clock, or pulse generator is required. However if you want to have a different ‘on’ and ‘off’ time then this simple circuit cannot perform this action, and we need to consider a more complex solution. The second m ...

TEXAS INSTRUMENTS (TLC2933AIPW) PHASE

... The TLC2933A is designed for phase-locked loop (PLL) systems and is composed of a voltage-controlled oscillator (VCO) and an edge-triggered type phase frequency detector (PFD). The oscillation frequency range of the VCO is set by an external bias resistor (RBIAS). The VCO has a 1/2 frequency divider ...

... The TLC2933A is designed for phase-locked loop (PLL) systems and is composed of a voltage-controlled oscillator (VCO) and an edge-triggered type phase frequency detector (PFD). The oscillation frequency range of the VCO is set by an external bias resistor (RBIAS). The VCO has a 1/2 frequency divider ...

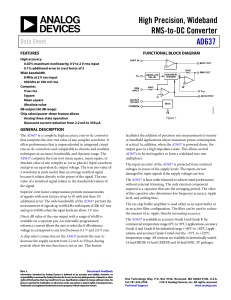

AD637 - Analog Devices

... voltages in excess of the supply levels. The inputs are not damaged by input signals if the supply voltages are lost. The AD637 is laser wafer trimmed to achieve rated performance without external trimming. The only external component required is a capacitor that sets the averaging period. The value ...

... voltages in excess of the supply levels. The inputs are not damaged by input signals if the supply voltages are lost. The AD637 is laser wafer trimmed to achieve rated performance without external trimming. The only external component required is a capacitor that sets the averaging period. The value ...

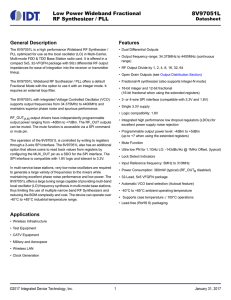

8V97051L Datasheet - Integrated Device Technology

... • Ultra low PN for 1.1GHz LO: -143dBc/Hz @ 1MHz Offset, (typical) • Lock Detect Indicators • Input Reference frequency: 5MHz to 310MHz ...

... • Ultra low PN for 1.1GHz LO: -143dBc/Hz @ 1MHz Offset, (typical) • Lock Detect Indicators • Input Reference frequency: 5MHz to 310MHz ...

LV8860V - ON Semiconductor

... --> make sure to input Hall signal with amplitude difference greater than 30mV. *When VSSW = 2V (open), VINp-p = 90 mV --> make sure to input Hall signal with amplitude difference greater than 90mV. *When VSSW = 3V (max), VINp-p = 150 mV --> make sure to input Hall signal with amplitude difference g ...

... --> make sure to input Hall signal with amplitude difference greater than 30mV. *When VSSW = 2V (open), VINp-p = 90 mV --> make sure to input Hall signal with amplitude difference greater than 90mV. *When VSSW = 3V (max), VINp-p = 150 mV --> make sure to input Hall signal with amplitude difference g ...

TPS54331 数据资料 dataSheet 下载

... The TPS54331 reduces the external component count by integrating the boot recharge diode. The bias voltage for the integrated high-side MOSFET is supplied by an external capacitor on the BOOT to PH pin. The boot capacitor voltage is monitored by an UVLO circuit and will turn the high-side MOSFET off ...

... The TPS54331 reduces the external component count by integrating the boot recharge diode. The bias voltage for the integrated high-side MOSFET is supplied by an external capacitor on the BOOT to PH pin. The boot capacitor voltage is monitored by an UVLO circuit and will turn the high-side MOSFET off ...

AD8603_DataSheet

... Chttp://www.mianfeiwendang.com/doc/ea0f083302a80ec7e2c19ac3F = 50 pF yields a phase margin of about 45° for the values shown in Figure 45. ...

... Chttp://www.mianfeiwendang.com/doc/ea0f083302a80ec7e2c19ac3F = 50 pF yields a phase margin of about 45° for the values shown in Figure 45. ...

Analog Input Buffer Architectures

... buffer shown above, the bias is set through a 10kΩ resistor. Please note that this resistor value has several implications. Since the input impedance into the op-amp is extremely high, the effective input impedance into the analog input buffer will be determined by the value of the resistor to the b ...

... buffer shown above, the bias is set through a 10kΩ resistor. Please note that this resistor value has several implications. Since the input impedance into the op-amp is extremely high, the effective input impedance into the analog input buffer will be determined by the value of the resistor to the b ...

LTC1540 - Nanopower Comparator with Reference

... and the propagation delay increases. The VREF and VOS are also slightly worse. The useful input voltage range extends from the negative supply to 0.9V below the positive supply. Test your prototype over the full temperature and supply voltage range if operation below 2V is anticipated. Because of th ...

... and the propagation delay increases. The VREF and VOS are also slightly worse. The useful input voltage range extends from the negative supply to 0.9V below the positive supply. Test your prototype over the full temperature and supply voltage range if operation below 2V is anticipated. Because of th ...

OPERATING INSTRUCTIONS AND SYSTEM DESCRIPTION FOR THE ISO-STIM 01D STIMULUS ISOLATION UNIT

... STATIC ELECTRICITY: Electronic equipment is sensitive to static discharges. Some devices such as sensor inputs are equipped with very sensitive FET amplifiers, which can be damaged by electrostatic charge and must therefore be handled with care. Electrostatic discharge can be avoided by touching a g ...

... STATIC ELECTRICITY: Electronic equipment is sensitive to static discharges. Some devices such as sensor inputs are equipped with very sensitive FET amplifiers, which can be damaged by electrostatic charge and must therefore be handled with care. Electrostatic discharge can be avoided by touching a g ...

AD797* Ultralow Distortion, Ultralow Noise Op Amp

... usually compromised, and dynamic performance is not adequate beyond audio frequencies. As can be seen in Figure 27b, the first stage gain is rolled off at high frequencies by the compensation network. Second stage noise and distortion will then appear at the input and degrade performance. The AD797 ...

... usually compromised, and dynamic performance is not adequate beyond audio frequencies. As can be seen in Figure 27b, the first stage gain is rolled off at high frequencies by the compensation network. Second stage noise and distortion will then appear at the input and degrade performance. The AD797 ...

MAX5037 VRM 9.0, Dual-Phase, Parallelable, Average Current-Mode Controller General Description

... The MAX5037 dual-phase, PWM controller provides high-output-current capability in a compact package with a minimum number of external components. The MAX5037 utilizes a dual-phase, average current-mode control that enables optimal use of low R DS(ON) MOSFETs, eliminating the need for external heatsi ...

... The MAX5037 dual-phase, PWM controller provides high-output-current capability in a compact package with a minimum number of external components. The MAX5037 utilizes a dual-phase, average current-mode control that enables optimal use of low R DS(ON) MOSFETs, eliminating the need for external heatsi ...

AD8203 High Common-Mode Voltage, Single-Supply

... 2/05—Rev. 0 to Rev. A Changes to Specifications Table...................................................... 3 Changes to Caption on Figure 6 and Figure 8 .............................. 6 Changes to Figure 12........................................................................ 7 Added Figure 14 to ...

... 2/05—Rev. 0 to Rev. A Changes to Specifications Table...................................................... 3 Changes to Caption on Figure 6 and Figure 8 .............................. 6 Changes to Figure 12........................................................................ 7 Added Figure 14 to ...