MAX11156 18-Bit, 500ksps, ±5V SAR ADC with Internal Reference in TDFN General Description

... (VDD = 4.75V to 5.25V, VOVDD = 2.3V to 5.25V, fSAMPLE = 500kHz, VREF = 4.096V, Reference Mode 3; TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25NC.) (Note 2) Note 2: Maximum and minimum limits are fully production tested over specified supply voltage range and at a tempera ...

... (VDD = 4.75V to 5.25V, VOVDD = 2.3V to 5.25V, fSAMPLE = 500kHz, VREF = 4.096V, Reference Mode 3; TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25NC.) (Note 2) Note 2: Maximum and minimum limits are fully production tested over specified supply voltage range and at a tempera ...

LT5526 - High Linearity, Low Power Downconverting Mixer.

... High Linearity, Low Power Downconverting Mixer ...

... High Linearity, Low Power Downconverting Mixer ...

LNK302/304-306 LinkSwitch-TN Family

... The feedback input circuit at the FEEDBACK pin consists of a low impedance source follower output set at 1.65 V. When the current delivered into this pin exceeds 49 µA, a low logic level (disable) is generated at the output of the feedback circuit. This output is sampled at the beginning of each cyc ...

... The feedback input circuit at the FEEDBACK pin consists of a low impedance source follower output set at 1.65 V. When the current delivered into this pin exceeds 49 µA, a low logic level (disable) is generated at the output of the feedback circuit. This output is sampled at the beginning of each cyc ...

LM5005 High Voltage 2.5 Amp Buck Regulator (Rev. E)

... on current mode control utilizing an emulated current ramp. Peak current mode control provides inherent line feed-forward, cycle-by-cycle current limiting and ease of loop compensation. The use of an emulated control ramp reduces noise sensitivity of the pulse-width modulation circuit, allowing reli ...

... on current mode control utilizing an emulated current ramp. Peak current mode control provides inherent line feed-forward, cycle-by-cycle current limiting and ease of loop compensation. The use of an emulated control ramp reduces noise sensitivity of the pulse-width modulation circuit, allowing reli ...

Operational-amplifier

... with a differential input and, usually, a single-ended output.[1] An op-amp produces an output voltage that is typically hundreds of thousands times larger than the voltage difference between its input terminals.[2] Operational amplifiers are important building blocks for a wide range of electronic ...

... with a differential input and, usually, a single-ended output.[1] An op-amp produces an output voltage that is typically hundreds of thousands times larger than the voltage difference between its input terminals.[2] Operational amplifiers are important building blocks for a wide range of electronic ...

UCC3974 数据资料 dataSheet 下载

... The LFD oscillator runs free at some frequency determined by the external timing components. The LFD oscillator can be synchronized to a system clock signal. by applying this clock signal to the LFDSYNC pin. The signal must not be applied during power up since the MODE pin’s crossing of the LFD_ENAB ...

... The LFD oscillator runs free at some frequency determined by the external timing components. The LFD oscillator can be synchronized to a system clock signal. by applying this clock signal to the LFDSYNC pin. The signal must not be applied during power up since the MODE pin’s crossing of the LFD_ENAB ...

High-Voltage, 2.2MHz, 2A Automotive Step- Down Converter with Low Operating Current MAX16974

... Junction-to-Ambient Thermal Resistance (qJA).........38.3°C/W Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial ...

... Junction-to-Ambient Thermal Resistance (qJA).........38.3°C/W Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial ...

a Very Low Noise Quad Operational Amplifier OP470

... amplifier with exceptionally low voltage noise, 5 nV/÷Hz at 1 kHz max, offering comparable performance to ADI’s industry standard OP27. The OP470 features an input offset voltage below 0.4 mV, excellent for a quad op amp, and an offset drift under 2 mV/∞C, guaranteed over the full military temperatu ...

... amplifier with exceptionally low voltage noise, 5 nV/÷Hz at 1 kHz max, offering comparable performance to ADI’s industry standard OP27. The OP470 features an input offset voltage below 0.4 mV, excellent for a quad op amp, and an offset drift under 2 mV/∞C, guaranteed over the full military temperatu ...

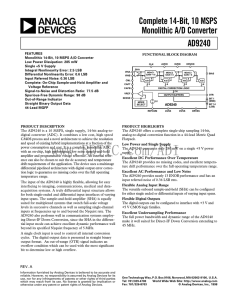

AD9240 数据手册DataSheet 下载

... interfacing to imaging, communications, medical and dataacquisition systems. A truly differential input structure allows for both single-ended and differential input interfaces of varying input spans. The sample-and-hold amplifier (SHA) is equally suited for multiplexed systems that switch full-scal ...

... interfacing to imaging, communications, medical and dataacquisition systems. A truly differential input structure allows for both single-ended and differential input interfaces of varying input spans. The sample-and-hold amplifier (SHA) is equally suited for multiplexed systems that switch full-scal ...

UNIT-V DAC: Principles – weighted-resistor network, R

... Basic integrator of a Dual-slope Integrating ADC. The comparator, the timer, and the controller are not shown. The basic integrating ADC circuit consists of an integrator, a switch to select between the voltage to be measured and the reference voltage, a timer that determines how long to integrate ...

... Basic integrator of a Dual-slope Integrating ADC. The comparator, the timer, and the controller are not shown. The basic integrating ADC circuit consists of an integrator, a switch to select between the voltage to be measured and the reference voltage, a timer that determines how long to integrate ...

MAX15108A High-Efficiency, 8A, Current-Mode Synchronous Step-Down Switching Regulator General Description

... making the device ideal for distributed power systems, portable devices, and preregulation applications. The IC utilizes a current-mode control architecture with a high gain transconductance error amplifier. The current-mode control architecture facilitates easy compensation design and ensures cycle ...

... making the device ideal for distributed power systems, portable devices, and preregulation applications. The IC utilizes a current-mode control architecture with a high gain transconductance error amplifier. The current-mode control architecture facilitates easy compensation design and ensures cycle ...

Pipelining and Parallel Processing

... In order to maintain the same sample rate, the clock period of the Lparallel circuit must be increased to LTseq, where Tseq is the propagation delay of the sequential circuit. There is more time to charge the same capacitance => supply voltage can be reduced to V 0 ...

... In order to maintain the same sample rate, the clock period of the Lparallel circuit must be increased to LTseq, where Tseq is the propagation delay of the sequential circuit. There is more time to charge the same capacitance => supply voltage can be reduced to V 0 ...

Improvement to Load-pull Technique for Design of Large

... a practical design [1]. Application of a load-pull technique to determine the optimum load impedance is a practical solution in these cases. The load-pull method was originally described in 1976 by Takayama [2] and many improvements have been published since then [3]. The load-pull method makes poss ...

... a practical design [1]. Application of a load-pull technique to determine the optimum load impedance is a practical solution in these cases. The load-pull method was originally described in 1976 by Takayama [2] and many improvements have been published since then [3]. The load-pull method makes poss ...

AD5726 数据手册DataSheet 下载

... Bipolar outputs are configured by connecting both VREFP and VREFN to nonzero voltages. This method of setting output voltage ranges has advantages over the bipolar offsetting methods because it is not dependent on internal and external resistors with different temperature coefficients. The AD5726 us ...

... Bipolar outputs are configured by connecting both VREFP and VREFN to nonzero voltages. This method of setting output voltage ranges has advantages over the bipolar offsetting methods because it is not dependent on internal and external resistors with different temperature coefficients. The AD5726 us ...

A CMOS QPSK Demodulator Frontend for GPON Fei Chen

... There are many people I would like to thank for their help and support during the course of my master research. The first person I would like to thank is my supervisor, Dr. Brian Frank for his guidance and encouragement over the past three years. He is always there to provide me with opportunities a ...

... There are many people I would like to thank for their help and support during the course of my master research. The first person I would like to thank is my supervisor, Dr. Brian Frank for his guidance and encouragement over the past three years. He is always there to provide me with opportunities a ...

AD9523-1 英文数据手册DataSheet 下载

... jitter cleanup to achieve the restrictive low phase noise requirements necessary for acceptable data converter SNR performance. The input receivers, oscillator, and zero delay receiver provide both single-ended and differential operation. When connected to a recovered system reference clock and a VC ...

... jitter cleanup to achieve the restrictive low phase noise requirements necessary for acceptable data converter SNR performance. The input receivers, oscillator, and zero delay receiver provide both single-ended and differential operation. When connected to a recovered system reference clock and a VC ...

Standards Project - Telecommunications Industry Association

... loop test condition has the nominal 8 dB value, and also calculates the corresponding SLR value for the 600 ohm without loop test condition. Column B contains the approximate 1/3 octave send sensitivity values from the TR41.3.3-10-05-009 contribution. Column C shows the data from Column B shifted by ...

... loop test condition has the nominal 8 dB value, and also calculates the corresponding SLR value for the 600 ohm without loop test condition. Column B contains the approximate 1/3 octave send sensitivity values from the TR41.3.3-10-05-009 contribution. Column C shows the data from Column B shifted by ...

ESDA Series Driver User’s Manual

... equipment nearby. (3) The Driver shall not be installed in an environment where corrosive gases, excess dust, or metal power is present. Insulation from water, water mist, or cutting fluid is required. (4) If there is a big magnet switch or welding equipment, which may generate electronic noise, nea ...

... equipment nearby. (3) The Driver shall not be installed in an environment where corrosive gases, excess dust, or metal power is present. Insulation from water, water mist, or cutting fluid is required. (4) If there is a big magnet switch or welding equipment, which may generate electronic noise, nea ...

超低功耗、负轨输入、 轨至轨输出、全差分放大器 THS4521-HT 特性

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extend ...

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extend ...

MAX9768 10W Mono Class D Speaker Amplifier with Volume Control General Description

... provides high-quality, efficient audio power with an integrated volume control function. The MAX9768 features a 64-step dual-mode (analog or digitally programmable) volume control and mute function. The audio amplifier operates from a 4.5V to 14V single supply and can deliver up to 10W into an 8Ω sp ...

... provides high-quality, efficient audio power with an integrated volume control function. The MAX9768 features a 64-step dual-mode (analog or digitally programmable) volume control and mute function. The audio amplifier operates from a 4.5V to 14V single supply and can deliver up to 10W into an 8Ω sp ...

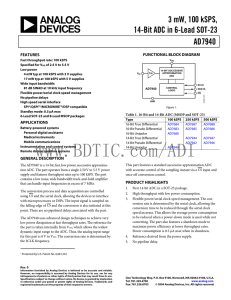

AD7940 数据手册DataSheet下载

... supply and features throughput rates up to 100 kSPS. The part contains a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 7 MHz. The conversion process and data acquisition are controlled using CS and the serial clock, allowing the devices to interfac ...

... supply and features throughput rates up to 100 kSPS. The part contains a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 7 MHz. The conversion process and data acquisition are controlled using CS and the serial clock, allowing the devices to interfac ...