Experiment #68 — Phase Locked Loops, the Basics

... itself. Phase refers to the relative two input signal frequencies, phase difference between an infA and fB, is cos(2π[fA – fB] put signal and the loop’s internal t + θ), with θ representing the oscillator. Locked means that difference in phase between the oscillator’s phase maintains the signals. I ...

... itself. Phase refers to the relative two input signal frequencies, phase difference between an infA and fB, is cos(2π[fA – fB] put signal and the loop’s internal t + θ), with θ representing the oscillator. Locked means that difference in phase between the oscillator’s phase maintains the signals. I ...

Automotive Qualified AUIRS2117S and AUIRS2118S Deliver

... The AUIRS2117S and AUIRS2118S 600V ICs were designed for automotive gate driver applications including direct injection and brushless DC motor drivers. These high side drivers feature very short turn-on and turn-off propagation time to drive the MOSFET or IGBT at a much higher frequency to shrink sy ...

... The AUIRS2117S and AUIRS2118S 600V ICs were designed for automotive gate driver applications including direct injection and brushless DC motor drivers. These high side drivers feature very short turn-on and turn-off propagation time to drive the MOSFET or IGBT at a much higher frequency to shrink sy ...

PLL applications The phase-lock-loop

... rejected, thus: d) The XOR PD has good noise rejection. Another important feature is whether the pll will lock on a harmonics of input data, the XOR PLL will lock on harmonics. To prove this replace any of clock signals at previous figures with twice/half the frequency, the average output will remai ...

... rejected, thus: d) The XOR PD has good noise rejection. Another important feature is whether the pll will lock on a harmonics of input data, the XOR PLL will lock on harmonics. To prove this replace any of clock signals at previous figures with twice/half the frequency, the average output will remai ...

RiverbeckConfPaper160516

... the varactor controlled by the charge pump and PLL loop dynamics provides fine frequency tuning. The high speed PLL dividers are implemented as CML logic and the low speed dividers in CMOS. The overall PLL architecture is a conventional Type II charge pump design. When both channels are active, four ...

... the varactor controlled by the charge pump and PLL loop dynamics provides fine frequency tuning. The high speed PLL dividers are implemented as CML logic and the low speed dividers in CMOS. The overall PLL architecture is a conventional Type II charge pump design. When both channels are active, four ...

PowerPoint Slides

... • Capacitance – Removed the tiny capacitor in the base of the coil. Added a small 1-28pf trimmer across the coil pins, set it to a few pf and centered the coil slug. Measured the output of the mixer while clicking through all the channels - perfect lock on RX and TX across the whole range and a clea ...

... • Capacitance – Removed the tiny capacitor in the base of the coil. Added a small 1-28pf trimmer across the coil pins, set it to a few pf and centered the coil slug. Measured the output of the mixer while clicking through all the channels - perfect lock on RX and TX across the whole range and a clea ...

MTR_Pedro_WP2 - Indico

... range relating to the reference clock frequency. Oscillator mode - the auto calibration logic can be used to quickly choose the VCXO parameters that have to be programmed in the Fuse-Bank to tune the oscillation frequency. ...

... range relating to the reference clock frequency. Oscillator mode - the auto calibration logic can be used to quickly choose the VCXO parameters that have to be programmed in the Fuse-Bank to tune the oscillation frequency. ...

Phase-Locked Loop Applications

... a. Frequency divider b. Loop filter c. Phase detector d. VCO 8. The output of a PLL used as a frequency demodulator is taken from the? a. Frequency divider b. Loop filter c. Phase detector d. VCO 9. The main difference between a standard PLL and a clock multiplier PLL is that the latter contains a? ...

... a. Frequency divider b. Loop filter c. Phase detector d. VCO 8. The output of a PLL used as a frequency demodulator is taken from the? a. Frequency divider b. Loop filter c. Phase detector d. VCO 9. The main difference between a standard PLL and a clock multiplier PLL is that the latter contains a? ...

RF Multiplexing Transmitting and Receiving Unit (TA: Saurav K

... A single unit of data transmission is 33 bits in length. Reason: (4 signal sources) * (1 sample per source) * (8 data bits per sample) + 1 synchronizing bit = (32 + 1) bits = 33 bits The data for all four sources are interleaved at the bit level. Bytes are transmitted MSB first, with signal source 1 ...

... A single unit of data transmission is 33 bits in length. Reason: (4 signal sources) * (1 sample per source) * (8 data bits per sample) + 1 synchronizing bit = (32 + 1) bits = 33 bits The data for all four sources are interleaved at the bit level. Bytes are transmitted MSB first, with signal source 1 ...

Prototype-Modifications-091412

... Without level shifters, envelope detector output does not overlap with full input range of log amp. Level shifters increase correction range. ...

... Without level shifters, envelope detector output does not overlap with full input range of log amp. Level shifters increase correction range. ...

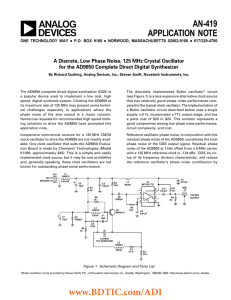

a AN-419 APPLICATION NOTE •

... a popular device used to implement a low cost, high speed, digital synthesis system. Clocking the AD9850 at its maximum rate of 125 MHz may present some technical challenges especially in applications where the phase noise of the sine output is a major concern. Numerous requests for recommended high ...

... a popular device used to implement a low cost, high speed, digital synthesis system. Clocking the AD9850 at its maximum rate of 125 MHz may present some technical challenges especially in applications where the phase noise of the sine output is a major concern. Numerous requests for recommended high ...

Development of a Picosecond-resolution TDC for

... The second design we have simulated is a time-to-amplitude converter (TAC) with a sensitivity of 1mV/ps. The maximum input time interval of 1ns will convert to a 1.0V voltage that is held in a capacitor. A 10-bit analog-to-digital converter would give a least count of 1 ps. Based on preliminary simu ...

... The second design we have simulated is a time-to-amplitude converter (TAC) with a sensitivity of 1mV/ps. The maximum input time interval of 1ns will convert to a 1.0V voltage that is held in a capacitor. A 10-bit analog-to-digital converter would give a least count of 1 ps. Based on preliminary simu ...

VLSI6332_sadi_italo_DLL

... 8 bit binary up down counter with reset and hold options. The counter is power and clock gated to reduce power when the clock phases are ...

... 8 bit binary up down counter with reset and hold options. The counter is power and clock gated to reduce power when the clock phases are ...

Voltage-controlled Oscillators (VCO), Phase Locked Loop, and

... Phase-Locked Loop (PLL) Phase-locked loop (PLL) is a feedback system consisting of a voltage-controlled oscillator, a phase comparator, and a loop filter and shown in Figure 5. The phase comparator compares the phase of the reference signal with the phase of the output of voltage control oscillator ...

... Phase-Locked Loop (PLL) Phase-locked loop (PLL) is a feedback system consisting of a voltage-controlled oscillator, a phase comparator, and a loop filter and shown in Figure 5. The phase comparator compares the phase of the reference signal with the phase of the output of voltage control oscillator ...

Liu_TWEPP09_LCPLL_poster

... (VCO), and a divider (divide by 16). An LVDS receiver and a CML driver are used as the input and output interface. The divider consists of a CML divider (divide by 2), a CML to CMOS converter, and a CMOS divider (divide by 8). The LVDS receiver, the phase frequency detector (PFD), the charge pump, t ...

... (VCO), and a divider (divide by 16). An LVDS receiver and a CML driver are used as the input and output interface. The divider consists of a CML divider (divide by 2), a CML to CMOS converter, and a CMOS divider (divide by 8). The LVDS receiver, the phase frequency detector (PFD), the charge pump, t ...

Phase Locked Loop Design for Optical Wireless

... when control bit ‘0’ PLL circuit will generate 100 MHz, when control bit ‘1’ the circuit will generate 100.1MHz. After that the synthesized signal is used as the clock signal of data buffer or First-In FirstOut (FIFO) data buffer to drive out the data signal. ...

... when control bit ‘0’ PLL circuit will generate 100 MHz, when control bit ‘1’ the circuit will generate 100.1MHz. After that the synthesized signal is used as the clock signal of data buffer or First-In FirstOut (FIFO) data buffer to drive out the data signal. ...

A Custom built UHF to VHF downconverter

... Most UHF downconverters uses a harmonic of a crystal oscillator as the mixer driver to downconvert a UHF signal to lower frequencies where affordable equipment can be used to demodulate the signal. In this design an affordable PLL synthesizer using an IC that contains an onboard VCO was used to gene ...

... Most UHF downconverters uses a harmonic of a crystal oscillator as the mixer driver to downconvert a UHF signal to lower frequencies where affordable equipment can be used to demodulate the signal. In this design an affordable PLL synthesizer using an IC that contains an onboard VCO was used to gene ...

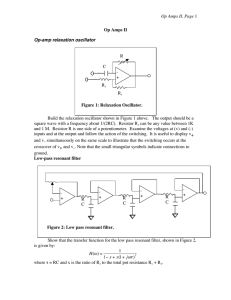

Op Amps II, Page R C -

... Choose RC so that the resonant frequency is 2 to 5 kHz. Tune the pot until the circuit nearly oscillates. See how close you can get. Notice how oscillations grow and die exponentially. Find the resonant frequency by feeding in a sine signal from a function generator. (You may need to decrease the in ...

... Choose RC so that the resonant frequency is 2 to 5 kHz. Tune the pot until the circuit nearly oscillates. See how close you can get. Notice how oscillations grow and die exponentially. Find the resonant frequency by feeding in a sine signal from a function generator. (You may need to decrease the in ...

Paper Title (use style: paper title)

... loop control system that has the ability to generate a feedback signal whose phase and frequency are aligned to the phase and frequency of the reference signal at locked condition [1]-[3]. The charge pump phase locked loop (CPPLL) is widely used for its frequency sensitive error signal, as it can ai ...

... loop control system that has the ability to generate a feedback signal whose phase and frequency are aligned to the phase and frequency of the reference signal at locked condition [1]-[3]. The charge pump phase locked loop (CPPLL) is widely used for its frequency sensitive error signal, as it can ai ...

EE311: Junior EE Lab Phase Locked Loop

... output will then increase, causing the dc component of the filter output/VCO input voltage to increase • The increasing VCO input voltage causes an increase in the VCO output frequency, i.e., causing the output frequency to match the new input frequency • The phase angle thus stabilizes at a new equ ...

... output will then increase, causing the dc component of the filter output/VCO input voltage to increase • The increasing VCO input voltage causes an increase in the VCO output frequency, i.e., causing the output frequency to match the new input frequency • The phase angle thus stabilizes at a new equ ...

PLL400-864AY 5V NARROWBAND PHASE-LOCKED LOOP Features

... Data, Clock, Enable, LD RF Feedback PLL IC ...

... Data, Clock, Enable, LD RF Feedback PLL IC ...