Lecture Notes - Practical AC Circuits File

... AC Bridges The AC bridge is Balanced when no current flows through the meter. AC bridges are used in measuring inductance and capacitance values. ...

... AC Bridges The AC bridge is Balanced when no current flows through the meter. AC bridges are used in measuring inductance and capacitance values. ...

Versatile Waveform Generator Operates from 0.1Hz to 20MHz

... edge occurs at the mid-point of the positive portion, causing SYNC to lead the output by 90°. SYNC lets you slave one MAX038 to another by providing a TTL-compatible square wave at the phase-detector input (PDI), as required by the slaved device (IC2). On the other hand, SYNC isn’t available if a MA ...

... edge occurs at the mid-point of the positive portion, causing SYNC to lead the output by 90°. SYNC lets you slave one MAX038 to another by providing a TTL-compatible square wave at the phase-detector input (PDI), as required by the slaved device (IC2). On the other hand, SYNC isn’t available if a MA ...

ISSCC D03_04 Karthik

... buffer is used at the output of each track-and-hold to drive four sample-and-hold circuits and their associated capacitive DACs. A feed-forward-based negative-gds technique in an otherwise conventional source follower helps to optimize signalto-noise performance and linearity at low supply voltages. ...

... buffer is used at the output of each track-and-hold to drive four sample-and-hold circuits and their associated capacitive DACs. A feed-forward-based negative-gds technique in an otherwise conventional source follower helps to optimize signalto-noise performance and linearity at low supply voltages. ...

PHYS4330 Theoretical Mechanics HW #3 Due 20 Sept 2011

... (4) A damped oscillator starts from rest at the origin at t = 0, at which time an oscillating driving force F (t) = F0 cos ωt is applied. The oscillator has a “natural” frequency ω0 (that is, the frequency it would have if there were no damping) and a damping parameter β. Find the complete solution, ...

... (4) A damped oscillator starts from rest at the origin at t = 0, at which time an oscillating driving force F (t) = F0 cos ωt is applied. The oscillator has a “natural” frequency ω0 (that is, the frequency it would have if there were no damping) and a damping parameter β. Find the complete solution, ...

CDR`s circuit performance in sensing and recovering

... 5Gbps. Clock data recovery circuit has become one of the building blocks in PCIe architecture. The ability of CDR to influence PCIe performance at Gigahertz data make it critical to design. With transfer rate of 5 Gbps, PLL approached are preferably chosen in [2] and [3]. Theoretical modeling and si ...

... 5Gbps. Clock data recovery circuit has become one of the building blocks in PCIe architecture. The ability of CDR to influence PCIe performance at Gigahertz data make it critical to design. With transfer rate of 5 Gbps, PLL approached are preferably chosen in [2] and [3]. Theoretical modeling and si ...

UMS-3000-R16-G 数据资料DataSheet下载

... Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Abs ...

... Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Abs ...

Basic Operation of a Frequency Synthesizer

... Phase noise in synthesizers Each of the components in a frequency synthesizer produces noise that will contribute to the overall noise that appears at the output. The actual way in which the noise from any one element in the loop contributes to the output will depend upon where it is produced. Noise ...

... Phase noise in synthesizers Each of the components in a frequency synthesizer produces noise that will contribute to the overall noise that appears at the output. The actual way in which the noise from any one element in the loop contributes to the output will depend upon where it is produced. Noise ...

phase detector

... • Phase-locked loops are used • as FM demodulators, • in carrier recovery circuits, and • as frequency synthesizers for modulation and demodulation. • Phase-locked loops have very good frequency accuracy and phase noise characteristics, but suffer from the fact that settling times (between changes ...

... • Phase-locked loops are used • as FM demodulators, • in carrier recovery circuits, and • as frequency synthesizers for modulation and demodulation. • Phase-locked loops have very good frequency accuracy and phase noise characteristics, but suffer from the fact that settling times (between changes ...

ADF4007 (Rev. B)

... These two bits set the N value. See Table 4. These two bits set the status of MUXOUT and PFD polarity. See Table 5. This multiplexer output allows either the N divider output or the R divider output to be accessed externally. Digital Power Supply. This pin can range from 2.7 V to 3.3 V. Decoupling c ...

... These two bits set the N value. See Table 4. These two bits set the status of MUXOUT and PFD polarity. See Table 5. This multiplexer output allows either the N divider output or the R divider output to be accessed externally. Digital Power Supply. This pin can range from 2.7 V to 3.3 V. Decoupling c ...

nemmani_paper

... (C) Time-to-digital converter: The time-to-digital converter compares the input reference clock and oscillator divided output and generates the phase difference word. The operation is performed as follows. The phase/frequency detector (PFD) at the input of the TDC generates UP & DN pulses. A digital ...

... (C) Time-to-digital converter: The time-to-digital converter compares the input reference clock and oscillator divided output and generates the phase difference word. The operation is performed as follows. The phase/frequency detector (PFD) at the input of the TDC generates UP & DN pulses. A digital ...

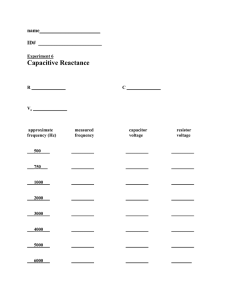

answer sheet

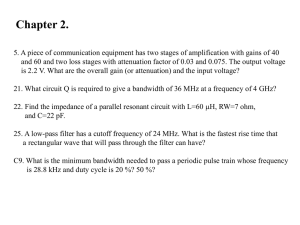

... Pick a frequency and add the magnitudes of the capacitor and resistor voltages. How does this compare to the generator voltage? This seems to contradict Kirchhoff's loop law. Why is this not the case? Questions ...

... Pick a frequency and add the magnitudes of the capacitor and resistor voltages. How does this compare to the generator voltage? This seems to contradict Kirchhoff's loop law. Why is this not the case? Questions ...

Ultra Low Power PLL Implementations

... architecture of the transceiver is such that the accuracy of the clock needed is low • Paper talks about how to do so, but will not focus on that • PLL Design Metrics – Power is MOST important – Since it is RF clock, phase noise is also given SOME ...

... architecture of the transceiver is such that the accuracy of the clock needed is low • Paper talks about how to do so, but will not focus on that • PLL Design Metrics – Power is MOST important – Since it is RF clock, phase noise is also given SOME ...

High Stability, Low Noise, Push-Push VFO

... Increasing the Loaded-Q improves the phase noise, improves long-term frequency stability versus temperature variations, reduces supply pushing, and reduces load pulling. When you build a free running Push-Push oscillator you can achieve high short-term frequency stability, which is important when th ...

... Increasing the Loaded-Q improves the phase noise, improves long-term frequency stability versus temperature variations, reduces supply pushing, and reduces load pulling. When you build a free running Push-Push oscillator you can achieve high short-term frequency stability, which is important when th ...

Tiny Low Frequency Clock Chip Supports Long Duration Timing

... LTC6991 is the latest part in the TimerBlox™ family of versatile silicon timing devices, in which an accurate programmable oscillator is combined with precision circuitry and logic. An extremely wide programmable frequency range allows the clock to operate with a period from 1ms to 9.5 hours. This m ...

... LTC6991 is the latest part in the TimerBlox™ family of versatile silicon timing devices, in which an accurate programmable oscillator is combined with precision circuitry and logic. An extremely wide programmable frequency range allows the clock to operate with a period from 1ms to 9.5 hours. This m ...