SGA2286Z 数据资料DataSheet下载

... responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change comp ...

... responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change comp ...

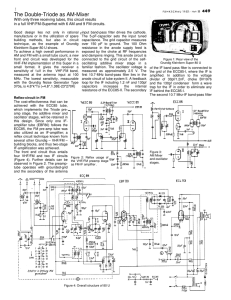

The Double-Triode as AM-Mixer

... FM in the beginning was from 87,5 to 100 MHz. Below 87,5 MHz was the Police band and above 100 MHz there was a Military band. Later on first 100 MHz to 104 MHz could be cleared and after then up to 108 MHz could be dedicated to FM broadcast as international usual. An explanation of neutralization ce ...

... FM in the beginning was from 87,5 to 100 MHz. Below 87,5 MHz was the Police band and above 100 MHz there was a Military band. Later on first 100 MHz to 104 MHz could be cleared and after then up to 108 MHz could be dedicated to FM broadcast as international usual. An explanation of neutralization ce ...

Using Two-Point Modulation To Reduce Synthesizer Problems

... Modulation can be applied to different points within the PLL, such as at the VCO input and at the master oscillator1. When modulation is applied to the input of the VCO, high-frequency content above the loop filter bandwidth of the modulating signal is developed at the VCO output. Low-frequency cont ...

... Modulation can be applied to different points within the PLL, such as at the VCO input and at the master oscillator1. When modulation is applied to the input of the VCO, high-frequency content above the loop filter bandwidth of the modulating signal is developed at the VCO output. Low-frequency cont ...

LRC Circuits

... lags the current through it by 90o; it reaches a maximum when the current is zero. Then the voltage amplitude across C in a circuit involving C and R in series could be found using the voltage divider equation, which of course is a consequence of Ohm's law. More generally, what we are saying is that ...

... lags the current through it by 90o; it reaches a maximum when the current is zero. Then the voltage amplitude across C in a circuit involving C and R in series could be found using the voltage divider equation, which of course is a consequence of Ohm's law. More generally, what we are saying is that ...

Chapter 5 - MyWeb at WIT - Wentworth Institute of Technology

... Clocked D Flip-Flop: Parallel Data Transfer ...

... Clocked D Flip-Flop: Parallel Data Transfer ...

Sample-Mike`sProject - University of Colorado Boulder

... operation of the diode is used for wave shaping purposes to sharpen pulse edges. For phase shifting applications operation only in the linear region is desired. Generally this means that the input voltage magnitude must be small with respect to the forward voltage of the diode. In this case, as show ...

... operation of the diode is used for wave shaping purposes to sharpen pulse edges. For phase shifting applications operation only in the linear region is desired. Generally this means that the input voltage magnitude must be small with respect to the forward voltage of the diode. In this case, as show ...

Section H5: High-Frequency Amplifier Response

... same and the relationship between vS and vin is a voltage divider! Again, in some instances in the following discussion, I will be using slightly different notation and taking a different approach than your author. As usual, if this results in confusion, or you are more comfortable with his techniqu ...

... same and the relationship between vS and vin is a voltage divider! Again, in some instances in the following discussion, I will be using slightly different notation and taking a different approach than your author. As usual, if this results in confusion, or you are more comfortable with his techniqu ...

LTC3880 System Checklist

... o Ensure VIN, V3.3, V2.5 high impedance when dongle connected without VIN o No body diodes between SDA/SCL from any slave device Test Points o Input o Output Polyphase rails o Tie all SNYC together o For any given SYNC group, only one chip (we call this the frequency master) can specify a FREQUENCY_ ...

... o Ensure VIN, V3.3, V2.5 high impedance when dongle connected without VIN o No body diodes between SDA/SCL from any slave device Test Points o Input o Output Polyphase rails o Tie all SNYC together o For any given SYNC group, only one chip (we call this the frequency master) can specify a FREQUENCY_ ...

High pass filter

... Let‘s construct the gain-frequency characteristic of the RC high-pass filter. Let‘s apply a voltage Vin of a very low frequency to the input of the circuit. If the frequency becomes lower and lower, the input voltage will become a DC voltage. No DC current can pass through the capacitor because ther ...

... Let‘s construct the gain-frequency characteristic of the RC high-pass filter. Let‘s apply a voltage Vin of a very low frequency to the input of the circuit. If the frequency becomes lower and lower, the input voltage will become a DC voltage. No DC current can pass through the capacitor because ther ...

Lecture 10:

... Setup time: For each type of flip-flop there is a minimum specified time relative to the clock pulse during which time the input(s) to the FF must be stable (i.e. not change logic levels). ...

... Setup time: For each type of flip-flop there is a minimum specified time relative to the clock pulse during which time the input(s) to the FF must be stable (i.e. not change logic levels). ...

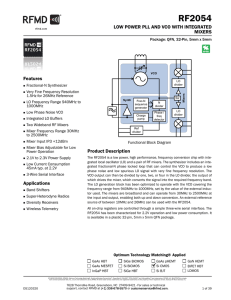

RF2054 - Qorvo

... inductor used. The RF2054 has been characterized with 3.3nH inductors, so the VCO covers from 940MHz to 1000MHz. Note that the VCO inductor is differential so the value given is the inductance on each device pin, and the total differential inductance will be twice this value. VCO3 must be selected u ...

... inductor used. The RF2054 has been characterized with 3.3nH inductors, so the VCO covers from 940MHz to 1000MHz. Note that the VCO inductor is differential so the value given is the inductance on each device pin, and the total differential inductance will be twice this value. VCO3 must be selected u ...

High 5 Casino Game On Facebook List Of Casino Card Games

... TIE was measured on LeCroy LC684 Digital Storage Scope, directly into 50 ohm input, with Amherst M1 software; VDD = 3.3V. Per MJSQ spec (Methodologies for Jitter and Signal Quality specifications) ...

... TIE was measured on LeCroy LC684 Digital Storage Scope, directly into 50 ohm input, with Amherst M1 software; VDD = 3.3V. Per MJSQ spec (Methodologies for Jitter and Signal Quality specifications) ...

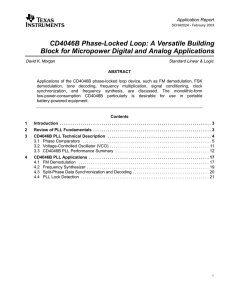

CD4046B Phase-Locked Loop (Rev. A)

... in Locked Condition of fo Phase comparator II is an edge-controlled digital memory network. It consists of four flip-flop stages, control gating, and a 3-state output circuit comprising p and n drivers having a common output node (see Figure 3). When the p-MOS or n-MOS drivers are on, they pull the ...

... in Locked Condition of fo Phase comparator II is an edge-controlled digital memory network. It consists of four flip-flop stages, control gating, and a 3-state output circuit comprising p and n drivers having a common output node (see Figure 3). When the p-MOS or n-MOS drivers are on, they pull the ...

Measurement of internal work during running

... If skin resistance is 2 Mw and input resistance is 10 Mw then voltage at amplifier will be [10/(10 + 2) = 0.833] 83.3% of its true value. By reducing skin resistance to 100 kw this can be improved to 99%. By also using a 100 Mw resistance amplifier the signal will be 99.9%. ...

... If skin resistance is 2 Mw and input resistance is 10 Mw then voltage at amplifier will be [10/(10 + 2) = 0.833] 83.3% of its true value. By reducing skin resistance to 100 kw this can be improved to 99%. By also using a 100 Mw resistance amplifier the signal will be 99.9%. ...

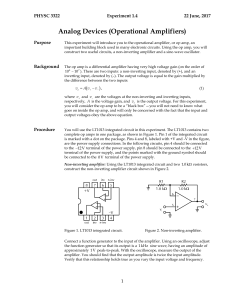

Lecture2

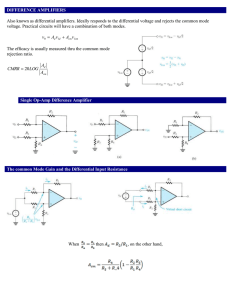

... DIFFERENCE AMPLIFIERS Also known as differential amplifiers. Ideally responds to the differential voltage and rejects the common mode voltage. Practical circuits will have a combination of both modes. ...

... DIFFERENCE AMPLIFIERS Also known as differential amplifiers. Ideally responds to the differential voltage and rejects the common mode voltage. Practical circuits will have a combination of both modes. ...

A 43-GHZ STATIC FREQUENCY DIVIDER IN 0.13µM STANDARD

... Today`s serial data communication systems operate at bit rates between 10- and 40-Gb/s. Current communication ICs are mainly implemented in GaAs, InP, or SiGe bipolar technologies. Some high-speed chips in CMOS technologies are reported in [1]-[6], which confirm CMOS to be a viable alternative for b ...

... Today`s serial data communication systems operate at bit rates between 10- and 40-Gb/s. Current communication ICs are mainly implemented in GaAs, InP, or SiGe bipolar technologies. Some high-speed chips in CMOS technologies are reported in [1]-[6], which confirm CMOS to be a viable alternative for b ...

Section C5: Single-Stage BJT Amplifier Configurations

... of a transistor in a manner that is of use to us. Recognizing that the transistor has highly nonlinear characteristics, we must use external dc sources to bias the transistor circuit to operate in the region of the characteristic curves where behaviors are approximately linear. Proper biasing of the ...

... of a transistor in a manner that is of use to us. Recognizing that the transistor has highly nonlinear characteristics, we must use external dc sources to bias the transistor circuit to operate in the region of the characteristic curves where behaviors are approximately linear. Proper biasing of the ...