±0.8% Accurate Quad UV/OV Positive/Negative Voltage Supervisor ADM12914

... Each monitored rail has two dedicated input pins, VHx and VLx, which allows each rail to be monitored for both undervoltage (UV) and overvoltage (OV) conditions with high threshold accuracy of ±0.8%. Common active low undervoltage (UV) and overvoltage (OV) pins are shared by each of the monitored vo ...

... Each monitored rail has two dedicated input pins, VHx and VLx, which allows each rail to be monitored for both undervoltage (UV) and overvoltage (OV) conditions with high threshold accuracy of ±0.8%. Common active low undervoltage (UV) and overvoltage (OV) pins are shared by each of the monitored vo ...

STPMS2

... Choose the current-to-voltage conversion ratio Ks and the voltage divider ratio in a way that calibration can be achieved ...

... Choose the current-to-voltage conversion ratio Ks and the voltage divider ratio in a way that calibration can be achieved ...

Document

... Superposition theorem states that in a linear bilateral network containing more than one source, the current flowing through the branch is the algebraic sum of the current flowing through that branch when sources are considered one at a time and replacing other sources by ...

... Superposition theorem states that in a linear bilateral network containing more than one source, the current flowing through the branch is the algebraic sum of the current flowing through that branch when sources are considered one at a time and replacing other sources by ...

Chapter 6 BUILDING A HOMEBREW QRP

... conducts) relatively large currents, (milliamperes), can pass through the diode. However, current will flow only when the forward offset voltage, (about 0.6 volts) is exceeded. Just like a diode, when a silicon NPN transistor is used, nothing significant will happen until the base voltage rises abov ...

... conducts) relatively large currents, (milliamperes), can pass through the diode. However, current will flow only when the forward offset voltage, (about 0.6 volts) is exceeded. Just like a diode, when a silicon NPN transistor is used, nothing significant will happen until the base voltage rises abov ...

BDTIC Stacks We are the experts for power systems

... Control electronics and the power connections are fully separated from each other by “reinforced isolation”. With several superior monitor functions, PrimeSTACK™ offers a self protecting switch function. PrimeSTACK™ enables the developement of highly efficient and safe inverters, quickly and with th ...

... Control electronics and the power connections are fully separated from each other by “reinforced isolation”. With several superior monitor functions, PrimeSTACK™ offers a self protecting switch function. PrimeSTACK™ enables the developement of highly efficient and safe inverters, quickly and with th ...

MAX8672 Complete Backup Management IC for NiMH Batteries General Description

... directly connected to the BST and LDO outputs, where LDO and BST are programmed to regulate just below system supply voltages. When system supply voltages exceed the programmed BST and LDO output voltage, BST and LDO are pulled up by the system supplies and do not sink current (BST sinks 80µA for ch ...

... directly connected to the BST and LDO outputs, where LDO and BST are programmed to regulate just below system supply voltages. When system supply voltages exceed the programmed BST and LDO output voltage, BST and LDO are pulled up by the system supplies and do not sink current (BST sinks 80µA for ch ...

Chapter 7 Input/Ouput Circuitry

... Such a voltage destroys MOS transistors, therefore, ESD protection is essential for the I/O circuitry. A typical solution of the ESD protection problem is to use clamping diodes implemented using MOS transistors with gates tied up to either GND for nMOS transistors, or to VDD for pMOS transistors as ...

... Such a voltage destroys MOS transistors, therefore, ESD protection is essential for the I/O circuitry. A typical solution of the ESD protection problem is to use clamping diodes implemented using MOS transistors with gates tied up to either GND for nMOS transistors, or to VDD for pMOS transistors as ...

2SK1056,2SK1057,2SK1058 Datasheet

... 1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration ...

... 1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration ...

CHAPTER 3: SiGe MONOLITHIC TECHNOLOGIES

... This chapter describes the two integrated circuit processes that were used in the verification of the designed LNAs. Full details of the process design kits (PDKs) cannot be disclosed due to a non-disclosure agreement (NDA) with the foundry; only those details already available in the public domain ...

... This chapter describes the two integrated circuit processes that were used in the verification of the designed LNAs. Full details of the process design kits (PDKs) cannot be disclosed due to a non-disclosure agreement (NDA) with the foundry; only those details already available in the public domain ...

11.3 Gbps, Active Back-Termination, Differential VCSEL Driver ADN2530

... reflections at the input that could otherwise lead to degradation in the output eye diagram. It is not recommended to drive the ADN2530 with single-ended data signal sources. The ADN2530 input stage must be ac-coupled to the signal source to eliminate the need for matching between the commonmode vol ...

... reflections at the input that could otherwise lead to degradation in the output eye diagram. It is not recommended to drive the ADN2530 with single-ended data signal sources. The ADN2530 input stage must be ac-coupled to the signal source to eliminate the need for matching between the commonmode vol ...

1818 Configuring a Resistor Network Production Test System with

... temperature-dependent offsets to the system. When testing highvolume, low-precision parts, the errors due to these offsets are not significant in the final results. However, if higher accuracy measurements are required, the Model 2400 can be configured for an enhanced ohms mode, which uses the offse ...

... temperature-dependent offsets to the system. When testing highvolume, low-precision parts, the errors due to these offsets are not significant in the final results. However, if higher accuracy measurements are required, the Model 2400 can be configured for an enhanced ohms mode, which uses the offse ...

RUQ050N02

... No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd. The content specified herein is subject to change for improvement without notice. The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products" ...

... No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd. The content specified herein is subject to change for improvement without notice. The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products" ...

PCM1702 数据资料 dataSheet 下载

... extremely linear output. The two DACs share a common reference, and a common R-2R ladder for bit current sources by dual balanced current segments to ensure perfect tracking under all conditions. By interleaving the individual bits of each DAC and employing precise laser trimming of resistors, the h ...

... extremely linear output. The two DACs share a common reference, and a common R-2R ladder for bit current sources by dual balanced current segments to ensure perfect tracking under all conditions. By interleaving the individual bits of each DAC and employing precise laser trimming of resistors, the h ...

LT1789-1/LT1789-10 - Micropower, Single Supply Rail-to-Rail Output Instrumentation Amplifier

... Note 5: Hysteresis in offset voltage is created by package stress that differs depending on whether the IC was previously at a higher or lower temperature. Offset voltage hysteresis is always measured at 25°C, but the IC is cycled to 85°C I-grade (or 70°C C-grade) or – 40°C I-grade (0°C C-grade) bef ...

... Note 5: Hysteresis in offset voltage is created by package stress that differs depending on whether the IC was previously at a higher or lower temperature. Offset voltage hysteresis is always measured at 25°C, but the IC is cycled to 85°C I-grade (or 70°C C-grade) or – 40°C I-grade (0°C C-grade) bef ...

FAN6208 Secondary-Side Synchronous Rectifier Controller for LLC Topology FAN

... To handle abnormal conditions for IC pins, the RP pin also provides open/short protection. When VRP is less than VRPS (0.3 V) or VRP is higher than VRPO (3.65 V), the protection is triggered. Figure 17 shows the RP pin short protection timing sequence. If VRP < VRPS (0.3 V) for longer than tRPOS (2 ...

... To handle abnormal conditions for IC pins, the RP pin also provides open/short protection. When VRP is less than VRPS (0.3 V) or VRP is higher than VRPO (3.65 V), the protection is triggered. Figure 17 shows the RP pin short protection timing sequence. If VRP < VRPS (0.3 V) for longer than tRPOS (2 ...

Transistor Structure

... electrons. This means pMOS transistor provide less current than nMOS transistor of comparable size and ...

... electrons. This means pMOS transistor provide less current than nMOS transistor of comparable size and ...

Temperature-, gate-, and photoinduced conductance of close

... +60 V than on the way down from +60 V to −60 V. Thus, the current apparently decays with time at these low temperatures; data points are taken every 10 s, giving a time scale to the hysteresis. For the I-V curves in the main part of Fig. 2 the data shown are for the voltage sweep from 0 V to +60 V a ...

... +60 V than on the way down from +60 V to −60 V. Thus, the current apparently decays with time at these low temperatures; data points are taken every 10 s, giving a time scale to the hysteresis. For the I-V curves in the main part of Fig. 2 the data shown are for the voltage sweep from 0 V to +60 V a ...

Oct-1968 - HP Labs

... designed to dry fast enough so they do not smudge by the time the user is ready to handle the record generally dry in the pen tip after being inoperative a few minutes to a few days. It is not uncommon to find water based inks still in use in capillary pen systems. A coffee spill on a record of this ...

... designed to dry fast enough so they do not smudge by the time the user is ready to handle the record generally dry in the pen tip after being inoperative a few minutes to a few days. It is not uncommon to find water based inks still in use in capillary pen systems. A coffee spill on a record of this ...

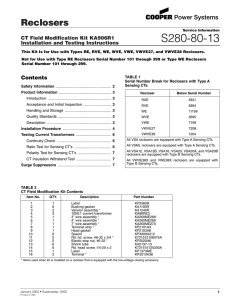

S280-80-13

... 1. With the phases still connected in series from the previous test, connect the secondaries of the CT’s in parallel by connecting pin socket G to H to J and measure the output between pin sockets K and J as shown in Figure 8 (Ratio-Test Circuit B). 2. Energize the 100 ampere ac test source. ...

... 1. With the phases still connected in series from the previous test, connect the secondaries of the CT’s in parallel by connecting pin socket G to H to J and measure the output between pin sockets K and J as shown in Figure 8 (Ratio-Test Circuit B). 2. Energize the 100 ampere ac test source. ...

Paper 1

... IBIAS was determined. Equation 3 was used to determine the positive and negative modulation current that carries the signal. ...

... IBIAS was determined. Equation 3 was used to determine the positive and negative modulation current that carries the signal. ...