Cell

... PPE can load and store from a memory location mapped to the local store (slow) SPE can use the DMA controller to move data to its own or other SPEs local store & between local store and main memory as well as I/O interfaces Memory flow controller on SPE can begin to transfer the data set of the next ...

... PPE can load and store from a memory location mapped to the local store (slow) SPE can use the DMA controller to move data to its own or other SPEs local store & between local store and main memory as well as I/O interfaces Memory flow controller on SPE can begin to transfer the data set of the next ...

Conclusions

... 1- Execution time very fast where each instruction takes a single cycle 2- Number of instructions very minimal As an example: PIC16Cx5x only 33 instructions ...

... 1- Execution time very fast where each instruction takes a single cycle 2- Number of instructions very minimal As an example: PIC16Cx5x only 33 instructions ...

test - Microchip

... Provides a bidirectional, half-duplex communication physical interface to an automotive and industrial Local Interconnect (LIN) and SAE J2602 bus. Operation covers LIN Bus Specification Versions 1.3, 2.0, 2.1 and SAE J2602. The device incorporates a voltage regulator with 5V/70mA or 3.3V/70mA output ...

... Provides a bidirectional, half-duplex communication physical interface to an automotive and industrial Local Interconnect (LIN) and SAE J2602 bus. Operation covers LIN Bus Specification Versions 1.3, 2.0, 2.1 and SAE J2602. The device incorporates a voltage regulator with 5V/70mA or 3.3V/70mA output ...

CS61C / CS150 in the News Review: I/O Working with real devices

... • CPU has sole control over main memory • Not ideal since… – CPU has to execute all transfers, could be doing other work – Device speeds don’t align well with CPU speeds – Energy cost of using ...

... • CPU has sole control over main memory • Not ideal since… – CPU has to execute all transfers, could be doing other work – Device speeds don’t align well with CPU speeds – Energy cost of using ...

What are the three basic LAN topologies? 2. What common WAN

... What network model draws a clear distinction between devices that share their resources and devices that do not? ...

... What network model draws a clear distinction between devices that share their resources and devices that do not? ...

ppt - shtech.org

... – Seek Time = time to position the head assembly at the proper cylinder – Rotation Time = time for the disk to rotate to the point where the first sectors of the block to access reach the head – Transfer Time = time taken by the sectors of the block and any gaps between them to rotate past the head ...

... – Seek Time = time to position the head assembly at the proper cylinder – Rotation Time = time for the disk to rotate to the point where the first sectors of the block to access reach the head – Transfer Time = time taken by the sectors of the block and any gaps between them to rotate past the head ...

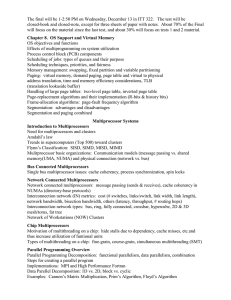

The final will be 1-2:50 PM on Wednesday, December 13... closed-book and closed-note, except for three sheets of paper with...

... The final will be 1-2:50 PM on Wednesday, December 13 in ITT 322. The test will be closed-book and closed-note, except for three sheets of paper with notes. About 70% of the Final will focus on the material since the last test, and about 30% will focus on tests 1 and 2 material. Chapter 8. OS Suppor ...

... The final will be 1-2:50 PM on Wednesday, December 13 in ITT 322. The test will be closed-book and closed-note, except for three sheets of paper with notes. About 70% of the Final will focus on the material since the last test, and about 30% will focus on tests 1 and 2 material. Chapter 8. OS Suppor ...

CSCI 200 Final Exam

... color. What is the total amount of memory used for the frame buffer? 4. A company is planning to use a 200 watt power supply in a computer whose mother board and disk drives need 35A at +5V, and 10A at +12V in total. Will this work? Why or why not? 5. Name and describe three ways of storing settings ...

... color. What is the total amount of memory used for the frame buffer? 4. A company is planning to use a 200 watt power supply in a computer whose mother board and disk drives need 35A at +5V, and 10A at +12V in total. Will this work? Why or why not? 5. Name and describe three ways of storing settings ...

SERIAL BUS COMMUNICATION PROTOCOLS

... Identifies(11 bits) the device to which data is being sent or request is being made. When RTR bit is at '1', it means this packet is for the device at destination address. If this bit is at '0' (dominant state) it means, this packet is a request for the data from the device. ...

... Identifies(11 bits) the device to which data is being sent or request is being made. When RTR bit is at '1', it means this packet is for the device at destination address. If this bit is at '0' (dominant state) it means, this packet is a request for the data from the device. ...

Network on Chip - Architectures and Design Methodology

... • Adds state to end-to-end connections. ...

... • Adds state to end-to-end connections. ...

NP_ch04

... Processors continue to increase in speed Some conventional hardware present in all systems ...

... Processors continue to increase in speed Some conventional hardware present in all systems ...

Java Methods 2nd AP edition

... CPU registers from memory and storing their values in memory for logical and arithmetic operations, and for altering the sequence of ...

... CPU registers from memory and storing their values in memory for logical and arithmetic operations, and for altering the sequence of ...

netX 50 – networX on chip The future of communication

... MHz and has 112 KB internal RAM and 64 KByte ROM memory. The memory can be expanded flexible by the 32-Bit memory controller with SDRAM, SRAM or FLASH externally. Extensive periphery functions, serial interfaces such as UART, USB, SPI, I²C, as well as the integrated IO-Link and CCD controller allows ...

... MHz and has 112 KB internal RAM and 64 KByte ROM memory. The memory can be expanded flexible by the 32-Bit memory controller with SDRAM, SRAM or FLASH externally. Extensive periphery functions, serial interfaces such as UART, USB, SPI, I²C, as well as the integrated IO-Link and CCD controller allows ...

Mid Semester Presentation - High Speed Digital Systems Laboratory

... Redundancy Using network creates several paths between each two devices, which helps error handling CPU Memory ...

... Redundancy Using network creates several paths between each two devices, which helps error handling CPU Memory ...

Polytel® Remote Data Termininal (RDT)

... • Store and Forward with up to 500kB or connected mode - Reliable transfer of intermittent data and sufficient space for new features ...

... • Store and Forward with up to 500kB or connected mode - Reliable transfer of intermittent data and sufficient space for new features ...

Low Pin Count

The Low Pin Count bus, or LPC bus, is used on IBM-compatible personal computers to connect low-bandwidth devices to the CPU, such as the boot ROM, ""legacy"" I/O devices (integrated into a super I/O chip), and Trusted Platform Module (TPM). ""Legacy"" I/O devices usually include serial and parallel ports, PS/2 keyboard, PS/2 mouse, and floppy disk controller.Most PC motherboards with a LPC bus have either a Platform Controller Hub (PCH) or a southbridge chip, which acts as the host and controls the LPC bus. All other devices connected to the physical wires of the LPC bus are peripherals.