DYNAMIC LOGIC

... Non-ratioed - sizing of the devices does not affect the logic levels Faster switching speeds » reduced load capacitance due to lower input capacitance (Cin) » reduced load capacitance due to smaller output loading (Cout) » no Isc, so all the current provided by PDN goes into discharging CL ...

... Non-ratioed - sizing of the devices does not affect the logic levels Faster switching speeds » reduced load capacitance due to lower input capacitance (Cin) » reduced load capacitance due to smaller output loading (Cout) » no Isc, so all the current provided by PDN goes into discharging CL ...

A Vernier Time-to-Digital Converter With Delay Latch Chain Architecture

... pump and the analog loop filters can be replaced with digital filters and a digital control loop. In the PLL case, the inputs to the TDC are two clock signals which is the notation we will use in this work. In this work we propose a new Vernier TDC architecture enabling both power and area improveme ...

... pump and the analog loop filters can be replaced with digital filters and a digital control loop. In the PLL case, the inputs to the TDC are two clock signals which is the notation we will use in this work. In this work we propose a new Vernier TDC architecture enabling both power and area improveme ...

Document

... Branch One current path in a parallel circuit. Kirchhoff’s A law stating the total current into a node current law equals the total current out of the node. Node A point or junction in a circuit at which two or more components are connected. Current divider A parallel circuit in which the currents d ...

... Branch One current path in a parallel circuit. Kirchhoff’s A law stating the total current into a node current law equals the total current out of the node. Node A point or junction in a circuit at which two or more components are connected. Current divider A parallel circuit in which the currents d ...

chapter 1 - UniMAP Portal

... It is very difficult to design electronic equipment so that it can work with 10 different voltage levels (each one representing one decimal character, 0 through 9). On the other hand, it is very easy to design simple, accurate electronic circuits that operate with only two voltage levels. Almost eve ...

... It is very difficult to design electronic equipment so that it can work with 10 different voltage levels (each one representing one decimal character, 0 through 9). On the other hand, it is very easy to design simple, accurate electronic circuits that operate with only two voltage levels. Almost eve ...

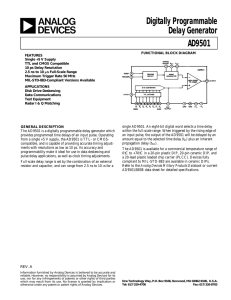

AD9501 Digitally Programmable Delay Generator

... (time skew) occurs, errors can occur during data transfer. For these situations, the matching of delays is generally accomplished by carefully matching lead lengths. ...

... (time skew) occurs, errors can occur during data transfer. For these situations, the matching of delays is generally accomplished by carefully matching lead lengths. ...

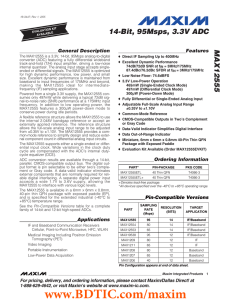

MAX12555 14-Bit, 95Msps, 3.3V ADC General Description Features

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.10V. The MAX12555 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX12555 supports either a single-ended or differential input clock. Wide var ...

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.10V. The MAX12555 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX12555 supports either a single-ended or differential input clock. Wide var ...

MAX1209 12-Bit, 80Msps, 3.3V IF-Sampling ADC General Description Features

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.15V. The MAX1209 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX1209 supports both a single-ended and differential input clock drive. Wide ...

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.15V. The MAX1209 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX1209 supports both a single-ended and differential input clock drive. Wide ...

MAX1208 12-Bit, 80Msps, 3.3V ADC General Description Features

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.15V. The MAX1208 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX1208 supports both a single-ended and differential input clock drive. Wide ...

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.15V. The MAX1208 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX1208 supports both a single-ended and differential input clock drive. Wide ...

Lecture 2: CMOS and Manufacturing Process

... 1. At every point in time (except during the switching transients) each gate output is connected to either VDD or Vssvia a low-resistive path. 2. The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects du ...

... 1. At every point in time (except during the switching transients) each gate output is connected to either VDD or Vssvia a low-resistive path. 2. The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects du ...

Effects of Smoke on Functional Circuits NUREG/CR-6543 SAND97-2544

... The high-speed digital circuit was not affected by smoke, even at the highest fuel level. The main component tested in this circuit was an advanced TTL (FAST) chip. An experiment that compared the failure of chip technologies in the presence of a shunt resistance showed that a FAST chip is one of th ...

... The high-speed digital circuit was not affected by smoke, even at the highest fuel level. The main component tested in this circuit was an advanced TTL (FAST) chip. An experiment that compared the failure of chip technologies in the presence of a shunt resistance showed that a FAST chip is one of th ...

Design Techniques for EMC, 2006 series

... Reduced levels of power supply transients. When ‘totem-pole’ circuits in ICs change state, they pass through a brief period when both upper and lower devices are on at the same time, momentarily shorting the supply rail. The resulting power supply current transient (sometimes called ‘shoot-through’) ...

... Reduced levels of power supply transients. When ‘totem-pole’ circuits in ICs change state, they pass through a brief period when both upper and lower devices are on at the same time, momentarily shorting the supply rail. The resulting power supply current transient (sometimes called ‘shoot-through’) ...

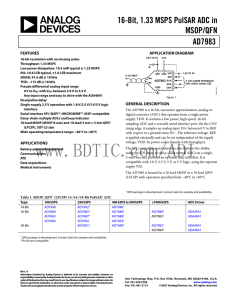

MAX19538 12-Bit, 95Msps, 3.3V ADC General Description Features

... low-noise internal quantizer. The analog input accepts single-ended or differential signals. The MAX19538 is optimized for low power, small size, and high dynamic performance. Excellent dynamic performance is maintained from baseband to input frequencies of 175MHz and beyond, making the MAX19538 ide ...

... low-noise internal quantizer. The analog input accepts single-ended or differential signals. The MAX19538 is optimized for low power, small size, and high dynamic performance. Excellent dynamic performance is maintained from baseband to input frequencies of 175MHz and beyond, making the MAX19538 ide ...

Quad-Channel Digital Isolators / ADuM1400

... current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects are eliminated with the simple iCoupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these iCoupler products. Furth ...

... current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects are eliminated with the simple iCoupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these iCoupler products. Furth ...

Leakage Current Reduction in CMOS VLSI Circuits by Input Vector

... the length of transistors increases the leakage current as well. Therefore, in a chip, transistors that have smaller threshold voltage and/or length due to process variation, contribute more to the overall leakage. Although previously the leakage current was important only in systems with long inact ...

... the length of transistors increases the leakage current as well. Therefore, in a chip, transistors that have smaller threshold voltage and/or length due to process variation, contribute more to the overall leakage. Although previously the leakage current was important only in systems with long inact ...

Digital Electronics Demystified - (Malestrom)

... of this effort was to reduce the electronic logic ‘‘truths’’ into two simple electrical states. These two electrical states are often represented as two numbers that can be manipulated using ‘‘binary arithmetic.’’ Binary arithmetic was formally described by the English mathematician George Boole in t ...

... of this effort was to reduce the electronic logic ‘‘truths’’ into two simple electrical states. These two electrical states are often represented as two numbers that can be manipulated using ‘‘binary arithmetic.’’ Binary arithmetic was formally described by the English mathematician George Boole in t ...

single output cdm standard cell library design

... performance improvement. Synopsys silicon smart and library compiler tool has been used to generate the standard cell libraries using FinFET device models from PTM and design compiler to synthesize the designs with developed standard cell libraries. The simulation results shows that CDM based standa ...

... performance improvement. Synopsys silicon smart and library compiler tool has been used to generate the standard cell libraries using FinFET device models from PTM and design compiler to synthesize the designs with developed standard cell libraries. The simulation results shows that CDM based standa ...

Digital electronics

Digital electronics or digital (electronic) circuits are electronics that handle digital signals- discrete bands of analog levels, rather than by continuous ranges (as used in analogue electronics). All levels within a band of values represent the same numeric value. Because of this discretization, relatively small changes to the analog signal levels due to manufacturing tolerance, signal attenuation or parasitic noise do not leave the discrete envelope, and as a result are ignored by signal state sensing circuitry.In most cases the number of these states is two, and they are represented by two voltage bands: one near a reference value (typically termed as ""ground"" or zero volts), and the other a value near the supply voltage. These correspond to the ""false"" (""0"") and ""true"" (""1"") values of the Boolean domain, respectively, yielding binary code.Digital techniques are useful because it is easier to get an electronic device to switch into one of a number of known states than to accurately reproduce a continuous range of values.Digital electronic circuits are usually made from large assemblies of logic gates, simple electronic representations of Boolean logic functions.