Lecture_13_LP_RTL_95

... design no clock during the test phase – One way to improve the testability of the design is to insert a control point, which is an OR gate controlled by an additional signal scan_mode. – Its task is to eliminate the function of the clock gate during the test phase and thus restores the controllabi ...

... design no clock during the test phase – One way to improve the testability of the design is to insert a control point, which is an OR gate controlled by an additional signal scan_mode. – Its task is to eliminate the function of the clock gate during the test phase and thus restores the controllabi ...

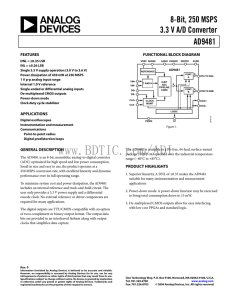

8-Bit, 250 MSPS 3.3 V A/D Converter AD9481

... (ADC) optimized for high speed and low power consumption. Small in size and easy to use, the product operates at a 250 MSPS conversion rate, with excellent linearity and dynamic performance over its full operating range. To minimize system cost and power dissipation, the AD9481 includes an internal ...

... (ADC) optimized for high speed and low power consumption. Small in size and easy to use, the product operates at a 250 MSPS conversion rate, with excellent linearity and dynamic performance over its full operating range. To minimize system cost and power dissipation, the AD9481 includes an internal ...

8-Bit, 250 MSPS 3.3 V A/D Converter AD9480

... To minimize system cost and power dissipation, the AD9480 includes an internal reference and track-and-hold circuit. The user only provides a 3.3 V power supply and a differential encode clock. No external reference or driver components are required for many applications. The digital outputs are LVD ...

... To minimize system cost and power dissipation, the AD9480 includes an internal reference and track-and-hold circuit. The user only provides a 3.3 V power supply and a differential encode clock. No external reference or driver components are required for many applications. The digital outputs are LVD ...

Lecture 16: Pitfalls & Reliability

... – Avoid unbuffered diffusion inputs where driver is unknown 16: Circuit Pitfalls ...

... – Avoid unbuffered diffusion inputs where driver is unknown 16: Circuit Pitfalls ...

Circuit Pitfalls

... – Avoid unbuffered diffusion inputs where driver is unknown 16: Circuit Pitfalls ...

... – Avoid unbuffered diffusion inputs where driver is unknown 16: Circuit Pitfalls ...

AD5222 数据手册DataSheet 下载

... active inputs are clock (CLK), CS and up/down (U/D). While the MODE, and DACSEL pins control common updates or individual updates. The negative-edge sensitive CLK input requires clean transitions to avoid clocking multiple pulses into the internal UP/DOWN counter register, Figure 30. Standard logic ...

... active inputs are clock (CLK), CS and up/down (U/D). While the MODE, and DACSEL pins control common updates or individual updates. The negative-edge sensitive CLK input requires clean transitions to avoid clocking multiple pulses into the internal UP/DOWN counter register, Figure 30. Standard logic ...

ADC0802, ADC0803 ADC0804

... (19.53mV with 2.5V tied to the VREF/2 pin). The digital output codes which correspond to these inputs are shown as D-1, D, and D+1. For the perfect A/D, not only will center-value (A - 1, A, A + 1, . . .) analog inputs produce the correct output digital codes, but also each riser (the transitions be ...

... (19.53mV with 2.5V tied to the VREF/2 pin). The digital output codes which correspond to these inputs are shown as D-1, D, and D+1. For the perfect A/D, not only will center-value (A - 1, A, A + 1, . . .) analog inputs produce the correct output digital codes, but also each riser (the transitions be ...

Low-power Sequential Circuit Design Using T

... ✝✝ Department of Electrical Engineering-Systems, University of Southern California, Los Angeles, USA. ...

... ✝✝ Department of Electrical Engineering-Systems, University of Southern California, Los Angeles, USA. ...

3. Preformance of CMOS Circuits

... – Approaches subthreshold leakage at 65 nm and below in some processes An order of magnitude less for pMOS than nMOS Control leakage in the process using tox > 10.5 Å – High-k gate dielectrics help ...

... – Approaches subthreshold leakage at 65 nm and below in some processes An order of magnitude less for pMOS than nMOS Control leakage in the process using tox > 10.5 Å – High-k gate dielectrics help ...

G7 - PRACTICAL CIRCUITS [2 exam question - 2 groups]

... Symbol 6 B. Symbol 4 C. Symbol 10 D. symbol 2 ...

... Symbol 6 B. Symbol 4 C. Symbol 10 D. symbol 2 ...

DET: Technological Studies

... The purpose of this unit of work is to introduce student to simple electronic control systems based on voltage dividers and bi-polar transistors. The circuits should be able to control output devices and component protection is introduced. Student activities include calculations relating to voltage ...

... The purpose of this unit of work is to introduce student to simple electronic control systems based on voltage dividers and bi-polar transistors. The circuits should be able to control output devices and component protection is introduced. Student activities include calculations relating to voltage ...

40-Gb/s Transimpedance Amplifier in 0.18

... CS stage first in this section, which is the fundamental building block and will be applied directly to the proposed wideband TIA using a four-stage cascade configuration. Fig. 1 shows a simplified small-signal equivalent circuit model of a CS stage including the PIP inductors (Ld1, Ls1, and Ld2), w ...

... CS stage first in this section, which is the fundamental building block and will be applied directly to the proposed wideband TIA using a four-stage cascade configuration. Fig. 1 shows a simplified small-signal equivalent circuit model of a CS stage including the PIP inductors (Ld1, Ls1, and Ld2), w ...

Unit iii – ic 741 OP-AMP - AJAY KUMAR GAUTAM

... Figure 1: The 741 op-amp circuit. Q11, Q12, and R5 generate a reference bias current, IREF. Q10, Q9, and Q8 bias the input stage, which is composed of Q1 to Q7. The second gain stage is composed of Q16 and Q17 with Q13B acting as active load. The class AB output stage is formed by Q14 and Q20 with b ...

... Figure 1: The 741 op-amp circuit. Q11, Q12, and R5 generate a reference bias current, IREF. Q10, Q9, and Q8 bias the input stage, which is composed of Q1 to Q7. The second gain stage is composed of Q16 and Q17 with Q13B acting as active load. The class AB output stage is formed by Q14 and Q20 with b ...

G7 - PRACTICAL CIRCUITS [2 exam question - 2

... B. The binary number system is most accurate C. Binary numbers are more compatible with analog circuitry D. All of these answers are correct ...

... B. The binary number system is most accurate C. Binary numbers are more compatible with analog circuitry D. All of these answers are correct ...

UNIT-3 (1) - WordPress.com

... Now, if Q = 0 and R = 1, then these are the states of inputs of gate B, therefore the outputs of gate B is at 1 (making it the inverse of Q i.e. 0). The output of gate B is connected to an input of gate A so if S = 1, both inputs of gate A are at the logic 1 state. This means that the output of gat ...

... Now, if Q = 0 and R = 1, then these are the states of inputs of gate B, therefore the outputs of gate B is at 1 (making it the inverse of Q i.e. 0). The output of gate B is connected to an input of gate A so if S = 1, both inputs of gate A are at the logic 1 state. This means that the output of gat ...

Chapter 8 Integrated-Circuit Logic Families

... Ronald J. Tocci, Neal S. Widmer, Gregory L. Moss ...

... Ronald J. Tocci, Neal S. Widmer, Gregory L. Moss ...

Slide 1 - Oxford University Press

... ground) realize the function Y = ABC. (b) When the two switches are connected in parallel, the function realized is Y = A(B + C). Microelectronic Circuits, Sixth Edition ...

... ground) realize the function Y = ABC. (b) When the two switches are connected in parallel, the function realized is Y = A(B + C). Microelectronic Circuits, Sixth Edition ...

2 CMOS VLSI Design

... Collisions with particles create electron-hole pairs in substrate – These carriers are collected on dynamic nodes, disturbing the voltage Minimize soft errors by having plenty of charge on dynamic nodes Tolerate errors through ECC (Error Correcting Code), redundancy CMOS VLSI Design ...

... Collisions with particles create electron-hole pairs in substrate – These carriers are collected on dynamic nodes, disturbing the voltage Minimize soft errors by having plenty of charge on dynamic nodes Tolerate errors through ECC (Error Correcting Code), redundancy CMOS VLSI Design ...

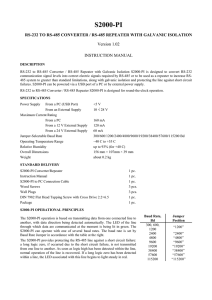

S2000-PI

... another, with data direction being detected automatically. The LED of the line through which data are communicated at the moment is being lit in green. The S2000-PI can operate with one of several baud rates. The baud rate is set by Baud Rate Jumper in accordance with the table at the right. The S20 ...

... another, with data direction being detected automatically. The LED of the line through which data are communicated at the moment is being lit in green. The S2000-PI can operate with one of several baud rates. The baud rate is set by Baud Rate Jumper in accordance with the table at the right. The S20 ...

Digital electronics

Digital electronics or digital (electronic) circuits are electronics that handle digital signals- discrete bands of analog levels, rather than by continuous ranges (as used in analogue electronics). All levels within a band of values represent the same numeric value. Because of this discretization, relatively small changes to the analog signal levels due to manufacturing tolerance, signal attenuation or parasitic noise do not leave the discrete envelope, and as a result are ignored by signal state sensing circuitry.In most cases the number of these states is two, and they are represented by two voltage bands: one near a reference value (typically termed as ""ground"" or zero volts), and the other a value near the supply voltage. These correspond to the ""false"" (""0"") and ""true"" (""1"") values of the Boolean domain, respectively, yielding binary code.Digital techniques are useful because it is easier to get an electronic device to switch into one of a number of known states than to accurately reproduce a continuous range of values.Digital electronic circuits are usually made from large assemblies of logic gates, simple electronic representations of Boolean logic functions.

![G7 - PRACTICAL CIRCUITS [2 exam question - 2 groups]](http://s1.studyres.com/store/data/005387230_1-76f563a4545dbc8ee3b6675916804d53-300x300.png)