STFI20NK50Z

... 2. Pulse width limited by safe operating area. 3. ISD < 17 A, di/dt < 200 A/µs, VDD =80% V(BR)DSS ...

... 2. Pulse width limited by safe operating area. 3. ISD < 17 A, di/dt < 200 A/µs, VDD =80% V(BR)DSS ...

experiment 6 - Portal UniMAP

... 3. Become aware of an experimental procedure to determine Vth, IN and Rth or RN. INTRODUCTION The Thevenin equivalent method allows you to replace any circuit consisting of independent sources, dependent sources, and resistors with a simple circuit consisting of a single voltage source in series wit ...

... 3. Become aware of an experimental procedure to determine Vth, IN and Rth or RN. INTRODUCTION The Thevenin equivalent method allows you to replace any circuit consisting of independent sources, dependent sources, and resistors with a simple circuit consisting of a single voltage source in series wit ...

Chapter 27-Circuits Multi-Resistor Single Loop Circuits Q1. A battery

... Q14. A capacitor in an RC circuit is charged to 85% of its maximum value in 2.4 s. What is the time constant of this circuit?Ans:1.3 s Q15. A 4.00 micro-F capacitor is charged to 24.0 V. Find the charge on the capacitor 4.00 milli-seconds after it is connected across a 200-Ohm resistor.Ans:0.647 mic ...

... Q14. A capacitor in an RC circuit is charged to 85% of its maximum value in 2.4 s. What is the time constant of this circuit?Ans:1.3 s Q15. A 4.00 micro-F capacitor is charged to 24.0 V. Find the charge on the capacitor 4.00 milli-seconds after it is connected across a 200-Ohm resistor.Ans:0.647 mic ...

Lab-18-(Circuit Analysis)

... total quantity of charge leaving the junction each second. If this were not true, charge would accumulate on the junction. Since like charges repel, this is unlikely and could not be sustained unless a separate energy source were available to constrain the charges to the node. This is the origin of ...

... total quantity of charge leaving the junction each second. If this were not true, charge would accumulate on the junction. Since like charges repel, this is unlikely and could not be sustained unless a separate energy source were available to constrain the charges to the node. This is the origin of ...

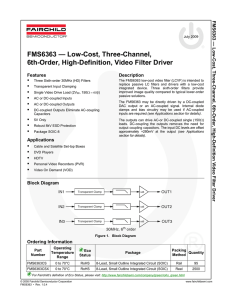

FMS6363 — Low-Cost, Three-Channel, 6th-Order, High-Definition, Video Filter Driver FM S6363 — Low-

... The FMS6363 outputs will be DC offset from the input by 150mv therefore VOUT = 2*VIN DC+150mv. This offset is required to obtain optimal performance from the output driver and is held at the minimum value in order to decrease the standing DC current into the load. Since the FMS6363 has a 2x (6dB) ga ...

... The FMS6363 outputs will be DC offset from the input by 150mv therefore VOUT = 2*VIN DC+150mv. This offset is required to obtain optimal performance from the output driver and is held at the minimum value in order to decrease the standing DC current into the load. Since the FMS6363 has a 2x (6dB) ga ...

physics 201 - La Salle University

... under the logic gates. The 7408 chip is a quad 2-input AND chip. That means that it contains four AND gates. For example, 1A and 1B are the inputs for the first AND gate, and 1Y is the corresponding output. An important distinction between the gates we used above and the chips we use in this section ...

... under the logic gates. The 7408 chip is a quad 2-input AND chip. That means that it contains four AND gates. For example, 1A and 1B are the inputs for the first AND gate, and 1Y is the corresponding output. An important distinction between the gates we used above and the chips we use in this section ...

OP290 数据手册DataSheet 下载

... An example of this is a transducer output where a change of temperature or pressure cannot exceed a certain rate due to physical limitations of the environment. The filter consists of a comparator which drives an integrator. The comparator compares the input voltage to the output voltage and forces ...

... An example of this is a transducer output where a change of temperature or pressure cannot exceed a certain rate due to physical limitations of the environment. The filter consists of a comparator which drives an integrator. The comparator compares the input voltage to the output voltage and forces ...

High Voltage Current Shunt Monitor AD8212

... (Pin 6) of the AD8212. The current flowing in this path is mirrored inside the current compensation circuit. This current then flows in Resistor R2, which is the same value as Resistor R1. The voltage created by this current across Resistor R2, displaces the noninverting input of Amplifier A1 by the ...

... (Pin 6) of the AD8212. The current flowing in this path is mirrored inside the current compensation circuit. This current then flows in Resistor R2, which is the same value as Resistor R1. The voltage created by this current across Resistor R2, displaces the noninverting input of Amplifier A1 by the ...

mobile bug. errors and trouble shooting

... Correction. Check the base voltage of transistor. It should be below 0.6 volts in stand by state and around 2 -4 volts when IC1 gives high output. If not, correct the front end. If base voltage is OK, then check the collector voltage. It should be high in the off state. If it is low, transistor is ...

... Correction. Check the base voltage of transistor. It should be below 0.6 volts in stand by state and around 2 -4 volts when IC1 gives high output. If not, correct the front end. If base voltage is OK, then check the collector voltage. It should be high in the off state. If it is low, transistor is ...

Mesh Analysis

... 4.If circuit contain only voltage sources apply kvl around each mesh If circuit has only independent voltage source .equate the clockwise sum of all resistance voltage to counter clockwise sum of all source voltage and order the terms of I1 to Im. For each dependent voltage source present ,relate t ...

... 4.If circuit contain only voltage sources apply kvl around each mesh If circuit has only independent voltage source .equate the clockwise sum of all resistance voltage to counter clockwise sum of all source voltage and order the terms of I1 to Im. For each dependent voltage source present ,relate t ...

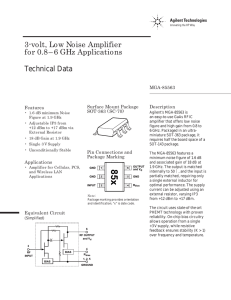

3-volt, Low Noise Amplifier for 0.8 – 6 GHz Applications Technical Data MGA-85563

... While the RF input terminal of the MGA-85563 is at DC ground potential, it should not be used as a current sink. If the input is connected directly to a preceding stage that has a DC voltage present, a blocking capacitor (C1) should be used. Setting the Bias Current for Higher Linearity The MGA-8556 ...

... While the RF input terminal of the MGA-85563 is at DC ground potential, it should not be used as a current sink. If the input is connected directly to a preceding stage that has a DC voltage present, a blocking capacitor (C1) should be used. Setting the Bias Current for Higher Linearity The MGA-8556 ...

Lab 13

... (VDS) voltages are equal. The two FETs are therefore operating in the saturation region since VDS > VGS VT (remember that VT > 0 for these FETs and VDS = VGS for this configuration). For identical FET devices VGS1 = VGS2 = - VSS/2 since, by KCL, ID1 = ID2 = K (W/L) (VGS - VT)2. It is interesting to ...

... (VDS) voltages are equal. The two FETs are therefore operating in the saturation region since VDS > VGS VT (remember that VT > 0 for these FETs and VDS = VGS for this configuration). For identical FET devices VGS1 = VGS2 = - VSS/2 since, by KCL, ID1 = ID2 = K (W/L) (VGS - VT)2. It is interesting to ...

Dual Bipolar/JFET, Audio Operational Amplifier OP275 *

... connected across its inputs. They limit the maximum differential input voltage to ±7.5 V. This is to prevent emitter-base junction breakdown from occurring in the input stage of the OP275 when very large differential voltages are applied. However, to preserve the OP275’s low input noise voltage, int ...

... connected across its inputs. They limit the maximum differential input voltage to ±7.5 V. This is to prevent emitter-base junction breakdown from occurring in the input stage of the OP275 when very large differential voltages are applied. However, to preserve the OP275’s low input noise voltage, int ...

STS11NF30L

... Figure 15. Test circuit for inductive load Figure 16. Unclamped Inductive load test switching and diode recovery times circuit ...

... Figure 15. Test circuit for inductive load Figure 16. Unclamped Inductive load test switching and diode recovery times circuit ...

A NOVELL METHOD OF ELECTRONIC TECHNIQUES FOR SOLVING HIGH

... and settling the parameters of DAC. 2.2. Creating a structure of components At the beginning there were ideas of a control-structure. The ideas have a range from one microcontroller for all to one for each channel or substitute microcontrollers for CPLD or FPGA. The founded concept is based on short ...

... and settling the parameters of DAC. 2.2. Creating a structure of components At the beginning there were ideas of a control-structure. The ideas have a range from one microcontroller for all to one for each channel or substitute microcontrollers for CPLD or FPGA. The founded concept is based on short ...