Integrated Design

... as shown in the following diagram to trigger a timer1 event. In our case, we connected a trimpot in place of R4 to fine tune the capacitance meter for accuracy. Since R2 will be known, we can get C because the voltage on the capacitor, v(t)=Vcc(1-exp(-t/τ)) with τ=(R2)*C. We used an analog DEMUX to ...

... as shown in the following diagram to trigger a timer1 event. In our case, we connected a trimpot in place of R4 to fine tune the capacitance meter for accuracy. Since R2 will be known, we can get C because the voltage on the capacitor, v(t)=Vcc(1-exp(-t/τ)) with τ=(R2)*C. We used an analog DEMUX to ...

Picture Coming Soon

... by Aimtec; refer to www.aimtec.com for the most current product specifications. 2. Product labels shown, including safety agency certifications on labels, may vary based on the date manufactured. 3. Mechanical drawings and specifications are for reference only. 4. All specifications are measured at ...

... by Aimtec; refer to www.aimtec.com for the most current product specifications. 2. Product labels shown, including safety agency certifications on labels, may vary based on the date manufactured. 3. Mechanical drawings and specifications are for reference only. 4. All specifications are measured at ...

figure 10-1

... Each of the four output signals will represent a different Duty Cycle, . For example, Output A is Logic 1 for 1/8 of the modulation period and thus = 0.125. Output C is Logic 1 for ½ the period and = 0.5. You may use TTL chips or any other, so long as they will work with Vcc = 5 Volts. Test the ...

... Each of the four output signals will represent a different Duty Cycle, . For example, Output A is Logic 1 for 1/8 of the modulation period and thus = 0.125. Output C is Logic 1 for ½ the period and = 0.5. You may use TTL chips or any other, so long as they will work with Vcc = 5 Volts. Test the ...

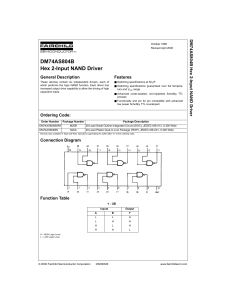

DM74AS804B Hex 2-Input NAND Driver

... These devices contain six independent drivers, each of which performs the logic NAND function. Each driver has increased output drive capability to allow the driving of high capacitive loads. ...

... These devices contain six independent drivers, each of which performs the logic NAND function. Each driver has increased output drive capability to allow the driving of high capacitive loads. ...

Application of Programmable Unijunction Transistor for - icmcs-2014

... even with an increase in the output current through the load of transistor (Figure 2). Only the turn off transistor or opening the circuit can remove the input voltage [2]. ...

... even with an increase in the output current through the load of transistor (Figure 2). Only the turn off transistor or opening the circuit can remove the input voltage [2]. ...

High Speed Arithmetic Design Using CPL and DPL Logic

... nel the filter is symmetric with the inner pair of taps adapting (Fig. 1); in the 250mb/s channel the filter is asymmetric with 4 taps adapting. System considerations also constrain the latency through the filter preventing free pipelining. These requirements place great demands on the basic circui ...

... nel the filter is symmetric with the inner pair of taps adapting (Fig. 1); in the 250mb/s channel the filter is asymmetric with 4 taps adapting. System considerations also constrain the latency through the filter preventing free pipelining. These requirements place great demands on the basic circui ...

QUESTIONS lesson 3 - JUANA

... What is an electric current? What are the names of the two types that exist, and how are they different? The electric current is the flow of electrons There are two types of currents: direct current (DC) and alternating current (AC). The direct current where the movement of the electrons is always i ...

... What is an electric current? What are the names of the two types that exist, and how are they different? The electric current is the flow of electrons There are two types of currents: direct current (DC) and alternating current (AC). The direct current where the movement of the electrons is always i ...

Class A Output Stage

... Class A output stage is a simple linear current amplifier. It is also very inefficient, typical maximum efficiency between 10 and 20 %. Only suitable for low power applications. High power requires much better efficiency. ...

... Class A output stage is a simple linear current amplifier. It is also very inefficient, typical maximum efficiency between 10 and 20 %. Only suitable for low power applications. High power requires much better efficiency. ...

GLOSSARY IT 327 PACKET An Excellence Project by Ed Packer

... Resonance: A particular frequency in a series LC circuit at which the current has its highest amplitude. It is characterized by the fact that XC=XL (so they cancel each other) and the total impedance (Z) = the resistance of the circuit, and the phase shift =0°. RMS Value: Root mean square of the pe ...

... Resonance: A particular frequency in a series LC circuit at which the current has its highest amplitude. It is characterized by the fact that XC=XL (so they cancel each other) and the total impedance (Z) = the resistance of the circuit, and the phase shift =0°. RMS Value: Root mean square of the pe ...

Lab #1: Ohm`s Law (and not Ohm`s Law)

... Lab #3 and Lab 4: RC and RL Circuits • Remember what capacitors and inductors are • Remember why circuits containing them can have currents that change with time ...

... Lab #3 and Lab 4: RC and RL Circuits • Remember what capacitors and inductors are • Remember why circuits containing them can have currents that change with time ...

as a PDF

... DyCML circuits combine the advantages of metal–oxide– semiconductor current-mode logic circuits with those of dynamic logic families to achieve high performance at a low voltage swing and low power dissipation [15]. Fig. 2 shows the general structure of the DyCML logic. A function F is implemented u ...

... DyCML circuits combine the advantages of metal–oxide– semiconductor current-mode logic circuits with those of dynamic logic families to achieve high performance at a low voltage swing and low power dissipation [15]. Fig. 2 shows the general structure of the DyCML logic. A function F is implemented u ...

EE414 Lecture Notes (electronic)

... - Initial turn-on of the IC causes a fast change in the voltage of the supply from 0-to-VDD - this causes enough charge displacement in the substrate to bias the SCR Signals Larger than VDD - if input signals have large amounts of overshoot resulting in voltages larger than VDD or less than VSS they ...

... - Initial turn-on of the IC causes a fast change in the voltage of the supply from 0-to-VDD - this causes enough charge displacement in the substrate to bias the SCR Signals Larger than VDD - if input signals have large amounts of overshoot resulting in voltages larger than VDD or less than VSS they ...

GSK-24 Logic Probe Kit The purpose of a logic probe is to examine

... over the full range of CMOS circuit voltages. In practice this is from 5V to 15V. If the probe takes its power supply from the circuit under test (as most do) then all components in the probe must operate over the 5 to 15 volt range. Some electronic equipment may have different voltage circuits with ...

... over the full range of CMOS circuit voltages. In practice this is from 5V to 15V. If the probe takes its power supply from the circuit under test (as most do) then all components in the probe must operate over the 5 to 15 volt range. Some electronic equipment may have different voltage circuits with ...

Computer Simulation Problems Section 8.1: The MOS Differential

... of the two circuits? 8.19 A differential amplifier is designed to have a differen tial voltage gain equal to the voltage gain of a common source amplifier. Both amplifiers use the same values of RD and supply voltages and are designed to dissipate equal amounts of power in their equilibrium or qui ...

... of the two circuits? 8.19 A differential amplifier is designed to have a differen tial voltage gain equal to the voltage gain of a common source amplifier. Both amplifiers use the same values of RD and supply voltages and are designed to dissipate equal amounts of power in their equilibrium or qui ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.