LOW NOISE, HIGH SLEW RATE, UNITY GAIN STABLE VOLTAGE FEEDBACK AMPLIFIER THS4271-EP FEATURES

... amplifiers. The devices are available in SOIC, MSOP with PowerPAD™, and leadless MSOP with PowerPAD™ packages. The THS4271 may have low-level oscillation when the die temperature (also known as the junction temperature) exceeds +60°C and is not recommended for new designs. For more information, see ...

... amplifiers. The devices are available in SOIC, MSOP with PowerPAD™, and leadless MSOP with PowerPAD™ packages. The THS4271 may have low-level oscillation when the die temperature (also known as the junction temperature) exceeds +60°C and is not recommended for new designs. For more information, see ...

LOC12a Resistors in Series and Parallel

... parallel across a power supply as shown in Figure 4, the potential difference across each resistor is equal to that supplied by the power supply. What about the current? A current I flows out of the power supply. Let I 1 be the current flowing through R1 and let I 2 be the current flowing through R2 ...

... parallel across a power supply as shown in Figure 4, the potential difference across each resistor is equal to that supplied by the power supply. What about the current? A current I flows out of the power supply. Let I 1 be the current flowing through R1 and let I 2 be the current flowing through R2 ...

General Description Features

... count, high-performance portable and cart-based ultrasound systems. The easy-to-use IC allows the user to achieve high-end 2D, PW, and CW Doppler (CWD) imaging capability using substantially less space and power. The highly compact imaging receiver lineup, including low-noise amplifier (LNA), variab ...

... count, high-performance portable and cart-based ultrasound systems. The easy-to-use IC allows the user to achieve high-end 2D, PW, and CW Doppler (CWD) imaging capability using substantially less space and power. The highly compact imaging receiver lineup, including low-noise amplifier (LNA), variab ...

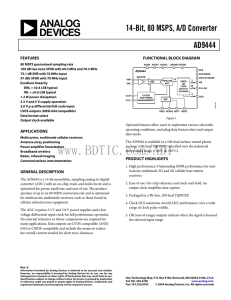

14-Bit, 80 MSPS, A/D Converter AD9444 FEATURES

... Out-of-Range Recovery Time The time it takes for the ADC to reacquire the analog input after a transition from 10% above positive full scale to 10% above negative full scale, or from 10% below negative full scale to 10% below positive full scale. ...

... Out-of-Range Recovery Time The time it takes for the ADC to reacquire the analog input after a transition from 10% above positive full scale to 10% above negative full scale, or from 10% below negative full scale to 10% below positive full scale. ...

Leakage Power and Circuit Aging Cooptimization by Gate Replacement Techniques

... either high or low, but with gate replacement method, only certain output value can be forced. However, gate replacement does not destroy gate structure, the standard cell library can be directly used; On the other hand, with “control point insertion”, it may introduce extra stacking effect [20], [3 ...

... either high or low, but with gate replacement method, only certain output value can be forced. However, gate replacement does not destroy gate structure, the standard cell library can be directly used; On the other hand, with “control point insertion”, it may introduce extra stacking effect [20], [3 ...

TPA6030A4 数据资料 dataSheet 下载

... VOLUME, SEDIFF, AND SEMAX OPERATION The three pins labeled VOLUME, SEDIFF, and SEMAX control the speaker (BTL) volume (VOLUME pin only) and the headphone (SE) volume. All three of these pins are controlled with a dc voltage. These voltages are a percentage of the voltage on the 5VREF pin. The 5VREF ...

... VOLUME, SEDIFF, AND SEMAX OPERATION The three pins labeled VOLUME, SEDIFF, and SEMAX control the speaker (BTL) volume (VOLUME pin only) and the headphone (SE) volume. All three of these pins are controlled with a dc voltage. These voltages are a percentage of the voltage on the 5VREF pin. The 5VREF ...

Variable Frequency Drive / Inverter

... Slip compensation, Reversing prevention, Auto restart, PID control ...

... Slip compensation, Reversing prevention, Auto restart, PID control ...

lecture1424265031

... successive layers of wires containing 6, 12, 18, 24 ...... wires. Thus, if there are n layers, the total number of individual wires is 3n(n + 1) + 1. In the manufacture of stranded conductors, the consecutive layers of wires are twisted or spiralled in opposite directions so that layers are bound to ...

... successive layers of wires containing 6, 12, 18, 24 ...... wires. Thus, if there are n layers, the total number of individual wires is 3n(n + 1) + 1. In the manufacture of stranded conductors, the consecutive layers of wires are twisted or spiralled in opposite directions so that layers are bound to ...

MP2681 - Monolithic Power System

... During pre-charge mode the charge timer is fixed with a set capacity based on the battery specifications. During CC and CV charge mode the timer duration is proportional to the charge rate. The timer will start counting after every time the charger process starts such as initial powerup or automatic ...

... During pre-charge mode the charge timer is fixed with a set capacity based on the battery specifications. During CC and CV charge mode the timer duration is proportional to the charge rate. The timer will start counting after every time the charger process starts such as initial powerup or automatic ...

Relay Contact Life

... The same situation exists in motor and transformer applications, and in applications where significant distributed line capacitance exists. During start-up, a motor can pull 600% or more of its running current. Thus, a 3 amp motor may actually pull 18 amps or more during start-up. A contact rated at ...

... The same situation exists in motor and transformer applications, and in applications where significant distributed line capacitance exists. During start-up, a motor can pull 600% or more of its running current. Thus, a 3 amp motor may actually pull 18 amps or more during start-up. A contact rated at ...

NTSX2102 1. General description Dual supply translating transceiver; open drain; auto

... The NTSX2102 can be used in point-to-point applications to interface between devices or systems operating at different supply voltages. The device is targeted at I2C or 1-wire buses which use open-drain drivers. ...

... The NTSX2102 can be used in point-to-point applications to interface between devices or systems operating at different supply voltages. The device is targeted at I2C or 1-wire buses which use open-drain drivers. ...

Assessment of Circuit Optimization Techniques Under NBTI Variability and Aging

... Different from the Vdd tuning methods belonging to NBTI compensation techniques, this method uses lower Vdd to decrease the NBTI degradation rate and therefore belongs to NBTI mitigation techniques. Tuning Vth . From Figure 2c and d, although higher Vth leads to larger intrinsic delay, NBTI degradat ...

... Different from the Vdd tuning methods belonging to NBTI compensation techniques, this method uses lower Vdd to decrease the NBTI degradation rate and therefore belongs to NBTI mitigation techniques. Tuning Vth . From Figure 2c and d, although higher Vth leads to larger intrinsic delay, NBTI degradat ...

ZXLD1374

... Pin driven either by open Drain or push-pull 3.3V or 5V logic levels. Drive with frequency higher than 100Hz to gate output ‘on’ and ‘off’ during dimming control. The device enters standby mode when PWM pin is driven with logic low level for more than 15ms nominal (Refer to application section for m ...

... Pin driven either by open Drain or push-pull 3.3V or 5V logic levels. Drive with frequency higher than 100Hz to gate output ‘on’ and ‘off’ during dimming control. The device enters standby mode when PWM pin is driven with logic low level for more than 15ms nominal (Refer to application section for m ...

EOS (Electrostatic Overstress)

... EOS often results in large scorch marks, discoloration of metal, melted metallization and/or bond wires, and massive destruction of the semiconductor component ...

... EOS often results in large scorch marks, discoloration of metal, melted metallization and/or bond wires, and massive destruction of the semiconductor component ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.