REVIEW ARTICLE Josephson voltage standards

... than physical artifacts are known as intrinsic standards. Although the Josephson voltage standard 共JVS兲 does not realize the SI definition of the volt, it provides a very stable reference voltage that can be reproduced anywhere without the need to transfer artifacts such as Weston cells. The accurac ...

... than physical artifacts are known as intrinsic standards. Although the Josephson voltage standard 共JVS兲 does not realize the SI definition of the volt, it provides a very stable reference voltage that can be reproduced anywhere without the need to transfer artifacts such as Weston cells. The accurac ...

AN1978

... obtain a higher current from the charge pump when pulsed load is applied on Vcc. In the typical applications a 100nF filter capacitor is connected to the Vcc output, near the ST8004 pins and another 100nF is connected, between C1 and C5, near the card slot as shown in Figure 7 and Figure 9. In order ...

... obtain a higher current from the charge pump when pulsed load is applied on Vcc. In the typical applications a 100nF filter capacitor is connected to the Vcc output, near the ST8004 pins and another 100nF is connected, between C1 and C5, near the card slot as shown in Figure 7 and Figure 9. In order ...

single-phase bridge rectifiers with current filters

... output of a rectifier with diodes (or with thyristors controlled α = 0o) and the effective value of the input AC voltage Vs. It is noted that, the maximum value of the DC voltage provided by a single-phase rectifier cannot reach the effective voltage of the input AC voltage (Vd(max) = Vd0 ≈ 0,9⋅Vs). ...

... output of a rectifier with diodes (or with thyristors controlled α = 0o) and the effective value of the input AC voltage Vs. It is noted that, the maximum value of the DC voltage provided by a single-phase rectifier cannot reach the effective voltage of the input AC voltage (Vd(max) = Vd0 ≈ 0,9⋅Vs). ...

AP7365 600mA, LOW QUIESCENT CURRENT, FAST TRANSIENT LOW DROPOUT LINEAR REGULATOR

... transient response of the LDO. The AP7365 is stable with very small ceramic output capacitors. Using a ceramic capacitor value that is at least 1μF with ESR > 15mΩ on the output ensures stability. Higher capacitance values help to improve line and load transient response. The output capacitance may ...

... transient response of the LDO. The AP7365 is stable with very small ceramic output capacitors. Using a ceramic capacitor value that is at least 1μF with ESR > 15mΩ on the output ensures stability. Higher capacitance values help to improve line and load transient response. The output capacitance may ...

MAX44244/MAX44245/MAX44248 36V, Precision, Low-Power, 90µA, Single/Quad/Dual Op Amps General Description

... provide ultra-precision, low-noise, zero-drift single/quad/ dual operational amplifiers featuring very low-power operation with a wide supply range. The devices incorporate a patented auto-zero circuit that constantly measures and compensates the input offset to eliminate drift over time and tempera ...

... provide ultra-precision, low-noise, zero-drift single/quad/ dual operational amplifiers featuring very low-power operation with a wide supply range. The devices incorporate a patented auto-zero circuit that constantly measures and compensates the input offset to eliminate drift over time and tempera ...

TPS76901 数据资料 dataSheet 下载

... ‡ The JEDEC Low K (1s) board design used to derive this data was a 3 inch x 3 inch, two layer board with 2 ounce copper traces on top of the board. § The JEDEC High K (2s2p) board design used to derive this data was a 3 inch x 3 inch, multilayer board with 1 ounce internal power and ground planes an ...

... ‡ The JEDEC Low K (1s) board design used to derive this data was a 3 inch x 3 inch, two layer board with 2 ounce copper traces on top of the board. § The JEDEC High K (2s2p) board design used to derive this data was a 3 inch x 3 inch, multilayer board with 1 ounce internal power and ground planes an ...

HV2213591366

... added to the dc component of id and iq. The error between the reference dc capacitor voltage and the sensed dc bus voltage of DSTATCOM is given to a proportional-integral (PI) controller whose output is considered the loss component of the current and is added to the dc component of id . Similarly, ...

... added to the dc component of id and iq. The error between the reference dc capacitor voltage and the sensed dc bus voltage of DSTATCOM is given to a proportional-integral (PI) controller whose output is considered the loss component of the current and is added to the dc component of id . Similarly, ...

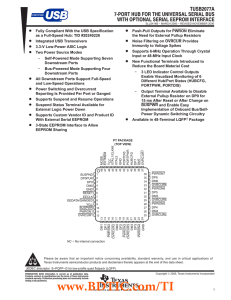

TUSB2077A 数据资料 dataSheet 下载

... The EXTMEM (terminal 47) enables or disables the optional EEPROM interface. When EXTMEM is high, the vendor and product IDs (VID and PID) use defaults, such that the message displayed during enumeration is General Purpose USB Hub. For this configuration, terminal 8 functions as the GANGED input term ...

... The EXTMEM (terminal 47) enables or disables the optional EEPROM interface. When EXTMEM is high, the vendor and product IDs (VID and PID) use defaults, such that the message displayed during enumeration is General Purpose USB Hub. For this configuration, terminal 8 functions as the GANGED input term ...

bq2407x Single-Chip Li-Ion Charge and System

... To disable the fast-charge safety timer and charge termination, tie TMR to the VREF pin. Tying the TMR pin high changes the timing resistor from the external value to an internal 50 kΩ ±25%, which can add an additional tolerance to any timed specification. The TMR pin normally regulates to 2.5 V whe ...

... To disable the fast-charge safety timer and charge termination, tie TMR to the VREF pin. Tying the TMR pin high changes the timing resistor from the external value to an internal 50 kΩ ±25%, which can add an additional tolerance to any timed specification. The TMR pin normally regulates to 2.5 V whe ...

Dual-Output, Low Dropout Volt Regs w/ Integrated SVS for Split

... a high signal to EN (enable) shuts down both regulators, reducing the input current to 1 mA at TJ = +25°C. The device is enabled when the EN pin is connected to a low-level input voltage. The output voltages of the two regulators are sensed at the VSENSE1 and VSENSE2 pins respectively. The input sig ...

... a high signal to EN (enable) shuts down both regulators, reducing the input current to 1 mA at TJ = +25°C. The device is enabled when the EN pin is connected to a low-level input voltage. The output voltages of the two regulators are sensed at the VSENSE1 and VSENSE2 pins respectively. The input sig ...

MAX3355E ±15kV ESD-Protected USB On-the-Go Charge Pump and Comparators in UCSP General Description

... SHDN to GND. Shutdown mode disables the charge pump and comparators (Table 4). While in shutdown mode, the STATUS1 output defaults to logic 0 and STATUS2 indicates VBUS. During shutdown, if VBUS is externally driven above VTH,SHDN (defined in the Comparators section), the MAX3355E sinks current from ...

... SHDN to GND. Shutdown mode disables the charge pump and comparators (Table 4). While in shutdown mode, the STATUS1 output defaults to logic 0 and STATUS2 indicates VBUS. During shutdown, if VBUS is externally driven above VTH,SHDN (defined in the Comparators section), the MAX3355E sinks current from ...

LT1739 - Dual 500mA, 200MHz xDSL Line Driver Amplifier

... Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Note 2: Applies to short circuits to ground only. A short circuit between the output and either supply may permanently damage the part when operated on supplies greater than ±10V. Note 3: The LT1739C ...

... Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Note 2: Applies to short circuits to ground only. A short circuit between the output and either supply may permanently damage the part when operated on supplies greater than ±10V. Note 3: The LT1739C ...

FTL7522 Low I Reset Timer with Fixed Delay and Reset Pulse

... Device default operation time N is 7.5s. If the DSR pin is pulled HIGH prior to VCC ramp, the FTL7522 enters Test Mode and the reset output, /RST1, is immediately pulled LOW for factory testing. The DSR pin MUST be forced to GND during normal operation. The DSR pin should never be driven HIGH or lef ...

... Device default operation time N is 7.5s. If the DSR pin is pulled HIGH prior to VCC ramp, the FTL7522 enters Test Mode and the reset output, /RST1, is immediately pulled LOW for factory testing. The DSR pin MUST be forced to GND during normal operation. The DSR pin should never be driven HIGH or lef ...

Low noise cryogenic electronics : preamplifier - CEA-Irfu

... Assuming the circuit is to be build around an ideal operational amplifier and neglecting stray and parasitic capacitors, the condition for the output not to be saturated is that the non-inverting input of the amplifier be kept to ground. Then Vout Vout ...

... Assuming the circuit is to be build around an ideal operational amplifier and neglecting stray and parasitic capacitors, the condition for the output not to be saturated is that the non-inverting input of the amplifier be kept to ground. Then Vout Vout ...

Simultaneous Communication and Processor Voltage Scaling for Dynamic and

... [10, 11, 19] and fat wires reduce the wire resistance [18, 19]. Techniques for the determination of the optimal quantity of repeaters are introduced in [10, 11]. An approach to calculate the optimal voltage swing on fat wires has been proposed in [18]. Similar to processors with supply voltage scali ...

... [10, 11, 19] and fat wires reduce the wire resistance [18, 19]. Techniques for the determination of the optimal quantity of repeaters are introduced in [10, 11]. An approach to calculate the optimal voltage swing on fat wires has been proposed in [18]. Similar to processors with supply voltage scali ...

For Full Text Click Here

... domain can be easily converted into time domain signal. The reflected voltage which is shown in Figure 3.a is actually the multiple reflections of the incident voltage time waveform from multiple discontinuity points in a circuit (which means different time delays) with different coefficients. These ...

... domain can be easily converted into time domain signal. The reflected voltage which is shown in Figure 3.a is actually the multiple reflections of the incident voltage time waveform from multiple discontinuity points in a circuit (which means different time delays) with different coefficients. These ...

Power MOSFET

A power MOSFET is a specific type of metal oxide semiconductor field-effect transistor (MOSFET) designed to handle significant power levels.Compared to the other power semiconductor devices, for example an insulated-gate bipolar transistor (IGBT) or a thyristor, its main advantages are high commutation speed and good efficiency at low voltages. It shares with the IGBT an isolated gate that makes it easy to drive. They can be subject to low gain, sometimes to degree that the gate voltage needs to be higher than the voltage under control.The design of power MOSFETs was made possible by the evolution of CMOS technology, developed for manufacturing integrated circuits in the late 1970s. The power MOSFET shares its operating principle with its low-power counterpart, the lateral MOSFET.The power MOSFET is the most widely used low-voltage (that is, less than 200 V) switch. It can be found in most power supplies, DC to DC converters, and low voltage motor controllers.