Bds96 - Instituto de Ingeniería Eléctrica

... current. Moreover, due to the flat characteristic of the gm/ID vs. ID/(W/L) curve near the weak inversion region, in this region a small increment of gm/ID requires a big increment of (W/L). By exploring the design space through the gm/ID method we can choose the best compromise between performance ...

... current. Moreover, due to the flat characteristic of the gm/ID vs. ID/(W/L) curve near the weak inversion region, in this region a small increment of gm/ID requires a big increment of (W/L). By exploring the design space through the gm/ID method we can choose the best compromise between performance ...

gain and output impedance of JFET stages

... When considering input signals of small amplitudes, the JFET device can be modelled as a linear voltage-controlled source. Both voltage-controlled voltage source (VCVS) and voltage-controlled current source (VCCS) are suitable models for the JFET device, because the controlled source can be transfor ...

... When considering input signals of small amplitudes, the JFET device can be modelled as a linear voltage-controlled source. Both voltage-controlled voltage source (VCVS) and voltage-controlled current source (VCCS) are suitable models for the JFET device, because the controlled source can be transfor ...

Appendix C Ohm`s Law, Kirchhoff`s Laws and AC Circuits

... Figure C.2 shows a phasor diagram representing the input voltage and the circuit current. Both phasors rotate counterclockwise as ωt increases. Notice that the voltage leads the current, as expected for an inductive circuit, and that the angle between the voltage and current phasors is the phase ang ...

... Figure C.2 shows a phasor diagram representing the input voltage and the circuit current. Both phasors rotate counterclockwise as ωt increases. Notice that the voltage leads the current, as expected for an inductive circuit, and that the angle between the voltage and current phasors is the phase ang ...

SUPERPOSITION

... voltage or current has been computed due to each and every source acting alone Add all the computed values obtained from analysing the circuit with each source acting alone. The sum is the actual voltage or current when all sources are acting simultaneously (i.e. when all the sources are present) Im ...

... voltage or current has been computed due to each and every source acting alone Add all the computed values obtained from analysing the circuit with each source acting alone. The sum is the actual voltage or current when all sources are acting simultaneously (i.e. when all the sources are present) Im ...

Name Symbol Units

... proportional to the current that flows through it The constant of proportionality is called resistance, R, and has units of Ohms (Ω) This is known as Ohm’s law and is usually written as ...

... proportional to the current that flows through it The constant of proportionality is called resistance, R, and has units of Ohms (Ω) This is known as Ohm’s law and is usually written as ...

Lab 4: Bipolar transistors and transistor circuits Lab 4: Bipolar

... series with the load. The blocking capacitor keeps the load from changing the DC biasing scheme while still having a very low impedance at frequencies in the kHz range—for example, a 4.7 μF capacitor has XC=34 Ω at 1 kHz.) 4-5 Transistor switch The following circuit illustrates the use of a transist ...

... series with the load. The blocking capacitor keeps the load from changing the DC biasing scheme while still having a very low impedance at frequencies in the kHz range—for example, a 4.7 μF capacitor has XC=34 Ω at 1 kHz.) 4-5 Transistor switch The following circuit illustrates the use of a transist ...

FINAL09fa

... if you only added capacitance to C2? What if you only added capacitance to Cc, with a series resistor RZ? What value should you use for RZ? ...

... if you only added capacitance to C2? What if you only added capacitance to Cc, with a series resistor RZ? What value should you use for RZ? ...

DM74S51 Dual 2-Wide 2-Input AND-OR

... 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N14A ...

... 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N14A ...

(Solution)Assignment ent 162 ch456

... To start, assume that both QI and Q2 are off, and therefore that the SCS is not conducting. A positive pulse on the cathode gate drives Q2 into conduction and thus provides a path for Q. base CUITent. When Ql turns on, its collector CUITent provides base current for Qb thus sustaining the Oil state ...

... To start, assume that both QI and Q2 are off, and therefore that the SCS is not conducting. A positive pulse on the cathode gate drives Q2 into conduction and thus provides a path for Q. base CUITent. When Ql turns on, its collector CUITent provides base current for Qb thus sustaining the Oil state ...

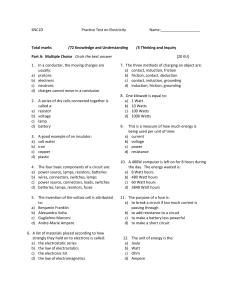

Practice Unit Test - hhs-snc1d

... a) What would happen to the lamps if points A and B were connected with a wire? ...

... a) What would happen to the lamps if points A and B were connected with a wire? ...

The transistor

... You would make sure that the amplitude of the signal was less than 0.50 V. Thus the input signal would always lie between 1 and 2 volts centred on 1.5 V. The output voltage would be centred on 5 V and varying between 0 and 10 V. Any input voltage below 1 volt would always yield a 0 V output and any ...

... You would make sure that the amplitude of the signal was less than 0.50 V. Thus the input signal would always lie between 1 and 2 volts centred on 1.5 V. The output voltage would be centred on 5 V and varying between 0 and 10 V. Any input voltage below 1 volt would always yield a 0 V output and any ...

Load-commutated Current Source Inverter (CSI)

... load is capacitive, it was shown that forced commutation may not be needed. The operation of a single-phase CSI with capacitive load (Fig. 40.1) is discussed here. It may be noted that the capacitor, C is assumed to be in parallel with resistive load (R). The capacitor, C is used for storing the cha ...

... load is capacitive, it was shown that forced commutation may not be needed. The operation of a single-phase CSI with capacitive load (Fig. 40.1) is discussed here. It may be noted that the capacitor, C is assumed to be in parallel with resistive load (R). The capacitor, C is used for storing the cha ...

Homework 5 - University of Southern California

... The biasing circuit in Fig. (P18) is typically designed to ensure that transistor Q1 is biased within in its linear active domain. If the circuit is to provide a static collector biasing current, ICQ, that is nominally independent of temperature over reasonable base-emitter junction temperature excu ...

... The biasing circuit in Fig. (P18) is typically designed to ensure that transistor Q1 is biased within in its linear active domain. If the circuit is to provide a static collector biasing current, ICQ, that is nominally independent of temperature over reasonable base-emitter junction temperature excu ...

LOYOLA COLLEGE (AUTONOMOUS), CHENNAI – 600 034

... 15. With a neat circuit explain the working of a decade counter. How does the counter returns to normal state when preset to one of the illegal states? ...

... 15. With a neat circuit explain the working of a decade counter. How does the counter returns to normal state when preset to one of the illegal states? ...

MCL2 UK - Fil Control

... The MCL2 is a yarn break capacitive sensor useful for assembling, and winding applications. MAIN FUNCTION: To control the linear motion of two textile yarns when assembling. When a yarn breaks or stops, the MCL2 will inform the user (flashing LED) that a position is defective. It can also activate a ...

... The MCL2 is a yarn break capacitive sensor useful for assembling, and winding applications. MAIN FUNCTION: To control the linear motion of two textile yarns when assembling. When a yarn breaks or stops, the MCL2 will inform the user (flashing LED) that a position is defective. It can also activate a ...

1304 A Current Copier Latch Circuit as Current

... Latching is an important and fundamental operation in varying applications such as filtering, analogue-to-digital conversion. Iterative weight-update with each sample input in training neural networks, [1]-[3], and system modeling in control, [4]-[5], are some of the examples of latching and can be ...

... Latching is an important and fundamental operation in varying applications such as filtering, analogue-to-digital conversion. Iterative weight-update with each sample input in training neural networks, [1]-[3], and system modeling in control, [4]-[5], are some of the examples of latching and can be ...

Wilson current mirror

A Wilson current mirror is a three-terminal circuit (Fig. 1) that accepts an input current at the input terminal and provides a ""mirrored"" current source or sink output at the output terminal. The mirrored current is a precise copy of the input current. It may be used as a Wilson current source by applying a constant bias current to the input branch as in Fig. 2. The circuit is named after George R. Wilson, an integrated circuit design engineer who worked for Tektronix. Wilson devised this configuration in 1967 when he and Barrie Gilbert challenged each other to find an improved current mirror overnight that would use only three transistors. Wilson won the challenge.