* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Homework 5 - University of Southern California

Index of electronics articles wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Power electronics wikipedia , lookup

Invention of the integrated circuit wikipedia , lookup

Schmitt trigger wikipedia , lookup

Molecular scale electronics wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Regenerative circuit wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Integrated circuit wikipedia , lookup

Opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Thermal runaway wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Current source wikipedia , lookup

Operational amplifier wikipedia , lookup

Two-port network wikipedia , lookup

Wilson current mirror wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

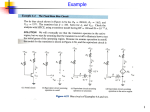

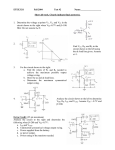

U niversity of S outhern C alifornia School Of Engineering Department Of Electrical Engineering EE 348: Homework Assignment #05 (Due 03/05/2002) Spring, 2002 Choma Problem #18: The biasing circuit in Fig. (P18) is typically designed to ensure that transistor Q1 is biased within in its linear active domain. If the circuit is to provide a static collector biasing current, ICQ, that is nominally independent of temperature over reasonable base-emitter junction temperature excursions, the circuit must be designed so that the two transistors, Q1 and Q2, are electrically identical and conduct equal collector current densities. In turn, this design constraint guarantees that the two transistor base-emitter voltages, VBE1 and VBE2, match one another over a wide range of operating temperatures. Consider the case in which the base-emitter junction area of transistor Q1 matches that of transistor Q2. (a). Assuming that the circuit is designed correctly to ensure acceptable temperature desensitization, derive an expression for the static collector current, ICQ, in terms of circuit parameters, applied static voltages, and transistor hFE and VBE. (b). What design criterion must be satisfied to render ICQ almost independent of hFE? (c). Why is the biasing current, ICQ, nominally independent of the voltage, VP? (d). For a fixed collector load resistance, RL, what smallest value of applied static voltage, VP, ensures transistor Q1 operation in its linear regime? +VCC +VP R1 RL ICQ Q1 Q2 R2 Ree Fig. (P18) Problem #19: A modified version of the biasing configuration in Fig. (P18) appears in Fig. P19). All transistors are identical with the possible exception that the area ratios of the two devices can be adjusted to ensure that each transistor conducts nominally identical current densities, thereby preserving nominally identical base-emitter (VBE) voltages across the two transis- EE 348 University of Southern California J. Choma, Jr. tors. For analytical simplicity and tractability, assume that each transistor has sufficiently large hFE to warrant tacit neglect of all quiescent base currents. +VCC +VP R1 RL ICQ Q1 Ry Q2 Rx R2 Ree Fig. (P19) (a). Derive an expression for the static collector current, ICQ, in terms of circuit parameters, applied static voltages, and transistor VBE. (b). Can a design criterion be invoked to render ICQ theoretically independent of VBE? If so, what is this design criterion? What circuit situation renders impossible the total desensitization of ICQ with respect to VBE? Problem #20: The three transistors in the base current–compensated bias current mirror of Fig. (P20) are electrically identical and conduct identical collector current densities. As usual, the circuit is designed to ensure that all transistors operate in their respective linear regimes. +VCC +VP R Rl Q3 ICQ Q2 Q1 Rx Fig. (P20) (a). Derive an expression for the bias current, ICQ, in terms of circuit parameters, transistor hFE, and transistor VBE. Homework #05 31 Spring Semester, 2002 EE 348 University of Southern California J. Choma, Jr. (b). What design requirements must be satisfied to render ICQ almost independent of hFE? (c). What purpose is served by resistor RX? Would the circuit operate acceptably over wide temperature ranges if RX were supplanted by an open circuit? Problem #21: The TN2219AM NPN transistor has the following abridged set of SPICE parameters. Use SPICE to generate, and submit plots of, the following static characteristic curves. Save copies of these plots; you will need them in subsequent homework assignments! (a). Base current (IB) -versus- base-emitter voltage (VBE) for collector-emitter voltages (VCE) of 1.5, 2.5, and 3.5 volts. Vary VBE from zero -to- 800 mV. (b). Collector current (IC) -versus- VBE for VCE =1.5, 2.5, and 3.5 volts. Vary VBE from zero to- 800 mV. (c). Static current gain (hFE = IC/IB) -versus- IC for VCE =1.5, 2.5, and 3.5 volts. Vary IC from 100 nA -to- 10 mA, and plot IC on a logarithmic scale. PARAMETER Homework #05 DESCRIPTION VALUE UNITS IS F NF VAF IKF Transport Saturation Current Forward Current Gain B-E Junction Emission Coefficient Forward Early Voltage Forward Knee Current 1.80 140 1.0 54 22 fA –– –– volts mA ISE NE R NR RB B-E Leakage Saturation Current B-E Leakage Emission Coefficient Reverse Current Gain B-C Junction Emission Coefficient Average Base Resistance 800 2.05 0.2 1.0 150 fA –– –– –– ohms RE RC CJE VJE MJE Average Emitter Resistance Average Collector Resistance Zero Bias B-E Junction Capacitance B-E Built-In Potential B-E Junction Grading Coefficient 2 120 5 950 0.5 ohms ohms fF mV –– CJC VJC MJC CJS VJS Zero Bias B-C Junction Capacitance B-C Built-In Potential B-C Junction Grading Coefficient Zero Bias Substrate Capacitance Substrate-Collector Built-In Potential 10 790 0.34 50 700 fF mV –– fF mV MJS TF TR Subs.-Collector Junction Grading Coeff. Forward Minority Carrier Transit Time Reverse Minority Carrier Transit Time 0.5 9 46.9 –– pSEC nSEC 32 Spring Semester, 2002 EE 348 University of Southern California J. Choma, Jr. Problem #22: Use the TN2219AM NPN transistor to design the circuit of Fig. (P18) to meet the following requirements and specifications (presumed quoted at 27 ºC). VCC = VP = 3.3 volts Both transistors biased for linear operation Both transistors identical, inclusive of junction areas ICQ = 1.2 mA @ VCE1 = 1.8 volts RL 5Ree ICQ changes by no more than 10% for temperatures ranging from 27 ºC - to- 75 ºC. Simulate the circuit, making sure to check the following performance indices. When the simulations do not track with either specifications or calculations, find out why and execute the required corrective actions. (a). (b). (c). (d). Collector current (ICQ) at temperature (T) = 27 ºC, 50 ºC, 75 ºC. Voltage at base of transistor Q1, with respect to ground, at T = 27 ºC, 50 ºC, 75 ºC. Voltage at collector of transistor Q1, with respect to ground, at T = 27 ºC, 50 ºC, 75 ºC. Voltage at emitter of transistor Q1, with respect to ground, at T = 27 ºC, 50 ºC, 75 ºC. Homework #05 33 Spring Semester, 2002 EE 348 University of Southern California J. Choma, Jr. U niversity of S outhern C alifornia School Of Engineering Department Of Electrical Engineering EE 348: Homework Assignment #05 (SOLUTIONS: Due 03/05/2002) Spring, 2002 Choma Problem #18: Homework #05 34 Spring Semester, 2002