ADS850 数据资料 dataSheet 下载

... to be 2Vp-p. This signal is ac-coupled in single-ended form to the ADS850 using the low distortion voltage-feedback amplifier OPA642. As is generally necessary for singlesupply components, operating the ADS850 with a full-scale input signal swing requires a level-shift of the amplifier’s zero-center ...

... to be 2Vp-p. This signal is ac-coupled in single-ended form to the ADS850 using the low distortion voltage-feedback amplifier OPA642. As is generally necessary for singlesupply components, operating the ADS850 with a full-scale input signal swing requires a level-shift of the amplifier’s zero-center ...

Task C - Electronic fundamenals regional heat 2011

... Predict how the operation of this active filter circuit shown on figure 3 will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults): ...

... Predict how the operation of this active filter circuit shown on figure 3 will be affected as a result of the following faults. Consider each fault independently (i.e. one at a time, no multiple faults): ...

Standard single purpose processors

... The crystal-controlled oscillator generates a very consistent highfrequency digital pulses that feed the cascaded counters. - the first counter counts these pulses up to the oscillator freq., which corresponds to exactly one second. - at this point, it generate a pulse that feeds the next counter. ...

... The crystal-controlled oscillator generates a very consistent highfrequency digital pulses that feed the cascaded counters. - the first counter counts these pulses up to the oscillator freq., which corresponds to exactly one second. - at this point, it generate a pulse that feeds the next counter. ...

Timers and Oscillators - Microwave Electronics Laboratory at UCSB

... important as the fundamental building block of a register or memory device. This circuit is also known as a flip-flop. A similar circuit is a Schmitt trigger. In this section we will build a simple version of each type using discrete transistors. In practice, it is more common to use dedicated ICs s ...

... important as the fundamental building block of a register or memory device. This circuit is also known as a flip-flop. A similar circuit is a Schmitt trigger. In this section we will build a simple version of each type using discrete transistors. In practice, it is more common to use dedicated ICs s ...

AD9742 数据手册DataSheet 下载

... resolution, and cost. The AD9742 offers exceptional ac and dc performance while supporting update rates up to 210 MSPS. The AD9742’s low power dissipation makes it well suited for portable and low power applications. Its power dissipation can be further reduced to a mere 60 mW with a slight degradat ...

... resolution, and cost. The AD9742 offers exceptional ac and dc performance while supporting update rates up to 210 MSPS. The AD9742’s low power dissipation makes it well suited for portable and low power applications. Its power dissipation can be further reduced to a mere 60 mW with a slight degradat ...

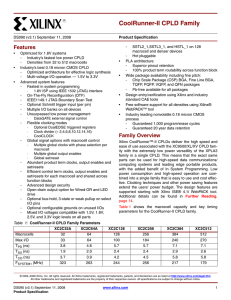

CoolRunner-II CPLD Family Data Sheet

... CPLD architecture combining macrocells into Function Blocks (FBs) interconnected with a global routing matrix, the Xilinx Advanced Interconnect Matrix (AIM). The FBs use a Programmable Logic Array (PLA) configuration which allows all product terms to be routed and shared among any of the macrocells ...

... CPLD architecture combining macrocells into Function Blocks (FBs) interconnected with a global routing matrix, the Xilinx Advanced Interconnect Matrix (AIM). The FBs use a Programmable Logic Array (PLA) configuration which allows all product terms to be routed and shared among any of the macrocells ...

document

... Servo motors and are constructed out of basic DC motors, by adding: • some gear reduction • a position sensor for the motor shaft • an electronic circuit that controls the motor's operation The basic hobby servo has a 180:1 gear ratio. The motor is typically small. Typically, a potentiometer (va ...

... Servo motors and are constructed out of basic DC motors, by adding: • some gear reduction • a position sensor for the motor shaft • an electronic circuit that controls the motor's operation The basic hobby servo has a 180:1 gear ratio. The motor is typically small. Typically, a potentiometer (va ...

Measuring Output VSWR For An Active Levelled Source

... output and reflected signals adding; and show a minima when they are in anti-phase, the reflected signal subtracting from the original output signal. The maximum to minimum level of the combined output signal gives the peak to peak value of the reflected signal. Therefore by changing the phase relat ...

... output and reflected signals adding; and show a minima when they are in anti-phase, the reflected signal subtracting from the original output signal. The maximum to minimum level of the combined output signal gives the peak to peak value of the reflected signal. Therefore by changing the phase relat ...

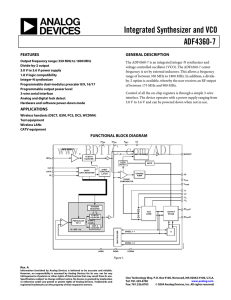

Integrated Synthesizer and VCO ADF4360-7 FEATURES

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

measurements on libera electron and libera brilliance bpm electronics

... latency on the FOFB. Global acquisitions of position reading around the ring Interlock output of the Libera was used to measure the are synchronized over the revolution clock (1.1153MHz latency. Figure 5 illustrates the test setup. for ALBA storage ring). Each Libera accomplishes the synchronization ...

... latency on the FOFB. Global acquisitions of position reading around the ring Interlock output of the Libera was used to measure the are synchronized over the revolution clock (1.1153MHz latency. Figure 5 illustrates the test setup. for ALBA storage ring). Each Libera accomplishes the synchronization ...

AT91SAM9G20 Summary - Technologic Systems

... – 0.9V to 1.1V for VDDBU, VDDCORE, VDDPLL – 1.65 to 3.6V for VDDOSC – 1.65V to 3.6V for VDDIOP (Peripheral I/Os) – 3.0V to 3.6V for VDDUSB – 3.0V to 3.6V VDDANA (Analog-to-digital Converter) – Programmable 1.65V to 1.95V or 3.0V to 3.6V for VDDIOM (Memory I/Os) Available in a 217-ball LFBGA and 247- ...

... – 0.9V to 1.1V for VDDBU, VDDCORE, VDDPLL – 1.65 to 3.6V for VDDOSC – 1.65V to 3.6V for VDDIOP (Peripheral I/Os) – 3.0V to 3.6V for VDDUSB – 3.0V to 3.6V VDDANA (Analog-to-digital Converter) – Programmable 1.65V to 1.95V or 3.0V to 3.6V for VDDIOM (Memory I/Os) Available in a 217-ball LFBGA and 247- ...

Accessories Other Specifications Specifications

... 5 mV to 5 V/div: DC to 30 MHz (-3dB) X5: DC to 10 MHz (-3dB) 12ns (Overshoot <5%) CH 1: CH 1, single trace CH 2, single trace dual trace, alternating dual trace, chopped agebraic sum of CH 1 + CH 2 CH 2 only 400 V (DC to AC peak) ...

... 5 mV to 5 V/div: DC to 30 MHz (-3dB) X5: DC to 10 MHz (-3dB) 12ns (Overshoot <5%) CH 1: CH 1, single trace CH 2, single trace dual trace, alternating dual trace, chopped agebraic sum of CH 1 + CH 2 CH 2 only 400 V (DC to AC peak) ...

PowerPoint Sunusu

... test head. Such an observation point represents an intermediate point along the cascaded transmission line. As a result, a rising edge will appear as a pair of transitions rather than a single transition. The novice test engineer often thinks the tester driver is defective, when in fact it is workin ...

... test head. Such an observation point represents an intermediate point along the cascaded transmission line. As a result, a rising edge will appear as a pair of transitions rather than a single transition. The novice test engineer often thinks the tester driver is defective, when in fact it is workin ...

AD1974 数据手册DataSheet下载

... The internal MCLK can be disabled in the PLL and Clock Control 0 register to reduce power dissipation when the AD1974 is idle. The clock should be stable before it is enabled. Unless a standalone mode is selected (see the Serial Control Port section), the clock is disabled by reset and must be enabl ...

... The internal MCLK can be disabled in the PLL and Clock Control 0 register to reduce power dissipation when the AD1974 is idle. The clock should be stable before it is enabled. Unless a standalone mode is selected (see the Serial Control Port section), the clock is disabled by reset and must be enabl ...

Methods of measuring low, medium and high resistances

... have the advantage that chance level is defined to be 0, and they have the form of a probability. Informedness has the stronger property that it is the probability that an informed decision is made (rather than a guess), when positive. When negative this is still true for the absolutely value of Inf ...

... have the advantage that chance level is defined to be 0, and they have the form of a probability. Informedness has the stronger property that it is the probability that an informed decision is made (rather than a guess), when positive. When negative this is still true for the absolutely value of Inf ...

- Krest Technology

... The small-signal behavior of both buffers is shown in Fig. 3(b). Apart from the attenuation, they create a peaking of 1.1 dB in the frequency domain and change the 3-dB corner frequency of the T/H output signal by 1.8%, from 68.3 to 69.5 GHz. In addition to the frequency compensation, one key challe ...

... The small-signal behavior of both buffers is shown in Fig. 3(b). Apart from the attenuation, they create a peaking of 1.1 dB in the frequency domain and change the 3-dB corner frequency of the T/H output signal by 1.8%, from 68.3 to 69.5 GHz. In addition to the frequency compensation, one key challe ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.