TJA1027 1. General description LIN 2.2A/SAE J2602 transceiver

... A loss of power (pins VBAT and GND) has no impact on the bus line or on the microcontroller. No reverse currents flow from the bus into pin LIN. The current path from VBAT to LIN via the integrated LIN slave termination resistor remains. The LIN transceiver can be disconnected from the power supply ...

... A loss of power (pins VBAT and GND) has no impact on the bus line or on the microcontroller. No reverse currents flow from the bus into pin LIN. The current path from VBAT to LIN via the integrated LIN slave termination resistor remains. The LIN transceiver can be disconnected from the power supply ...

PC8349/E [Preliminary]

... – Complies with USB Specification Rev. 2.0 – High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations – Direct connection to a high-speed device without an external hub – External PHY with serial and low-pin count (ULPI) interfaces • Local bus controller (LBC) – Multiplexed 3 ...

... – Complies with USB Specification Rev. 2.0 – High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations – Direct connection to a high-speed device without an external hub – External PHY with serial and low-pin count (ULPI) interfaces • Local bus controller (LBC) – Multiplexed 3 ...

ltc1694.pdf

... must be fulfilled if a high value of RS is used. An acknowledge is accomplished by the SMBus host releasing the SDA line (pulling high) at the end of the last bit sent and the SMBus slave device pulling the SDA line low before the rising edge of the ACK clock pulse. The LTC1694 2.2mA boosted pull-up ...

... must be fulfilled if a high value of RS is used. An acknowledge is accomplished by the SMBus host releasing the SDA line (pulling high) at the end of the last bit sent and the SMBus slave device pulling the SDA line low before the rising edge of the ACK clock pulse. The LTC1694 2.2mA boosted pull-up ...

5 Requirements - ISO/IEC JTC 1/SC 25/WG 1 Home Page

... ISO/IEC 15045-1 (part 1) specifies the functional requirements and basic architecture for the residential gateway. This part, ISO/IEC 15045-2 (part 2), specifies a residential gateway modular structure and an internal protocol and language that may be used to implement a conforming gateway system fo ...

... ISO/IEC 15045-1 (part 1) specifies the functional requirements and basic architecture for the residential gateway. This part, ISO/IEC 15045-2 (part 2), specifies a residential gateway modular structure and an internal protocol and language that may be used to implement a conforming gateway system fo ...

TJA1029 1. General description LIN 2.2A/SAE J2602 transceiver with TXD dominant timeout

... The TJA1029 is the interface between the Local Interconnect Network (LIN) master/slave protocol controller and the physical bus in a LIN network. It is primarily intended for in-vehicle subnetworks using baud rates up to 20 kBd and is compliant with LIN 2.0, LIN 2.1, LIN 2.2, LIN 2.2A and SAE J2602. ...

... The TJA1029 is the interface between the Local Interconnect Network (LIN) master/slave protocol controller and the physical bus in a LIN network. It is primarily intended for in-vehicle subnetworks using baud rates up to 20 kBd and is compliant with LIN 2.0, LIN 2.1, LIN 2.2, LIN 2.2A and SAE J2602. ...

MC68HC705 microcontroller

... Appendix A. MC68HRC705J1A . . . . . . . . . . . . . . . . . . . 137 Appendix B. MC68HSC705J1A . . . . . . . . . . . . . . . . . . . 141 Appendix C. MC68HSR705J1A . . . . . . . . . . . . . . . . . . . 145 ...

... Appendix A. MC68HRC705J1A . . . . . . . . . . . . . . . . . . . 137 Appendix B. MC68HSC705J1A . . . . . . . . . . . . . . . . . . . 141 Appendix C. MC68HSR705J1A . . . . . . . . . . . . . . . . . . . 145 ...

Aalborg Universitet distribution network

... to provide efficient and flexible interfaces for both distributed generation (DG) units and various electric loads thanks to the emerging power electronics technology [1]. On the other hand, harmonic pollution which stems from nonlinear electronic devices may deteriorate the power quality of the dis ...

... to provide efficient and flexible interfaces for both distributed generation (DG) units and various electric loads thanks to the emerging power electronics technology [1]. On the other hand, harmonic pollution which stems from nonlinear electronic devices may deteriorate the power quality of the dis ...

Hardware and Layout Design Considerations for DDR Memory

... suited for use in mainstream memory interfaces where stubs and connectors are present. The 2.5 V version, named SSTL-2, is prominent with DDR1 memories and is defined within JESD8-9B. The memory controller s drivers and receivers are compatible.with SSTL-2. The most common SSTL termination is the cl ...

... suited for use in mainstream memory interfaces where stubs and connectors are present. The 2.5 V version, named SSTL-2, is prominent with DDR1 memories and is defined within JESD8-9B. The memory controller s drivers and receivers are compatible.with SSTL-2. The most common SSTL termination is the cl ...

Data Manipulation - Cairo University Scholars

... more microprocessors. They are suitable for tasks which require high processing speed, such as medical imaging and computer-aided design. ...

... more microprocessors. They are suitable for tasks which require high processing speed, such as medical imaging and computer-aided design. ...

USB/IP - a Peripheral Bus Extension for Device Sharing

... ability of intelligent peripheral buses (e.g., USB and IEEE1394) is now commonplace. These peripheral buses have advanced features such as serialized I/O, plug-and-play, and universal connectivity. Serialized I/O, which supports devices with a wide range of I/O speeds, minimizes hardware and softwar ...

... ability of intelligent peripheral buses (e.g., USB and IEEE1394) is now commonplace. These peripheral buses have advanced features such as serialized I/O, plug-and-play, and universal connectivity. Serialized I/O, which supports devices with a wide range of I/O speeds, minimizes hardware and softwar ...

GIC Quick Start Guide

... As is described in [2], GICs are induced in the electric power grid when coronal mass ejections (CMEs) on the sun send charged particles towards the earth. These particles interact with the Earth’s magnetic field causing what is known as a geomagnetic disturbance (GMD). So changes in the earth’s ...

... As is described in [2], GICs are induced in the electric power grid when coronal mass ejections (CMEs) on the sun send charged particles towards the earth. These particles interact with the Earth’s magnetic field causing what is known as a geomagnetic disturbance (GMD). So changes in the earth’s ...

TJA1021

... current consumption, the TJA1021 can still be woken up remotely via pin LIN, or woken up locally via pin WAKE_N, or activated directly via pin SLP_N. Filters at the inputs of the receiver (LIN), of pin WAKE_N and of pin SLP_N prevent unwanted wake-up events due to automotive transients or EMI. All w ...

... current consumption, the TJA1021 can still be woken up remotely via pin LIN, or woken up locally via pin WAKE_N, or activated directly via pin SLP_N. Filters at the inputs of the receiver (LIN), of pin WAKE_N and of pin SLP_N prevent unwanted wake-up events due to automotive transients or EMI. All w ...

PRC-002-2 Disturbance Monitoring and Reporting

... 7.2 The phase current for the same phase at the same voltage corresponding to the voltage in Requirement R7, Part 7.1, phase current(s) for any phase-to-phase voltages, or positive sequence current. 7.3 Real Power and Reactive Power flows expressed on a three phase basis corresponding to all circuit ...

... 7.2 The phase current for the same phase at the same voltage corresponding to the voltage in Requirement R7, Part 7.1, phase current(s) for any phase-to-phase voltages, or positive sequence current. 7.3 Real Power and Reactive Power flows expressed on a three phase basis corresponding to all circuit ...

GP100 Pascal Whitepaper

... being interconnected using InfiniBand® and 100 Gb Ethernet to form much larger and more powerful systems. The ratio of GPUs to CPUs has also increased. 2012’s fastest supercomputer, the Titan located at Oak Ridge National Labs, deployed one GK110 GPU per CPU. Today, two or more GPUs are more commonl ...

... being interconnected using InfiniBand® and 100 Gb Ethernet to form much larger and more powerful systems. The ratio of GPUs to CPUs has also increased. 2012’s fastest supercomputer, the Titan located at Oak Ridge National Labs, deployed one GK110 GPU per CPU. Today, two or more GPUs are more commonl ...

installer manual

... The INTEGRA control panels support the following keypads: INT-TSG – touchscreen keypad; INT-KSG – LCD keypad with touch keys; INT-KLCD – LCD keypad with mechanical keys; INT-KLCDR – LCD keypad with mechanical keys and built-in proximity card reader; INT-KLCDK – LCD keypad with mechanical keys; INT-K ...

... The INTEGRA control panels support the following keypads: INT-TSG – touchscreen keypad; INT-KSG – LCD keypad with touch keys; INT-KLCD – LCD keypad with mechanical keys; INT-KLCDR – LCD keypad with mechanical keys and built-in proximity card reader; INT-KLCDK – LCD keypad with mechanical keys; INT-K ...

MIT OpenCourseWare http://ocw.mit.edu 6.189 Multicore

... 512 external E registers (asynchronous vector load/store engine) address management to allow all of external physical memory to be addressed atomic memory operations (fetch&op) support for hardware barriers/eureka to synchronize parallel tasks Prof. Saman Amarasinghe, MIT. ...

... 512 external E registers (asynchronous vector load/store engine) address management to allow all of external physical memory to be addressed atomic memory operations (fetch&op) support for hardware barriers/eureka to synchronize parallel tasks Prof. Saman Amarasinghe, MIT. ...

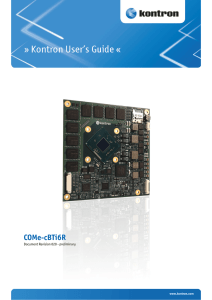

COMe-cBTi6R

... The baseboard designer can optimize exactly how each of these functions implements physically. Designers can place connectors precisely where needed for the application on a baseboard designed to optimally fit a system’s packaging. A single baseboard design can use a range of COM Express® modules wi ...

... The baseboard designer can optimize exactly how each of these functions implements physically. Designers can place connectors precisely where needed for the application on a baseboard designed to optimally fit a system’s packaging. A single baseboard design can use a range of COM Express® modules wi ...

Fault Analysis

... • Simulator defaults zero‐sequence parameters to 2.5 times the positive sequence impedances • PTI assumes that are open in the zero‐ sequence model if no zero‐sequence data is specified in the *.seq data file – When reading in *.seq files, Simulator gives the ability to assume this behavior ...

... • Simulator defaults zero‐sequence parameters to 2.5 times the positive sequence impedances • PTI assumes that are open in the zero‐ sequence model if no zero‐sequence data is specified in the *.seq data file – When reading in *.seq files, Simulator gives the ability to assume this behavior ...

Efficient Data Transfer Protocols for Big Data

... radio telescope that will generate as much or more data than the LHC. In support of the increasing data movement demands, new approaches are needed to overcome the challenges that face existing networking technologies. The ubiquitous Transmission Control Protocol (TCP) is known to have performance p ...

... radio telescope that will generate as much or more data than the LHC. In support of the increasing data movement demands, new approaches are needed to overcome the challenges that face existing networking technologies. The ubiquitous Transmission Control Protocol (TCP) is known to have performance p ...

Cache Behavior of Network Protocols

... to continue (for example, on a cache hit) or to stall (on a cache miss). We have designed and implemented a back end for use with MINT to construct a uniprocessor simulator for our 100 MHz R4400-based SGI Challenge. Figure 1 shows the memory organization for this ...

... to continue (for example, on a cache hit) or to stall (on a cache miss). We have designed and implemented a back end for use with MINT to construct a uniprocessor simulator for our 100 MHz R4400-based SGI Challenge. Figure 1 shows the memory organization for this ...

AN2014 Application note How a designer can make the most of

... used for the non-volatile storage of parameters and fine-granularity data. There is no single memory technology (SRAM, DRAM, EEPROM, Flash Memory, EPROM, ROM) that meets an application’s needs perfectly. Consequently, the designer needs to know the particular strengths and weaknesses of each technol ...

... used for the non-volatile storage of parameters and fine-granularity data. There is no single memory technology (SRAM, DRAM, EEPROM, Flash Memory, EPROM, ROM) that meets an application’s needs perfectly. Consequently, the designer needs to know the particular strengths and weaknesses of each technol ...

BIOS Setup - Dell Community

... Protection Technology that is used in the processors to segregate areas of memory for use by either storage of code instructions or for storage of data. Enable this feature to prevent malicious software and viruses from taking over the system by inserting malicious code into non-executable memory lo ...

... Protection Technology that is used in the processors to segregate areas of memory for use by either storage of code instructions or for storage of data. Enable this feature to prevent malicious software and viruses from taking over the system by inserting malicious code into non-executable memory lo ...

PCA9617A 1. General description Level translating Fm+ I

... voltage (0.8 V to 5.5 V) and higher voltage (2.2 V to 5.5 V) Fast-mode Plus (Fm+) I2C-bus or SMBus applications. While retaining all the operating modes and features of the I2C-bus system during the level shifts, it also permits extension of the I2C-bus by providing bidirectional buffering for both ...

... voltage (0.8 V to 5.5 V) and higher voltage (2.2 V to 5.5 V) Fast-mode Plus (Fm+) I2C-bus or SMBus applications. While retaining all the operating modes and features of the I2C-bus system during the level shifts, it also permits extension of the I2C-bus by providing bidirectional buffering for both ...

Evaluation of Transient Recovery Voltage Issues Associated with the

... This approach includes replacing existing capacitor breakers with those having higher TRV duties and providing an intentional ground to the neutral of the capacitor bank configuration. Approach 3: Combine the above two approaches. ...

... This approach includes replacing existing capacitor breakers with those having higher TRV duties and providing an intentional ground to the neutral of the capacitor bank configuration. Approach 3: Combine the above two approaches. ...

TN-41-13: DDR3 Point-to-Point Design Support

... right memory design methodology can be critical to a project’s success. While DDR3 SDRAM was targeted for use on modules, it can easily be adapted for point-to-point applications. DDR3 is an evolutionary transition from DDR2. DDR3 point-to-point systems are similar to DDR2 point-to-point systems; bo ...

... right memory design methodology can be critical to a project’s success. While DDR3 SDRAM was targeted for use on modules, it can easily be adapted for point-to-point applications. DDR3 is an evolutionary transition from DDR2. DDR3 point-to-point systems are similar to DDR2 point-to-point systems; bo ...

Bus (computing)

In computer architecture, a bus (related to the Latin ""omnibus"", meaning ""for all"") is a communication system that transfers data between components inside a computer, or between computers. This expression covers all related hardware components (wire, optical fiber, etc.) and software, including communication protocols.Early computer buses were parallel electrical wires with multiple connections, but the term is now used for any physical arrangement that provides the same logical functionality as a parallel electrical bus. Modern computer buses can use both parallel and bit serial connections, and can be wired in either a multidrop (electrical parallel) or daisy chain topology, or connected by switched hubs, as in the case of USB.

![PC8349/E [Preliminary]](http://s1.studyres.com/store/data/000076051_1-052fc2cccce23cc32c18f48f9f811182-300x300.png)