Performance Analysis of LLC-LC Resonant Converter Fed

... The closed loop control is carried out using field oriented control approach. Field Oriented Control is based on the machine current and voltage space vectors, the transformation of a three phase speed and time dependent system into a two co-ordinate time invariant system and effective Pulse Width M ...

... The closed loop control is carried out using field oriented control approach. Field Oriented Control is based on the machine current and voltage space vectors, the transformation of a three phase speed and time dependent system into a two co-ordinate time invariant system and effective Pulse Width M ...

LM1084 5A Low Dropout Positive Regulators (Rev. G)

... Stability consideration primarily concerns the phase response of the feedback loop. In order for stable operation, the loop must maintain negative feedback. The LM1084 requires a certain amount series resistance with capacitive loads. This series resistance introduces a zero within the loop to incre ...

... Stability consideration primarily concerns the phase response of the feedback loop. In order for stable operation, the loop must maintain negative feedback. The LM1084 requires a certain amount series resistance with capacitive loads. This series resistance introduces a zero within the loop to incre ...

Document

... Ultra low power consumption 0.18µA TYP at VDD=3V (0.65µA MAX.) Two signal lines (SCL, SDA) required for connection to the CPU. Time counters (counting hours, minutes, and seconds) and calendar counters (counting years, months, days, and weeks) (in BCD format) Interrupt circuit configured to generate ...

... Ultra low power consumption 0.18µA TYP at VDD=3V (0.65µA MAX.) Two signal lines (SCL, SDA) required for connection to the CPU. Time counters (counting hours, minutes, and seconds) and calendar counters (counting years, months, days, and weeks) (in BCD format) Interrupt circuit configured to generate ...

MAX2021 High-Dynamic-Range, Direct Up-/Downconversion 650MHz to 1200MHz Quadrature Mod/Demod General Description

... In addition to offering excellent linearity and noise performance, the MAX2021 also yields a high level of component integration. This device includes two matched passive mixers for modulating or demodulating in-phase and quadrature signals, two LO mixer amplifier drivers, and an LO quadrature split ...

... In addition to offering excellent linearity and noise performance, the MAX2021 also yields a high level of component integration. This device includes two matched passive mixers for modulating or demodulating in-phase and quadrature signals, two LO mixer amplifier drivers, and an LO quadrature split ...

LTC6403-1 - 200MHz, Low Noise, Low Power Fully Differential Input

... test circuit of Figure 1 by applying a voltage on the VOCM pin and testing at both mid supply and at the Electrical Characteristics table limits to verify that the differential gain has not deviated from the mid supply VOCM case by more than 1%, and the common mode offset (VOSCM) has not deviated by ...

... test circuit of Figure 1 by applying a voltage on the VOCM pin and testing at both mid supply and at the Electrical Characteristics table limits to verify that the differential gain has not deviated from the mid supply VOCM case by more than 1%, and the common mode offset (VOSCM) has not deviated by ...

DRV632 数据资料 dataSheet 下载

... DRV632. These capacitors block the dc portion of the audio source and allow the DRV632 inputs to be properly biased to provide maximum performance. These capacitors form a high-pass filter with the input resistor, RIN. The cutoff frequency is calculated using Equation 3. For this calculation, the ca ...

... DRV632. These capacitors block the dc portion of the audio source and allow the DRV632 inputs to be properly biased to provide maximum performance. These capacitors form a high-pass filter with the input resistor, RIN. The cutoff frequency is calculated using Equation 3. For this calculation, the ca ...

Fractional/Integer-N PLL Basics

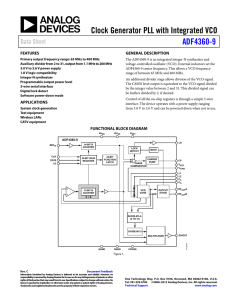

... reprogramming a new value for N) the phase detector will create an error voltage based on the phase difference of the two input signals. This error voltage will change the output frequency of the VCO so that it satisfies Equation 2. As long as the system is in a locked condition the VCO will have th ...

... reprogramming a new value for N) the phase detector will create an error voltage based on the phase difference of the two input signals. This error voltage will change the output frequency of the VCO so that it satisfies Equation 2. As long as the system is in a locked condition the VCO will have th ...

Voltage-reference impact on total harmonic distortion

... pin of SAR ADCs is key when designing dataacquisition systems with low harmonic distortion. The internal circuitry connected to the reference pin of most successive-approximationregister analog-to-digital converters (SAR ADCs) (and some wideband delta-sigma ADCs) consists of switched-capacitor loads ...

... pin of SAR ADCs is key when designing dataacquisition systems with low harmonic distortion. The internal circuitry connected to the reference pin of most successive-approximationregister analog-to-digital converters (SAR ADCs) (and some wideband delta-sigma ADCs) consists of switched-capacitor loads ...

student`s book - Macmillan Education South Africa

... • Explain the frequency selectivity characteristic of RC series circuits (low- and high-pass circuits). • Explain the effects of faulty components in RC circuits. ...

... • Explain the frequency selectivity characteristic of RC series circuits (low- and high-pass circuits). • Explain the effects of faulty components in RC circuits. ...

DS3991 General Description Features

... prevent the transformer from reaching the strike voltage and could potentially cause numerous other problems. Operating with the inverter voltage at too high of a level can be damaging to the inverter components. Proper use of the SVMs can prevent these problems. If desired, the high and/or low SVMs ...

... prevent the transformer from reaching the strike voltage and could potentially cause numerous other problems. Operating with the inverter voltage at too high of a level can be damaging to the inverter components. Proper use of the SVMs can prevent these problems. If desired, the high and/or low SVMs ...

As sine wave generation by using

... current from individual solar panels into alternating currentfor the electric grid. They are grid tie designs by default. Induction heating: Inverters convert low frequency main AC power to higher frequency for use in induction. To do this, AC power is first rectified to provide DC power. The inve ...

... current from individual solar panels into alternating currentfor the electric grid. They are grid tie designs by default. Induction heating: Inverters convert low frequency main AC power to higher frequency for use in induction. To do this, AC power is first rectified to provide DC power. The inve ...

8-Bit, High Bandwidth Multiplying DAC with Serial Interface AD5425

... interface standards. An LDAC pin is also provided, which allows simultaneous updates in a multi-DAC configuration. On power-up, the internal shift register and latches are filled with 0s and the DAC outputs are 0 V. As a result of manufacturing on a CMOS submicron process, this DAC offers excellent ...

... interface standards. An LDAC pin is also provided, which allows simultaneous updates in a multi-DAC configuration. On power-up, the internal shift register and latches are filled with 0s and the DAC outputs are 0 V. As a result of manufacturing on a CMOS submicron process, this DAC offers excellent ...

www.BDTIC.com/TI Designing With Logic SDYA009C June 1997

... Many parameter values in data sheets are not measured when the circuits are tested. The information is based on typical values that have been established experimentally and that are applicable to the majority of devices of the same type or family. In individual cases it might be necessary to interpr ...

... Many parameter values in data sheets are not measured when the circuits are tested. The information is based on typical values that have been established experimentally and that are applicable to the majority of devices of the same type or family. In individual cases it might be necessary to interpr ...

299 8.1 COMBINED ANALOG/DIGITAL COMPUTING ELEMENTS

... and it is supposed to reset when VB becomes more positive than ground. The output of the flip-flop is used to provide the "CARRY" signal to the addFurther, if the time is divided into equal iners in the digital multiplier and to energize the tervals of durationAt and if the digital quantitransistor ...

... and it is supposed to reset when VB becomes more positive than ground. The output of the flip-flop is used to provide the "CARRY" signal to the addFurther, if the time is divided into equal iners in the digital multiplier and to energize the tervals of durationAt and if the digital quantitransistor ...