* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download VI. Transistor amplifiers: Biasing and Small Signal Model

Stray voltage wikipedia , lookup

Signal-flow graph wikipedia , lookup

Electrical substation wikipedia , lookup

Electrical ballast wikipedia , lookup

Flexible electronics wikipedia , lookup

Audio power wikipedia , lookup

Public address system wikipedia , lookup

Mains electricity wikipedia , lookup

Negative feedback wikipedia , lookup

Alternating current wikipedia , lookup

Power MOSFET wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Buck converter wikipedia , lookup

Zobel network wikipedia , lookup

Oscilloscope history wikipedia , lookup

Schmitt trigger wikipedia , lookup

Current source wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Current mirror wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

VI. Transistor amplifiers: Biasing and Small Signal Model

6.1

Introduction

Transistor amplifiers utilizing BJT or FET are similar in design and analysis. Accordingly

we will discuss BJT amplifiers thoroughly. Then, similar FET circuits are briefly reviewed.

Consider the circuit below. The operating point of the BJT is shown in the iC vCE space.

iC

RB

+

iB

+

vBE

vCE

_ _

iE

VBB

RC

VCC

Let us add a sinusoidal source with an amplitude of ∆VBB in series with VBB . In response to

this additional source, the base current will become iB + ∆iB leading to the collector current

of iC + ∆iC and CE voltage of vCE + ∆vCE .

i C +∆ i C

RB

i B +∆ i B

+

+

vBE +∆ vBE _ _

+

− ∆ VBB

~

vCE +∆ vCE

RC

VCC

VBB

For example, assume without the sinusoidal source, the base current is 150 µA, iC = 22 mA,

and vCE = 7 V (the Q point). If the amplitude of ∆iB is 40 µA, then with the addition of

the sinusoidal source iB + ∆iB = 150 + 40 cos(ωt) and varies from 110 to 190 µA. The BJT

operating point should remain on the load line and collector current and CE voltage change

with changing base current while remaining on the load line. For example when base current

is 190 µA, the collector current is 28.6 mA and CE voltage is about 4.5 V. As can be seen

from the figure above, the collector current will approximately be iC +∆iC = 22+6.6 cos(ωt)

and CE voltage is vCE + ∆vCE = 7 − 2.5 cos(ωt).

The above example shows that the signal from the sinusoidal source ∆VBB is greatly amplified

and appears as signals in collector current and CE voltage. It is clear from the figure that

this happens as long as the BJT stays in the active-linear state. As the amplitude of ∆iB

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

158

is increased, the swings of BJT operating point along the load line become larger and larger

and, at some value of ∆iB , BJT will enter either the cut-off or saturation state and the

output signals will not be a sinusoidal function. Note: An important observation is that

one should locate the Q point in the middle of the load line if we want to have the largest

output signal.

The above circuit, however, has two major problems: 1) The input signal, ∆VBB , is in

series with the VBB DC voltage making design of previous two-port network difficult, and

2) The output signal is usually taken across RC as RC × iC . This output voltage has a DC

component which is of no interest and can cause problems in the design of the next-stage,

two-port network.

The DC voltage needed to “bias” the BJT (establish the Q point) and the AC signal of

interest can be added together or separated using capacitor coupling as dis iscussed below.

6.1.1

Capacitive Coupling

For DC voltages (ω = 0), the capacitor is an open circuit (infinite impedance). For AC

voltages, the impedance of a capacitor, Z = −j/(ωC), can be made sufficiently small by

choosing an appropriately large value for C (the higher the frequency, the lower the C value

that one needs). This property of capacitors can be used to add and separate AC and DC

signals. Example below highlights this effect.

+15 V

Consider the circuit below which includes a DC source of

15 V and an AC source of vi = Vi cos(ωt). We are interested to calculate voltages vA and vB . The best method

to solve this circuit is superposition. The circuit is broken into two circuits. In circuit 1, we “kill” the AC source

and keep the DC source. In circuit 2, we “kill” the DC

source and keep the AC source. Superposition principle

states that vA = vA1 + vA2 and vB = vB1 + vB2 .

R2

vA

+

−

vi

C1

+

−

v

B

+15 V

R2

vA1

C1

R1

+

R2

A

+

−

+15 V

vA2

v

R

1

+

B

R1

R2

−

B1

vi

C1

+

−

vi

C1

v

B2

R

1

Consider the first circuit. It is driven by a DC source and, therefore, the capacitor will act

as open circuit. The voltage vA1 = 0 as it is connected to ground and vB1 can be found by

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

159

voltage divider formula: vB1 = 15R1 /(R1 + R2 ). As can be seen both vA1 and vB1 are DC

voltages.

In the second circuit, resistors R1 and R2 are in parallel. Let RB = R1 k R2 . The circuit

is a high-pass filter: VA2 = Vi and VB2 = Vi (RB )/(RB + 1/jωC). If we operate the circuit

at frequency above the cut-off frequency of the filter, i.e., RB 1/ωC, we will have VB2 ≈

VA2 = Vi and vB2 ≈ vA2 = Vi cos(ωt). Therefore, for ω 1/RB C

vA = vA1 + vA2 = Vi cos(ωt)

vB = vB1 + vB2 =

R1

× 15 + Vi cos(ωt)

R1 + R 2

Obviously, the capacitor is preventing the DC voltage to appear at point A, while the voltage

at point B is the sum of DC signal from 15-V supply and the AC signal.

Using capacitive coupling, we can reconfigure our previous amplifier circuit as is shown in

the figure below. Capacitive coupling is used extensively in transistor amplifiers.

vCE +∆ vCE

∆ vCE

i C +∆ i C

∆ VBB

RB

i B +∆ i B

+

+

vBE +∆ vBE _ _

+

−

~

vCE +∆ vCE

RC

VCC

VBB

BJT amplifier circuits are analyzed using superposition, similar to the example above:

1) DC Biasing: The input AC signal is set to zero and capacitors act as open circuit. This

analysis establishes the Q point in the active-linear state.

2) AC Response: DC bias voltages are set to zero. The response of the circuit to an AC

input is calculated and the transfer function, input and output impedances, etc. are found.

The break up of the problem into these two parts have an additional advantage as the

requirement for accuracy are different in the two cases. For DC biasing, we are interested in

locating the Q point roughly in the middle of active-linear state. The exact location of the

Q point is not important. Thus, a simple model, such as large-signal model of page 114 is

quite adequate. We are, however, interested to compute the transfer function for AC signals

more accurately. We will develop a model which is more accurate for small AC signals in

this section.

FET-based amplifiers are similar. FET should be biased similar to BJT and the analysis

method is broken into the DC biasing and the AC response.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

160

6.2

BJT Biasing

VCC

This simple bias circuit is usually referred to as “fixed bias” as a

fixed voltage is applied to the BJT base. As we like to have only one

power supply, the base circuit is also powered by VCC . (To avoid

confusion, we will use capital letters to denote DC bias values e.g.,

IC .) Assuming that BJT is in active-linear state, we have:

BE-KVL:

VCC = IB RB + VBE

→

IB =

RB

RC

iC

+

iB

+

vBE

VCC − VBE

RB

vCE

_ _

VCC − VBE

RB

= IC RC + VCE → VCE = VCC − IC RC

RC

= VCC − β

(VCC − VBE )

RB

IC = βIB = β

CE-KVL:

VCC

VCE

For a given circuit (known RC , RB , VCC , and BJT β) the above equations can be solved to

find the Q-point (IB , IC , and VCE ). Alternatively, one can use the above equations to design

a BJT circuit to operate at a certain Q point. (Note: Do not memorize the above equations

or use them as formulas, they can be easily derived from simple KVLs).

Example 1: Find values of RC , RB in the above circuit with β = 100 and VCC = 15 V so

that the Q-point is IC = 25 mA and VCE = 7.5 V.

Since the BJT is in the active-linear state (VCE = 7.5 > Vγ ), IB = IC /β = 0.25 mA. BE-KVL

and CE-KVL result in:

BE-KVL:

VCC + RB IB + VBE = 0

CE-KVL:

VCC = IC RC + VCE

→

15 − 0.7

= 57.2 kΩ

0.250

15 = 25 × 10−3 RC + 7.5 →

→

RB =

RC = 300 Ω

Example 2: Consider the circuit designed in example 1. What is the Q point if β = 200.

We have RB = 57.2 kΩ, RC = 300 Ω, and VCC = 15 V but IB , IC , and VCE are unknown.

Assuming that the BJT is in the active-linear state:

BE-KVL:

VCC + RB IB + VBE = 0

→

IB =

VCC − VBE

= 0.25 mA

RB

IC = β IB = 50 mA

CE-KVL:

VCC = IC RC + VCE

→

VCE = 15 − 300 × 50 × 10−3 = 0

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

161

As VCE < vγ the BJT is not in the active-linear state (since IC > 0, the BJT should be in

saturation).

The above examples show the problem with our simple fixed-bias circuit as the β of a

commercial BJT can depart by a factor of 2 from its average value given in the manufacturers’

spec sheet. More importantly, environmental conditions (mainly temperature) can play an

important role. In a given BJT, IC increases by 9% per ◦ C for a fixed VBE (because of the

change in β). Consider a circuit which is tested to operate perfectly at 25◦ C. At 35◦ C, β

and IC will be roughly doubled and the BJT can be in saturation! In fact, the circuit has a

build-in positive feedback. If the temperature rises slightly, the corresponding increase in β

makes IC larger. Since the power dissipation in the transistor is VCE IC , the transistor may

get hotter which increases transistor β and IC further and can cause a “thermal runaway.”

The problem is that our biasing circuit fixes the value of IB (independent of BJT parameters)

and, as a result, both IC and VCE are directly proportional to BJT β (see formulas in the

previous page). A biasing scheme should be found that make the Q-point (IC and VCE )

independent of transistor β and insensitive to the above problems → Use negative feedback!

6.2.1

Voltage-Divider Biasing

VCC

This biasing scheme can be best analyzed and understood if we replace R1 and R2 of the voltage divider with its Thevenin equivalent:

VBB

R2

VCC

=

R1 + R 2

R1

RC

iC

and RB = R1 k R2

+

vBE

Analysis below also shows that the Q point is independent of BJT

parameters:

IE ≈ IC = βIB

vCE

_ _

R2

RE

Thevenin

Equivalent

VCC

{

The emitter resistor, RE , provides the negative feedback. Suppose

IC becomes larger than the designed value (e.g., larger β due to an

increase in temperature). Then, VE = RE IE will increase. Since

VBB and RB do not change, KVL in the BE loop shows that IB

should decrease which will reduce IC back towards its design value.

If IC becomes smaller than its design value opposite happens, IB

has to increase which will increase and stabilize IC .

RC

iC

RB

+

−

+

iB

+

vBE

VBB

vCE

_ _

RE

VBB − VBE

RB + βRE

BE-KVL:

VBB = RB IB + VBE + IE RE

→

IB =

CE-KVL:

VCC = RC IC + VCE + IE RE

→

VCE = VCC − IC (RC + RE )

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

+

iB

162

Choose RB such that RB βRE (this is the condition for the feedback to be effective):

IC ≈ I E ≈

VBB − VBE

RE

VBB − VBE

βRE

RC + R E

(VBB − VBE )

−

RE

and IB ≈

VCE = VCC − IC (RC + RE ) ≈ VCC

Note that now both IC and VCE are independent of β.

Another way to see how the circuit works is to consider BE-KVL: VBB = RB IB +VBE +IE RE .

If we choose RB βRE ≈ (IE /IB )RE or RB IB IE RE (rhe feedback condition above),

the KVL reduces to VBB ≈ VBE + IE RE , forcing a constant IE independent of the BJT β.

As IC ≈ IE this will also fixes the Q point of BJT. If the BJT parameters change (different

β due to a change in temperature), the circuit forces IE to remain fixed and changes IB

accordingly. This biasing scheme is one of several methods which fix IC (and VCE ) and allow

the BJT to adjust IB (through negative feedback) to achieve the proper bias. This class of

biasing methods is usually called “self-bias” schemes.

Another important point follows from VBB ≈ VBE + IE RE . As VBE is not a constant and

can change slightly (can drop to 0.6 or increase to 0.8 V for a Si BJT), we need to ensure

that IE RE is much larger than possible changes in VBE . As changes in VBE = vγ is about

0.1 V, we need to ensure that VE = IE RE 0.1 or VE > 10 × 0.1 = 1 V.

Example: Design a stable bias circuit with a Q point of IC = 2.5 mA and VCE = 7.5 V.

Transistor β ranges from 50 to 200.

Step 1: Find VCC : As we like to have the Q-point to be located in the middle of the load

line, we set VCC = 2VCE = 2 × 7.5 = 15 V.

Step 2: Find RC and RE :

VCE = VCC − IC (RC + RE )

→

RC + RE =

7.5

= 3 kΩ

2.5 × 10−3

We are free to choose RC and RE (usually the AC response sets the values of RC and RE as is

discussed later). We have to ensure, however, that VE = IE RE > 1 V or RE > 1/IE = 400 Ω.

Let’s choose RE = 1 kΩ which gives RC = 3 − RE = 2 kΩ (both commercial values).

Step 3: Find RB and VBB : We need to set RB βRE . As any commercial BJT has a range

of β values and we want to ensure that the above inequality is always satisfied, we should

use the minimum β value:

RB βmin RE

→

RB = 0.1βmin RE = 0.1 ∗ 50 ∗ 1, 000 = 5 kΩ

VBB ≈ VBE + IE RE = 0.7 + 2.5 × 10−3 × 103 = 3.2 V

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

163

Step 4: Find R1 and R2

R1 R2

= 5 kΩ

R1 + R 2

R2

3.2

=

=

= 0.21

R1 + R 2

15

RB = R 1 k R 2 =

VBB

VCC

The above are two equations in two unknowns (R1 and R2 ). The easiest way to solve these

equations are to divide the two equations to find R1 and use that in the equation for VBB :

R1 =

5 kΩ

= 24 kΩ

0.21

R2

= 0.21

R1 + R 2

→

0.79R2 = 0.21R1

→

R2 = 6.4 kΩ

Reasonable commercial values for R1 and R2 are and 24 kΩ and 6.2 kΩ, respectively.

The voltage divider biasing scheme is used frequently in BJT amplifiers. There are two

drawbacks to this biasing scheme that may make it unsuitable for some applications:

1) Because VB > 0, a coupling capacitor is needed to attach the input signal to the amplifier

circuit. As a result, this biasing scheme leads to an “AC” amplifier (cannot amplify DC

signals). In some applications, we need “DC” amplifiers. Biasing with two voltage sources,

discussed below, can solve this problem.

2) The voltage divider biasing requires 3 resistors (R1 , R2 , and RE ), and a coupling capacitor.

In ICs, resistors and large capacitors take too much space compared to transistors. It is

preferable to reduce their numbers as much as possible. For IC applications, “currentmirrors” are usually used to bias BJT amplifiers as is discussed below.

6.2.2

Biasing with 2 Voltage Sources

VCC

This biasing scheme is also a self-bias method and is similar

to the voltage-divider biasing. Basically, we have assigned a

voltage of −VEE to the ground (reference voltage) and chosen

VEE = VBB . As such, all of the currents and voltages in the

circuit should be identical to the voltage-divider biasing. We

should find that this is a stable bias point as long as RB βRE .

BE-KVL:

RB IB + VBE + RE IE − VEE = 0

IE

+ RE IE = VEE − VBE →

RB

β

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

IE =

VEE − VBE

RE + RB /β

RC

iC

RB

+

iB

+

vBE

vCE

_ _

RE

−VEE

164

Similar to the bias with one power supply, if we choose RB such that, RB βRE , we get:

VEE − VBE

= const

RE

= RC IC + VCE + RE IE − VEE

IC ≈ I E ≈

CE-KVL:

VCC

VCE = VCC + VEE − IC (RC + RE ) = const

Therefore, IC , and VCE are independent β and bias point is stable. Similar to the voltagedivider bias, we need to ensure that RE IE ≥ 1 V to account for possible variation in VBE .

Bias with two power supplies has certain advantages over biasing with one power supply, it

has two resistors, RB and RE (as opposed to three), and in fact, in most applications, we can

remove RB altogether and directly couple the input signal (without a coupling capacitor) to

the BJT). As such, such a configuration can also amplify “DC” signals.

6.2.3

Biasing in ICs: Current Mirrors

VCC

The self-bias schemes above, voltage-divider and bias with 2 voltage

sources, essentially operate the same way: They force IE to have

a given value independent of the BJT parameters. In principle, the

same objective can be achieved if we could bias the BJT with a current

source as is shown. In this case, no bias resistor is needed and we only

need to include resistors necessary for AC operation. As such, biasing

with a current source is the preferred way in most integrated circuits.

Such a biasing can be achieved with a current mirror circuit.

Consider the circuit shown with two identical transistors, Q1

and Q2 . Because both bases and emitters of the transistors

are connected together, KVL leads to vBE1 = vBE2 . As BJT’s

are identical, they should have similar iB (iB1 = iB2 = iB )

and, therefore, similar iE = iE1 = iE2 and iC = iC1 = iC2

KCL:

iE

β+1

βiE

β+1

2iE

iE

2iE

β+2

Iref = iC +

=

+

=

iE

β+1

β+1 β+1

β+1

Io

β

1

=

=

Iref

β+2

1 + 2/β

iB =

Io = i C =

RC

iC

RB

+

iB

+

vBE

vCE

_ _

RE

I

−VEE

I ref

2iE

Io

β +1

iC

iC

Q1

_

iE

+

+

vBE2 _

vBE1

−VEE

Q2

iE

We have explicitly used iC = βiB and iE = (β + 1)iB to illustrate the impact of β.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

165

For β 1, Io ≈ Iref (with an accuracy of 2/β). This circuit is called a “current mirror”

as the two transistors work in tandem to ensure that current Io remains the same as Iref

no matter what circuit is attached to the collector of Q2 . As such, the circuit behaves as

a current source and can be used to bias BJT circuits, i.e., Q2 collector is attached to the

emitter circuit of the BJT amplifier to be biased.

VCC

Value of Iref can be set in many ways. The simplest is by using

a resistor Rc as is shown. By KVL, we have:

RC

Io

iC

VCC = RC Iref + vBE1 − VEE

Iref

I ref

Q1

VCC + VEE − vBE1

=

= const

RC

_

iE

+

+

vBE2 _

vBE1

−VEE

Q2

iE

Current mirror circuits are widely used for biasing BJTs. In the simple current mirror circuit

above, Io = Iref with a relative accuracy of 2/β and Iref is constant with an accuracy of

small changes in vBE1 . Variations of the above simple current mirror, such as Wilson current

mirror and Widlar current mirror, have Io = Iref even with a higher accuracy and also

compensate for the small changes in vBE . Wilson mirror is especially popular because it

replace Rc with a transistor.

The right hand part of the current mirror circuit can be duplicated such that one current

mirror circuit can bias several BJT circuits as is shown. In fact, by coupling output of two

or more of the right hand BJTs, integer multiples of Iref can be made for biasing circuits

which require a higher bias current.

VCC

RC

I ref

Io

Io

2Io

−VEE

A large family of BJT circuit, including current mirrors, differential amplifiers, and emittercoupled logic circuits include identical BJT pairs. These circuits are rarely made of discrete

transistors because if one chooses two commercial BJTs, e.g., two 2N3904, there is no guaranty that β1 = β2 . However, if two identical BJTs are manufactured together on one chip

next to each other, β1 ≈ β2 within a couple of percent.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

166

6.3

Biasing FETs

Field-effect transistors can also be used in amplifier circuits by operating the FET in the

active state. Similar to BJT amplifiers, we need to apply a DC bias (in addition to the input

AC signal) so that the FET remains in the active state for the entire period of the AC signal.

VGG

The fixed-bias scheme for FETs is shown. Note that RG is not necessary

for biasing but is necessary for AC operation as without RG the input

AC signal will be grounded through VGG .

GS-KVL:

VDD

RD

RG

VGG = VGS

ID = K(VGS − Vt )2 = K(VGG − Vt )2

DS-KVL:

VDD = ID RD + VDS

→

VDS = VDD − KRD (VGG − Vt )2

Similar to the BJT β, both Vt and K vary due to the manufacturing and environmental

conditions. For example, as temperture is increased, both Vt and K decrease: decreasing

K decreases ID while decreasing Vt raises ID . The net effect (usually) is that ID decreases.

While the “thermal runaway” is not a problem in FETs, the bias point is not stable.

Similar to the BJT bias circuits, addition of a resistor RS provides the negative feedback

necessary to stabilize the bias point. For the voltage divider self bias, VG is set by R1 and R2 .

Since VGS = VG − RS ID , any decrease in ID would increase VGS and increases ID . Similarly,

any increase in ID would decrease VGS and decreases ID . As a result, ID will stay nearly

constant (because ID = K(VGS − Vt )2 , ID does not remain constant like IC in a BJT, rather

it variation become much smaller by the negative feedback). Another difference between

voltage-divider self-bias for FET with that of BJT si that in the case of BJT, we have to

ensure that RB βRE for negative feedback to be effective. THis generally limits the value

of R1 and R2 . In a FET, IG = 0 and no such limitaion exists. Therefore, R1 and R2 can be

taken to be large (MΩ) which is important in the AC response as is discussed later.

Self bias with 2 power supplies and FET current mirror bias are also shown below.

R2

RD

RD

iD

iD

R1

RS

VDD

VDD

VDD

R1

R

Io

I ref

RS

−VSS

Voltage-divider (Self Bias)

Bias with 2 power supplies

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

FET Current Mirror

167

6.4

BJT Small Signal Model

We calculated the DC behavior

of the BJT (DC biasing) with a

simple large-signal model. In the

active-linear state, this model is

simply: vBE = 0.7 V, iC = βiB .

This model is sufficient for calculating the Q point as we are only

interested in ensuring sufficient design space for the amplifier, i.e.,

Q point should be in the middle

of the load line in the active-linear

state. In fact, for our good biasing scheme with negative feedback,

the Q point location is independent

of BJT parameters (and, therefore,

independent of model used!).

iB

iC

vγ

vBE

vsat

vCE

A comparison of the simple largesignal model with the iv characteristics of the BJT shows that our

simple large-signal model is crude.

For example, the input AC signal results in small changes in vBE around 0.7 V (Q point) and

corresponding changes in iB . The simple model cannot be used to calculate these changes

(It assumes vBE is constant!). Also for a fixed iB , iC is not exactly constant as is assumed

in the simple model (see iC vs vCE graphs). As a whole, the simple large signal model is not

sufficient to describe the AC behavior of BJT amplifiers where more accurate representations

of the amplifier gain, input and output resistance, etc. are needed.

A more accurate, but still linear, model can be developed by assuming that the changes in

transistor voltages and currents due to the AC signal are small compared to corresponding

Q-point values and using a Taylor series expansion. Consider function f (x). Suppose we

know the value of the function and all of its derivative at some known point x0 . Then,

the value of the function in the neighborhood of x0 can be found from the Taylor Series

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

168

expansion as:

df (∆x)2 d2 f f (x0 + ∆x) = f (x0 ) + ∆x

+ ...

+

dx x=x0

2 dx2 x=x0

Close to our original point of x0 , ∆x is small and the high order terms of this expansion

(terms with (∆x)n , n = 2, 3, ...) usually become very small. Typically, we consider only the

first order term, i.e.,

df f (x0 + ∆x) ≈ f (x0 ) + ∆x

dx x=x0

The Taylor series expansion can be similarly applied to function of two or more variables

such as f (x, y):

∂f ∂f f (x0 + ∆x, y0 + ∆y) ≈ f (x0 , y0 ) + ∆x

+ ∆y

∂x x0 ,y0

∂y x0 ,y0

In a BJT, there are four parameters of interest: iB , iC , vBE , and vCE . The BJT iv characteristics plots, specify two of the above parameters, vBE and iC in terms of the other two,

iB and vCE , i.e., vBE is a function of iB and vCE (written as vBE (iB , vCE ) similar to f (x, y))

and iC is a function of iB and vCE , iC (iB , vCE ).

Let’s assume that BJT is biased and the Q point parameters are IB , IC , VBE and VCE . We

now apply a small AC signal to the BJT. This small AC signal changes vCE and iB by small

values around the Q point:

iB = IB + ∆iB

vCE = VCE + ∆vCE

The AC changes, ∆iB and ∆vCE results in AC changes in vBE and iC that can be found

from Taylor series expansion in the neighborhood of the Q point, similar to expansion of

f (x0 + ∆x, y0 + ∆y) above:

vBE (IB + ∆iB , VCE + ∆vCE ) = VBE

iC (IB + ∆iB , VCE

∂vBE ∂vBE +

∆iB +

∆vCE

∂iB Q

∂vCE Q

∂iC ∂iC + ∆vCE ) = IC +

∆iB +

∆vCE

∂iB Q

∂vCE Q

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

169

where all partial derivatives are calculated at the Q point and we have noted that at the Q

point, vBE (IB , VCE ) = VBE and iC (IB , VCE ) = IC . We denote the AC changes in vBE and iC

as ∆vBE and ∆iC , respectively:

vBE (IB + ∆iB , VCE + ∆vCE ) = VBE + ∆vBE

iC (IB + ∆iB , VCE + ∆vCE ) = IC + ∆iC

So, by applying a small AC signal, we have changed iB and vCE by small amounts, ∆iB and

∆vCE , and BJT has responded by changing , vBE and iC by small AC amounts, ∆vBE and

∆iC . From the above two sets of equations we can find the BJT response to AC signals:

∆vBE =

∂vBE

∂vBE

∆iB +

∆vCE ,

∂iB

∂vCE

∆iC =

∂iC

∂iC

∆iB +

∆vCE

∂iB

∂vCE

where the partial derivatives are the slope of the iv curves near the Q point. We define

hie ≡

∂vBE

,

∂iB

hre ≡

∂vBE

,

∂vCE

hf e ≡

∂iC

,

∂iB

hoe ≡

∂iC

∂vCE

Thus, response of BJT to small signals can be written as:

∆vBE = hie ∆iB + hre ∆vCE

∆iC = hf e ∆iB + hoe ∆vCE

which is our small-signal model for BJT.

We now need to relate the above analytical model to circuit elements so that we can solve

BJT circuits. Consider the expression for ∆vBE

∆vBE = hie ∆iB + hre ∆vCE

Each term on the right hand side should have units of Volts. Thus, hie should have units of

resistance and hre should have no units (these are consistent with the definitions of hie and

hre ). Furthermore, the above equation is like a KVL: the voltage drop between the base and

emitter (∆vBE ) is equal to the sum of voltage drops across two elements. The voltage drop

across the first element is hie ∆iB . So, it is a resistor with a value of hie . The voltage drop

across the second element is hre ∆vCE . Thus, it is a dependent voltage source.

B

∆i

Β +

+

∆v

E

V1 = hie ∆ iB

−

ΒΕ

−

+

V2 = hre ∆ v

CE

B

Β

E

h ie

+

∆v

−

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

∆i

ΒΕ

hre ∆v CE

+

−

−

170

Now consider the expression for ∆iC :

∆iC = hf e ∆iB + hoe ∆vCE

Each term on the right hand side should have units of Amperes. Thus, hf e should have no

units and hoe should have units of conductance (these are consistent with the definitions of

hoe and hf e .) Furthermore, the above equation is like a KCL: the collector current (∆iC )

is equal to the sum of two currents. The current in first element is hf e ∆iB . So, it is a

dependent current source. The current in the second element is proportional to hoe /∆vCE .

So it is a resistor with the value of 1/hoe .

∆i

C

+

i1 = h fe ∆ iB

∆v

i = h oe ∆v

2

CE

∆i

C

C

1/hoe

CE

−

C

+

hfe ∆ iB

∆v

CE

−

E

E

Now, if put the models for BE and CE terminals together we arrive at the small signal

“hybrid” model for BJT. It is similar to the hybrid model for a two-port network.

∆i

B

B

+

∆v

E

BE

_

∆i

h ie

hre ∆v CE

C

+

-

C

+

hfe ∆ iB

1/hoe

∆v

CE

-

E

The small-signal model is mathematically valid only for signals with small amplitudes. But

this model is so useful that is often used for signals with amplitudes approaching those of

Q-point parameters by using average values of “h” parameters. “h” parameters are given in

the manufacturer’s spec sheets for each BJT. It should not be surprising to note that even in

a given BJT, “h” parameter can vary substantially depending on manufacturing statistics,

operating temperature, etc. Manufacturer’s’ spec sheets list these “h” parameters and give

the minimum and maximum values. Traditionally, the geometric mean of the minimum and

maximum values are used as the average value in design (see the table below).

Since hf e = ∂iC /∂iB and BJT β = iC /iB , β is sometimes called hF E in manufacturers’ spec

sheets and has a value quite close to hf e . In most electronic text books, β, hF E and hf e are

used interchangeably.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

171

Typical hybrid parameters of a general-purpose 2N3904 NPN BJT

Minimum

1

0.5 × 10−4

100

1

25

10

rπ = hie (kΩ)

hre

β ≈ hf e

hoe (µS)

ro = 1/hoe (kΩ)

re = hie /hf e (Ω)

Maximum

10

8 × 10−4

400

40

1,000

25

Average*

3

2 × 10−4

200

6

150

15

* Geometric mean.

As hre is small, it is usually ignored in analytical calculations as it makes analysis much

simpler. This model, called the hybrid-π model, is most often used in analyzing BJT circuits.

In order to distinguish this model from the hybrid model, most electronic text books use a

different notation for various elements of the hybrid-π model:

rπ = hie

B

∆i

∆i

B

C

+

∆v

BE

ro =

C

1

hoe

β = hf e

B

∆i

∆i

B

C

+

hfe ∆ iB

h ie

1/hoe

_

∆v

BE

=⇒

β∆ i

rπ

B

C

ro

_

E

E

The above hybrid-π model includes a current-controlled current source. A variant of the

hybrid-π model can be developed which includes a voltage-controlled current source by noting

(∆vBE = rπ ∆iB :

β∆iB = β

∆vBE

= gm ∆vBE

rπ

β

Transfer conductance

rπ

rπ

1

=

Emitter resistance

re ≡

gm

β

gm ≡

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

B

∆i

∆i

B

C

+

∆v

BE

gm ∆ vBE

rπ

C

ro

_

E

172

6.5

FET Small Signal Model

Similar to the BJT, the simple large-signal model of FET (page 127) is sufficient for finding

the bias point; but we need to develop a more accurate model for analysis of AC signals.

The main issue is that the FET large signal model indicates that iD only depends on vGS

and is independent of vDS in the active state. In reality, iD increases slightly with vDS in

the active state.

We can develop a small signal model for FET in a manner similar to the procedure described

in detail for the BJT. The FET characteristics equations specify two of the FET parameters,

iG and iD , in terms of the other two, vGS and vDS . (Actually FET is simpler than BJT as

iG = 0 at all times.) As before, we write the FET parameters as a sum of DC bias value

and a small AC signal, e.g., iD = ID + ∆iD . Performing a Taylor series expansion, similar

to pages 169 and 170, we get:

iG (VGS + ∆vGS , VDS + ∆vDS ) = 0

iD (VGS

∂iD ∂iD ∆vGS +

∆vDS

+ ∆vGS , VDS + ∆vDS ) = iD (VGS , VDS ) +

∂vGS Q

∂vDS Q

Since iG (VGS +∆vGS , VDS +∆vDS ) = IG +∆iG and iD (VGS +∆vGS , VDS +∆vDS ) = ID +∆iD ,

we find the AC components to be:

∆iG = 0

and

Defining

gm ≡

∂iD

∂vGS

and

∂iD ∂iD ∆iD =

∆vGS +

∆vDS

∂vGS Q

∂vDS Q

ro ≡

∂iD

∂vDS

We get:

∆iG = 0

and

∆iD = gm ∆vGS + ro ∆vDS

This results in the hybrid-π model for

the FET as is shown. Note that the

FET hybrid-π model is similar to the BJT

hybrid-π model with rπ → ∞.

G

∆i = 0

∆i

G

D

D

gm ∆ vGS

+

∆v

GS

_

ro

S

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

173

6.6

BJT Amplifier Circuits

As we have developed different models for DC signals (simple large-signal model) and AC

signals (small-signal model), analysis of BJT circuits follows these steps:

DC biasing analysis: Assume all capacitors are open circuit. Analyze the transistor circuit

using the simple large signal mode as described in page 114.

AC analysis:

1) Kill all DC sources

2) Assume coupling capacitors are short circuit. The effect of these capacitors is to set a

lower cut-off frequency for the circuit. This is analyzed in the last step.

3) Inspect the circuit. If you identify the circuit as a prototype circuit, you can directly use

the formulas for that circuit. Otherwise go to step 4.

4) Replace the BJT with its small signal model.

5) Solve for voltage and current transfer functions and input and output impedances (nodevoltage method is the best).

6) Compute the cut-off frequency of the amplifier circuit.

Several standard BJT amplifier configurations are discussed below and are analyzed. For

completeness, circuits include standard bias resistors R1 and R2 . For bias configurations

that do not utilize these resistors (e.g., current mirror), simply set RB = R1 k R2 → ∞.

6.6.1

Common Collector Amplifier (Emitter Follower)

VCC

DC analysis: With the capacitors open circuit, this circuit is the

same as our good biasing circuit of page 162 with RC = 0. The

bias point currents and voltages can be found using procedure

of pages 162-164.

R1

vi

Cc

vo

AC analysis: To start the analysis, we kill all DC sources:

R2

RE

VCC = 0

R1

vi

Cc

vi

Cc

vo

R2

RE

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

C

B

vo

E

R1

R2

RE

174

We can combine R1 and R2 into RB (same resistance that we encountered in the biasing

analysis) and replace the BJT with its small signal model:

vi

Cc

B

∆i

∆i

B

C

+

∆v

RB

BE

β ∆i

rπ

B

Cc

rπ

B

E

vo

∆i

ro

RB

vo

E

_

vi

C

B

RE

ro

β ∆i

B

C

RE

The figure above shows why this is a common collector configuration: the collector is common

between the input and output AC signals. We can now proceed with the analysis. Node

voltage method is usually the best approach to solve these circuits. For example, the above

circuit has only one node equation for node at point E with a voltage vo :

vo − v i vo − 0

vo − 0

+

− β∆iB +

=0

rπ

ro

RE

Because of the controlled source, we need to write an “auxiliary” equation relating the control

current (∆iB ) to node voltages:

∆iB =

vi − v o

rπ

Substituting the expression for ∆iB in our node equation, multiplying both sides by rπ , and

collecting terms, we get:

vi (1 + β) = vo 1 + β + rπ

1

1

+

ro RE

= vo

"

rπ

1+β+

ro k R E

#

Amplifier Gain can now be directly calculated:

Av ≡

vo

=

vi

1+

1

rπ

(1 + β)(ro k RE )

Unless RE is very small (tens of Ω), the fraction in the denominator is quite small compared

to 1 and Av ≈ 1.

To find the input impedance, we calculate ii by KCL:

ii = i1 + ∆iB =

vi − v o

vi

+

RB

rπ

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

175

Since vo ≈ vi , we have ii = vi /RB or

Ri ≡

vi

= RB

ii

Note that RB is the combination of our biasing resistors R1 and R2 . With alternative biasing

schemes which do not require R1 and R2 (and, therefore, RB → ∞), the input resistance of

the emitter follower circuit will become large. In this case, we cannot use vo ≈ vi . Using the

full expression for vo from above, the input resistance of the emitter follower circuit becomes:

Ri ≡

vi

= RB k [rπ + (RE k ro )(1 + β)]

ii

which is quite large (hundreds of kΩ to several MΩ) for RB → ∞. Such a circuit is in fact

the first stage of the 741 OpAmp.

The output resistance of the common collector amplifier (in fact for all transistor amplifiers)

is somewhat complicated because the load can be configured in two ways (see figure): First,

RE , itself, is the load. This is the case when the common collector is used as a “current

amplifier” to raise the power level and to drive the load. The output resistance of the circuit

is Ro as is shown in the circuit model. This is usually the case when values of Ro and Ai

(current gain) is quoted in electronic text books.

VCC

VCC

R1

R1

Cc

vi

vi

Cc

vo

R2

vo

RE = RL

R2

RE is the Load

vi

Cc

rπ

B

B

vo

vi

Cc

rπ

B

E

∆i

β∆ i

B

ro

RL

Separate Load

E

∆i

RB

RE

RE

C

RB

B

vo

β∆ i

B

ro

RE

RL

C

Ro

R’o

Alternatively, the load can be placed in parallel to RE . This is done when the common

collector amplifier is used as a buffer (Av ≈ 1, Ri large). In this case, the output resistance

is denoted by Ro0 (see figure). For this circuit, BJT sees a resistance of RE k RL . Obviously,

if we want the load not to affect the emitter follower circuit, we should use RL to be much

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

176

larger than RE . In this case, little current flows in RL which is fine because we are using

this configuration as a buffer and not to amplify the current and power. As such, value of

Ro0 or Ai does not have much use.

Cc

vi

When RE is the load, the output resistance can

be found by killing the source (short vi ) and finding the Thevenin resistance of the two-terminal

network (using a test voltage source).

rπ

B

∆i

β∆ iB

B

RB

iT

E

+

−

ro

vT

C

Ro

vT

KCL:

iT = −∆iB +

− β∆iB

ro

KVL (outside loop):

− rπ ∆iB = vT

Substituting for ∆iB from the 2nd equation in the first and rearranging terms we get:

Ro ≡

(ro ) rπ

vT

=

iT

(1 + β)(ro ) + rπ

Since, (1 + β)(ro ) rπ , the expression for Ro simplifies to

Ro ≈

rπ

rπ

(ro ) rπ

=

≈

= re

(1 + β)(ro )

(1 + β)

β

As mentioned above, when RE is the load the common collector is used as a “current amplifier” to raise the current and power levels . This can be seen by checking the current gain

in this amplifier: io = vo /RE , ii ≈ vi /RB and

Ai ≡

io

RB

=

ii

RE

We can calculate Ro0 , the output resistance

when an additional load is attached to the circuit (i.e., RE is not the load) with a similar

procedure: we need to find the Thevenin resistance of the two-terminal network (using a

test voltage source).

We can use our previous results by noting that

we can replace ro and RE with ro0 = ro k RE

which results in a circuit similar to the case

with no RL . Therefore, Ro0 has a similar expression as Ro if we replace ro with ro0 :

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

vi

Cc

rπ

B

∆i

β∆ iB

B

RB

iT

E

ro

+

−

RE

vT

C

R’o

vi

Cc

rπ

B

∆i

RB

B

iT

E

β∆ iB

+

−

r’o

vT

C

R’o

177

Ro0

vT

(ro0 ) rπ

≡

=

iT

(1 + β)(ro0 ) + rπ

In most circuits, (1 + β)(ro0 ) rπ (unless we choose a small value for RE ) and Ro0 ≈ re

In summary, the general properties of the common collector amplifier (emitter follower)

include a voltage gain of unity (Av ≈ 1), a very large input resistance Ri ≈ RB (and can

be made much larger with alternate biasing schemes). This circuit can be used as buffer for

matching impedance, at the first stage of an amplifier to provide very large input resistance

(such in 741 OpAmp). The common collector amplifier can be also used as the last stage

of some amplifier system to amplify the current (and thus, power) and drive a load. In this

case, RE is the load, Ro is small: Ro = re and current gain can be substantial: Ai = RB /RE .

Impact of Coupling Capacitor:

Up to now, we have neglected the impact of the coupling capacitor in the circuit (assumed

it was a short circuit). This is not a correct assumption at low frequencies. The coupling

capacitor results in a lower cut-off frequency for the transistor amplifiers. In order to find the

cut-off frequency, we need to repeat the above analysis and include the coupling capacitor

impedance in the calculation. In most cases, however, the impact of the coupling capacitor

and the lower cut-off frequency can be deduced be examining the amplifier circuit model.

Consider our general model for any

amplifier circuit. If we assume that

coupling capacitor is short circuit

(similar to our AC analysis of BJT

amplifier), vi0 = vi .

Vi

Ro

Cc

+

−

+

V’i

−

Ri

+

−

Io

+

AVi

Vo

ZL

−

Voltage Amplifier Model

When we account for impedance of the capacitor, we have set up a high pass filter in the

input part of the circuit (combination of the coupling capacitor and the input resistance of

the amplifier). This combination introduces a lower cut-off frequency for our amplifier which

is the same as the cut-off frequency of the high-pass filter:

ωl = 2π fl =

1

Ri Cc

Lastly, our small signal model is a low-frequency model. As such, our analysis indicates

that the amplifier has no upper cut-off frequency (which is not true). At high frequencies,

the capacitance between BE , BC, CE layers become important and a high-frequency smallsignal model for BJT should be used for analysis. You will see these models in upper division

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

178

courses. Basically, these capacitances results in amplifier gain to drop at high frequencies.

PSpice includes a high-frequency model for BJT, so your simulation should show the upper

cut-off frequency for BJT amplifiers.

6.6.2

Common Emitter Amplifier

DC analysis: Recall that an emitter resistor is necessary to provide stability of the

bias point. As such, the circuit configuration as is shown has as a poor bias. We

need to include RE for good biasing (DC

signals) and eliminate it for the AC signals. The solution is to include an emitter

resistance and use a “bypass” capacitor to

short it out for AC signals as is shown.

VCC

RC

R1

vi

VCC

vo

Cc

RC

R1

vi

vo

Cc

R2

R2

Cb

RE

Good Bias using a

by−pass capacitor

Poor Bias

For this new circuit and with the capacitors open circuit, this circuit is the same as our

good biasing circuit of page 162. The bias point currents and voltages can be found using

procedure of pages 162-164.

AC analysis: To start the analysis, we kill all DC sources, short out Cb (which shorts out

RE ), combine R1 and R2 into RB , and replace the BJT with its small signal model. We

see that the emitter is now common between the input and output AC signals (thus, the

common emitter amplifier). Examination of the circuit shows that:

vi

vi = rπ ∆iB

vo = −(RC k ro ) β∆iB

vo

β

β

RC

= − (RC k ro ) ≈ − RC = −

vi

rπ

rπ

re

Ri = R B k r π

Cc

B

C

∆i

RB

B

rπ

β∆ iB

vo

RC

ro

Av ≡

E

Ro

R’o

The negative sign in Av indicates a 180◦ phase shift between the input and output signals.

This circuit has a large voltage gain but has a medium value for the input resistance.

As with the emitter follower circuit, the load can be configured in two ways: 1) RC is the

load; or 2) the load is placed in parallel to RC . The output resistance can be found by killing

the source (short vi ) and finding the Thevenin resistance of the two-terminal network. For

this circuit, we see that if vi = 0 (killing the source), ∆iB = 0. In this case, the strength of

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

179

the dependent current source would be zero and this element would become an open circuit.

Therefore,

Ro = r o

Ro0 = RC k ro

Lower cut-off frequency: Both the coupling and bypass capacitors contribute to setting

the lower cut-off frequency for this amplifier, both act as a high-pass filter with:

1

Ri Cc

1

ωl (bypass) = 2π fl = 0

RE Cb

ωl (coupling) = 2π fl =

0

where RE

≡ RE k re

0

Note that usually RE re and, therefore, RE

≈ re .

In the case when these two frequencies are far apart, the cut-off frequency of the amplifier

is set by the “larger” cut-off frequency. i.e.,

ωl (bypass) ωl (coupling)

→

ωl (coupling) ωl (bypass)

→

1

Ri Cc

1

ωl = 2π fl = 0

RE Cb

ωl = 2π fl =

When the two frequencies are close to each other, there is no exact analytical formulas, the

cut-off frequency should be found from simulations. An approximate formula for the cut-off

frequency (accurate within a factor of two and exact at the limits) is:

ωl = 2π fl ≈

1

1

+ 0

Ri Cc RE Cb

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

180

6.6.3

Common Emitter Amplifier with Emitter resistance

VCC

A problem with the common emitter amplifier is that its gain

depend on BJT parameters: Av ≈ (β/rπ )RC . Some form of

feedback is necessary to ensure stable gain for this amplifier.

One way to achieve this is to add an emitter resistance. Recall

impact of negative feedback on OpAmp circuits: we traded gain

for stability of the output. Same principles apply here.

R1

RC

Cc

vo

vi

DC analysis: With the capacitors open circuit, this circuit is the

RE

R2

same as our good biasing circuit of page 162. The bias point

currents and voltages can be found using procedure of pages

162-164.

AC analysis: To start the analysis, we kill all DC sources, combine R1 and R2 into RB and

replace the BJT with its small signal model. Analysis is straight forward using node-voltage

method.

vi

vE − v i

vE

vE − v o

+

− β∆iB +

=0

rπ

RE

ro

vo

vo − v E

+

+ β∆iB = 0

RC

ro

vi − v E

∆iB =

(Controlled source aux. Eq.)

rπ

C1

B

∆i

∆i

B

C

+

∆v

RB

BE

β∆ iB

rπ

_

C

vo

ro

E

RE

RC

Substituting for ∆iB in the node equations and noting 1 + β ≈ β, we get :

vE − v i vE − v o

vE

+β

+

=0

RE

rπ

ro

vo

vo − v E

vE − v i

+

−β

=0

RC

ro

rπ

Above are two equations in two unknowns (vE and vo ). Adding the two equation together

we get vE = −(RE /RC )vo and substituting that in either equations we can find vo . Using

rπ /β = re , we get:

Av =

vo

RC

RC

=

≈

vi

re (1 + RC /ro ) + RE (1 + re /ro )

re (1 + RC /ro ) + RE

where we have simplified the equation noting re ro . For most circuits, RC ro and

re RE . In this case, the voltage gain is simply Av = −RC /RE .

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

181

The input resistance of the circuit can be found from (prove it!)

Ri = R B k

vi

∆iB

Noting that ∆iB = (vi − vE )/rπ and vE = −(RE /RC )vo = −(RE /RC )Av vi , we get:

Ri = R B k

rπ

1 + Av RC /RE

Substituting for Av from above (complete expression for Av with re /ro 1), we get:

"

RE

+ re

Ri = R B k β

1 + RC /ro

!#

For most circuits, RC ro and re RE . In this case, the input resistance is simply

Ri = RB k (βRE ).

As before the minus sign in Av indicates a 180◦ phase shift between input and output

signals. Note the impact of negative feedback introduced by the emitter resistance: The

voltage gain is independent of BJT parameters and is set by RC and RE (recall OpAmp

inverting amplifier!). The input resistance is also increased dramatically.

B

As with the emitter follower circuit, the load can

be configured in two ways: 1) RC is the load. 2)

Load is placed in parallel to RC . The output resistance can be found by killing the source (short

vi ) and finding the Thevenin resistance of the

two-terminal network (by attaching a test voltage

source to the circuit).

iT = −∆iB − i1 = −∆iB 1 +

rπ

RE

vT = −∆iB rπ − i2 ro = −∆iB ro

iT

C

B

β∆ iB

rπ

i2

E

ro

+

−

Ro

B

∆i

iT

C

B

β∆ iB

rπ

i2

E

ro

+

−

RC

rπ

β+1+

RE

vT

RE

i1

Resistor RB drops out of the circuit because it is

shorted out. Resistors rπ and RE are in parallel.

Therefore, i1 = (rπ /RE )∆iB and by KCL, i2 =

(β + 1 + rπ /RE )∆iB . Then:

∆i

i1

+ rπ

vT

RE

R’o

Then:

Ro =

1 + ro /re

vT

= ro + RE ×

iT

1 + RE /rπ

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

182

where we have used rπ /β = re . Generally ro re (first approximation below) and for most

circuit, RE rπ (second approximation) leading to

RE /re

RE ro

RE

Ro ≈ r o + r o ×

≈ ro +

= ro

+1

1 + RE /rπ

re

re

Value of Ro0 can be found by a similar procedure. Alternatively, examination of the circuit

shows that

Ro0 = RC k Ro ≈ RC

Lower cut-off frequency: The coupling capacitor together with the input resistance of

the amplifier lead to a lower cut-off frequency for this amplifier (similar to emitter follower).

The lower cut-off frequency is given by:

ωl = 2π fl =

1

Ri Cc

A Possible Biasing Problem: The gain of the common

emitter amplifier with the emitter resistance is approximately

RC /RE . For cases when a high gain (gains larger than 5-10) is

needed, RE may be become so small that the necessary good

biasing condition, VE = RE IE > 1 V cannot be fulfilled. The

solution is to use a by-pass capacitor as is shown. The AC signal

sees an emitter resistance of RE1 while for DC signal the emitter

resistance is the larger value of RE = RE1 + RE2 . Obviously formulas for common emitter amplifier with emitter resistance can

be applied here by replacing RE with RE1 as in deriving the amplifier gain, and input and output impedances, we “short” the

bypass capacitor so RE2 is effectively removed from the circuit.

VCC

R1

RC

Cc

vo

vi

R2

R E1

R E2

Cb

The addition of by-pass capacitor, however, modifies the lower cut-off frequency of the circuit.

Similar to a regular common emitter amplifier with no emitter resistance, both the coupling

and bypass capacitors contribute to setting the lower cut-off frequency for this amplifier.

Similarly we find that an approximate formula for the cut-off frequency (accurate within a

factor of two and exact at the limits) is:

ωl = 2π fl =

1

1

+ 0

Ri Cc RE Cb

0

where RE

≡ RE2 k (RE1 + re )

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

183

6.6.4

Common Base Amplifier

VCC

By setting the signal ground at the base of the BJT, one arrives

at the common base amplifier (the input sginal is still applied

between the base and the emitter). While it is possible to bias

this configuration with a voltage divider self-bias, the preferred

method is to bias this amplifier with two power supplies (or a

current mirror). The bias point currents and voltages can be

found using procedure of pages 164-165.

RC

vo

vi

Cc

AC analysis: To start the analysis, we kill all DC sources and

replace the BJT with its small signal model. We see that base

is now common between the input and output AC signals (thus,

the common base amplifier).

∆i

B

B

β ∆ iB

rπ

vi

ro

=⇒

RC

vi

E

ii

E

∆i

RE

C

Cc

B

Cc

−VEE

β ∆ iB

vo

C

RE

rπ

RE

ro

vo

RC

B

Using node voltage method and noting ∆iB = −vi /rπ :

vo

vo − v i

+ β∆iB +

=0

RC

ro

1

β

1

1

+ vi − −

+

RC ro

rπ ro

vo

vo

1

β

≈ vi

RC k r o

rπ

Av ≡

!

=0

vo

β

β

RC

= (RC k ro ) ≈ RC =

vi

rπ

rπ

re

which is exactly the gain of the common emitter amplifier (with no emitter resistor) except

for the positive sign. This should not be surprising as compared to a common emitter, we

have switched the terminals of the input signal (leading to the change in the sign of Av ) and

the output voltage is vCB = vCE − vBE ≈ vCE because of the high gain of the amplifier.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

184

The input resistance of the circuit can be found by finding ii from the circuit above and

computing vi /ii to be

Ri =

rπ (ro + RC )

rπ

rπ

rπ (ro + RC )

≈

≈

≈

= re

rπ + RC + ro (1 + β)

ro (1 + β)

1+β

β

In the approximation, we first used the fact that rπ + RC ro (1 + β) and then RC ro .

Note that the input resistance is quite small.

As before, the load can be configured in two ways: 1) RC is the load; or 2) load is placed

in parallel to RC . The output resistance can be found by killing the source (short vi ) and

finding the Thevenin resistance of the two-terminal network. For this circuit, we see that

if vi = 0 (killing the source), ∆iB = 0. In this case, the strength of the dependent current

source would be zero and this element would become an open circuit. In addition, emitter

would be effectively grounded and resistors RE and rπ are effectively shorted out of the

circuit. Therefore,

Ro = r o

Ro0 = RC k ro ≈ RC

which are similar to the common amplifier with no emitter resistor.

As a whole, this circuit is similar to common emitter amplifier with no resistor (large voltage

gain, medium output resistance) but has a very low input resistance (re ). As such, it is

rarely used as a voltage amplifier (except for very specialized cases).

Following the formula in page 13, the short circuit current-gain of this amplifier is:

Ai =

ZI

re RC

Av =

=1

ZL + Z o

0 + R c re

Therefore, this circuit has a low input resistance, a medium output resistance and currentgain of unity and, therefore, is a “current buffer”: It accepts an input signal current with

a low input resistance and deliver nearly equal current to a much higher output resistance.

Common-base amplifiers are mostly used as a current buffer, typically forming circuits including two BJTs (cascode amplifier) which are utilized specially in integrated circuits.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

185

6.7

FET Amplifier Circuits

As expected, FET amplifiers are very similar to the BJT amplifiers. There are four basic

FET amplifiers: 1) common-drain or source follower (similar to common collector or emitter

follower), 2) common-source (similar to common emitter), 3) common source with a source

resistor (similar to common emitter with an emitter resistor) and common gate (similar to

common base).

The analysis technique are exactly the same: 1) DC-biasing analysis, and 2) AC analysis in

which we replace FET with its small signal model. In fact, by comparing the small signal

model for an FET that that of a BJT, we should be able to find the answer immediately by

replacing β/rπ = gm in the formulas of the equivalent BJT circuits and then let rπ → ∞ (and

of course, replace RC → RD , RE → RS , and RB = R1 k R2 → RG = R1 k R2 ). Therefore,

we will only solve the common-source amplifier in detail and summarize the results for the

other configurations.

6.7.1

Common Source Amplifier

DC analysis: Recall that a source resistor

is necessary to provide stability for the bias

point. As such, the circuit configuration as

is shown has a poor bias. We need to include RS for good biasing (DC signals) and

eliminate it for AC signals. The solution

is to include a source resistance and use a

“bypass” capacitor to short it out for AC

signals similar to the BJT common-emitter

amplifier.

VDD

R1

vi

VDD

R1

RD

vo

Cc

vi

RD

vo

Cc

R2

R2

Cb

RS

Good Bias using a

by−pass capacitor

Poor Bias

AC analysis: To start the analysis, we kill all DC sources, short out Cb (which shorts out

RS ), combine R1 and R2 into RG , and replace the FET with its small signal model. We see

that the source is now common between the input and output AC signals (thus, the common

source amplifier). Examination of the circuit shows that:

vi = ∆vGS

vo = −(RD k ro ) gm ∆vGS

vo

Av ≡

= −gm (RD k ro ) ≈ −gm RD

vi

Ri = R G

Ro = r o

Ro0 = RD k ro

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

vi

Cc

RG

G

∆i = 0

+

∆v

GS

_

vo

D

G

gm ∆ vGS

ro

RD

S

Ro

R’o

186

which are exactly the same as formulas for a BJT common emitter amplifier if we let β/rπ =

gm and rπ → ∞. Note that as an FET can be biased with large (MΩ) R1 and R2 (see

page 167), the input resistance of this amplifier is considerably larger than that of a common

emitter amplifier and can even be made to be infinitely large (resistance of the Gate insulator)

by removing RG and biasing the circuit with two voltage supplies or a current mirror.

Lower cut-off frequency: As Ri is very large, the lower cut-off frequency is set by the

bypass capacitor (unless Cc is chosen to be very small) .

ωl = ωl (bypass) = 2π fl =

where RS0 ≡ RS k

1

RS0 Cb

1

gm

Note that usually RS 1/gm and, therefore, RS0 ≈ 1/gm .

6.7.2

Common Source Amplifier with Source resistance

Similar to common-emitter amplifier, the common source amplifier gain depends on the FET parameters (gm ). Addition of

a source resistance will remove this dependency (similar to the

common emitter amplifier with an emitter resistor). Details of

the AC analysis is left as an exercise. The parameters of this

amplifier are:

RD

gm RD

≈−

Av = −

1 + g m RS

RS

Ri = R G

Ro = 1/gm k ro

1

ωl = 2π fl =

Ri Cc

VDD

R1

vi

RD

vo

Cc

R2

RS

Ro0 = RD k Ro ≈ RD

Similar to the common-emitter amplifier, the gain is set by RD and RS and is independent of

the FET parameters. The input resistance of the circuit is large (much larger than common

emitter amplifier because R1 and R2 can be large).

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

187

6.7.3

Common Drain Amplifier

VDD

This circuit is similar to the common-collector amplifier (or the

emitter follower). Details of the AC analysis is left as an exercise.

The parameters of this amplifier are:

Av =

gm ro RS

≈1

ro + (1 + gm ro )RS

R1

Cc

vi

vo

Ri = R G

Ro = 1/gm k ro

1

ωl = 2π fl =

Ri Cc

R2

Ro0 = RS k Ro ≈ RS

RS

Similar to the emitter follower, the source follower is a voltage buffer. It is superior to the

emitter follower because of its very large input resistance.

6.7.4

Common Gate Amplifier

VDD

This circuit is similar to the BJT common-base amplifier. Details of the AC analysis is left as an exercise. The parameters of

this amplifier are:

RD

vo

Av = −gm (RD k ro ) ≈ −gm RD

Ri =

RS (ro + RD )

RS (ro + RD )

ro

1

≈

≈

=

ro + RD + (1 + gm ro )RS

(1 + gm ro )RS

gm ro

gm

Ro0 = RD k ro ≈ RD

1

ωl = 2π fl =

Ri Cc

Ro = r o

vi

Cc

RS

−VSS

Note that in the approximation for Ri , we first used the fact that ro + RD (1 + gm ro )RS

and then RD ro .

Similar to the common-base amplifier, this is a poor voltage amplifier because of its low input

resistance but has a short-circuit current gain of unity, low input impedance, and medium

output impedance and can be used as a current buffer.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

188

Summary of Transistor Amplifiers?

VCC

Common Collector (Emitter Follower):

R1

(RE k ro )(1 + β)

≈1

Av =

rπ + (RE k ro )(1 + β)

Cc

vi

vo

Ri = RB k [rπ + (RE k ro )(1 + β)] ≈ RB

(ro ) rπ

rπ

Ro =

≈

= re

(1 + β)(ro ) + rπ

β

Ro0 =

rπ

(ro0 ) rπ

≈

(1 + β)(ro0 ) + rπ

β

R2

1

2π fl =

Ri Cc

where ro = ro k RC

RE

VCC

Common Emitter:

RC

R1

β

RC

β

(RC k ro ) ≈ − RC = −

rπ

rπ

re

Ri = R B k r π

Av = −

vo

Cc

vi

R2

Cb

RE

Ro0 = RC k ro ≈ RC

1

1

0

+ 0

where RE

≡ RE k re

2π fl =

Ri Cc RE Cb

Ro = r o

VCC

Common Emitter with Emitter Resistance:

Av = −

R1

RC

RC

RC

≈−

≈−

re (1 + RC /ro ) + RE

re + R E

RE

"

RE

+ re

Ri = R B k β

1 + RC /ro

!#

≈ RB k βRE ≈ RB

RE

RE /re

Ro ≈ r o + r o ×

≈ ro

+1

1 + RE /rπ

re

Ro0 = RC k Ro ≈ RC

and 2π fl =

RC

Cc

vo

vi

R2

RE

1

Ri Cc

VCC

RC

Common Base Amplifer:

β

RC

(RC k ro ) ≈

rπ

re

rπ (ro + RC )

≈ re

Ri =

rπ + RC + ro (1 + β)

vo

Av =

Ro = r o

Ro0 = RC k ro ≈ RC

vi

Cc

1

and 2π fl =

Ri Cc

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

RE

−VEE

189

VDD

Common Drain (Source Follower):

Av =

R1

gm ro RS

≈1

ro + (1 + gm ro )RS

Cc

vi

vo

Ri = R G

R2

Ro = 1/gm k ro

1

ωl = 2π fl =

Ri Cc

Ro0

RS

= RS k Ro ≈ RS

VDD

Common Source:

R1

Av = −gm (RD k ro ) ≈ −gm RD

RD

vo

Cc

vi

Ri = R G

Ro = r o

Ro0 = RD k ro

ωl = ωl (bypass) = 2π fl =

R2

1

RS0 Cb

where RS0 ≡ RS k

Cb

RS

1

gm

VDD

Common Source with Source Resistance:

RD

gm RD

≈−

Av = −

1 + g m RS

RS

Ri = R G

Ro = 1/gm k ro

1

ωl = 2π fl =

Ri Cc

R1

vi

R2

Ro0 = RD k Ro ≈ RD

Ro0 = RD k ro ≈ RD

1

ωl = 2π fl =

Ri Cc

Ro = r o

RS

VDD

RD

Av = −gm (RD k ro ) ≈ −gm RD

1

RS (ro + RD )

≈

ro + RD + (1 + gm ro )RS

gm

vo

Cc

Common Gate Amplifer:

Ri =

RD

vo

vi

Cc

RS

−VSS

?

If bias resistors are not present (e.g., bias with current mirror), let RB or RG → ∞ in the

“full” expression for Ri .

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

190

6.8

Exercise Problems

In circuit design, use 5% commercial resistor and capacitor values (1, 1.1, 1.2, 1.3, 1.5, 1.6,

1.8, 2, 2.2, 2.4, 2.7, 3., 3.3, 3.6, 3.9, 4.3, 4.7, 5.1, 5.6, 6.2, 6.8, 7.5, 8.2, 9.1 × 10 n where n is

an integer). Use Si BJTs, with β = 200, βmin = 100, rπ = 5 kΩ, ro = 100 kΩ.

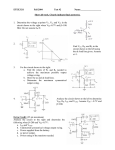

Problem 1. Show that this circuit is a stable biasing scheme.

Problem 2 to 5. Compute Io assuming identical transistors.

Problem 6 to 8: Find the bias point and AC amplifier parameters of these circuits (Manufacturers’ spec sheets give: β = 200, rπ = 5 kΩ, ro = 100 kΩ).

V CC

I ref

Io

I ref

VCC

Io

Q3

Io

I ref

Q3

RC

RB

IC

Q1

Q2

Q1

Q2

Q2

−VSS

−VEE

Problem 1

Q1

Problem 2

−VEE

Problem 3

Problem 4

15 V

9V

34 k

Io

I ref

Q3

Q2

30k

4.7 µ F

vi

vo

0.47 µ F

Q1

vo

vi

18k

16 V

1k

22k

1k

vi

270

510nF

1.5k

vo

5.9 k

240

47 µ F

6.2k

510

−VSS

Problem 5

Problem 6

Problem 7

Problem 8

Problem 9: Design a BJT amplifier with a gain of 4 and a lower cut-off frequency of 100 Hz.

The Q point parameters should be IC = 3 mA and VCE = 7.5 V.

Problem 10: Design a BJT amplifier with a gain of 10 and a lower cut-off frequency of

100 Hz. The Q point parameters should be IC = 3 mA and VCE = 7.5 V. A power supply of

15 V is available.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

191

Problem 11. Design a BJT amplifier with a gain of 5 and a lower cut-off frequency of 10 Hz,

powered by a 16 V supply. Set the Q-point parameters to be VCE = 10 V and Ic = 5 mA.

Problem 12. Consider the BJT circuit below with R1 = 47 kΩ, R2 = 39 kΩ, RE =

1.5 kΩ, RL = 50 kΩ, C1 = 100 nF, C2 = 0.47 µF, and VCC = 15 V. An input signal with

vi = cos(5000t) is applied to the circuit. Calculate expressions for voltages vB , vE , and vo

(include both AC and DC parts in the expression for each voltage). Manufacturers’ spec

sheets give: β = 200, rπ = 5 kΩ, ro = 100 kΩ.

Problems 13 to 16: Find the bias point and AC amplifier parameters of these circuits

(Manufacturers’ spec sheets give: β = 200, rπ = 5 kΩ, ro = 100 kΩ).

Problems 17. Find the bias point and AC amplifier parameters of these circuits (Manufacturers’ spec sheets give K = 0.25 mA/V2 and Vt = 1 V, gm = 0.25 mA/V, and ro = 100 kΩ).

Problems 18. Find the bias point and AC amplifier parameters of these circuits (Manufacturers’ spec sheets give K = 0.20 mA/V2 and Vt = 3 V, gm = 0.2 mA/V, and ro = 100 kΩ).

Problem 19. Find the bias point and AC amplifier parameters of these circuits (Manufacturers’ spec sheets give K = 0.20 mA/V2 and Vt = 4 V, gm = 0.2 mA/V, and ro = 100 kΩ).

15 V

VCC

R

v

C

i

vB

vE

C2

RE

−9 V

2k

vo

vi

1

1

R2

39 k

18k

vo

Problem 12

510

4V

vi

110k

vo

1k

vo

vi

Cc

51k

18k

Problem 15

20 V

2k

1M

1k

vi

18 V

500k

vo

vi

Cc

1k

vo

1k

Problem 14

12 V

vo

Cc

1M

1k

0.47 µ F

22k

510

Problem 13

vi

vo

0.47 µ F

47 µ F

6.2 k

22k

vi

0.33 µ F

RL

9V

1k

Cb

1.3M

10k

−5 V

Problem 16

Problem 17

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

Problem 18

Problem 19

192

Problems 20 to 22: Find the bias point and AC amplifier parameters of these circuits

(Manufacturers’ spec sheets give: β = 200, rπ = 5 kΩ, ro = 100 kΩ).

15 V

33k

vi

2k

18k

Q1

0.47 µF

33k

Q2

vo

4.7 µF

6.2k

500

22k

18 V

15 V

1k

15k

2k

Q2

vi

4.7 µF

6.2k

Problem 20

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

vo

Q1

500

vi

1k

Problem 21

3.6k

1.5k

Q1

4.7 µF

2.7k

510

vo

Q2

510

Problem 22

193

6.9

Solution to Selected Exercise Problems

Problem 1. Show that this is a stable biasing scheme.

This is another stable biasing scheme which eliminates RB thereby, greatly reducing the

input resistance and increasing the value of the coupling capacitor (or lowering the cut-off

frequency). This scheme uses Rc as the feedback resistor.

We assume that the BJT is in the active-linear state. Since IB IC ,

by KCL I1 = IC + IC ≈ IC . Then:

BE-KVL:

VCC = RC IC + RB IB + VBE = (RC + RB /β) IC + VBE

IC =

VCC − VBE

RC + RB /β

VCC

RC

RB

I1

IC

If, RB /β RC or RB βRC , we will have (setting VBE = Vγ ):

IC =

VCC − Vγ

RC

Since IC is independent of β, the bias point is stable. We still need to prove that the BJT

is in the active-linear state. We write a KVL through BE and CE terminals:

VCE = RB IB + VBE = RB IB + Vγ > Vγ

Since VCE > Vγ , BJT is indeed in the active state.

To see the negative feedback effect, rewrite BE-KVL as:

IB =

VCC − Vγ − RC IC

RB

Suppose that the circuit is operating and BJT β is increased (e.g., an increase in the temperature). In this case IC will increase which raises the voltage across resistor RC (RC IC ).

From the above equation, this will lead to a reduction in IB which, in turn, will decrease

IC = βIB and compensate for any increase in β. If BJT β is decreased (e.g., a decrease

in the temperature), IC will decrease which reduces the voltage across resistor RC (RC IC ).

From the above equation, this will lead to an increase in IB which, in turn, will increase

IC = βIB and compensate for any decrease in β.

Note: The drawback of this bias scheme is that the allowable AC signal on VCE is small.

Since VCE ± ∆VCE > Vγ in order for the BJT to remain in active state, we find the amplitude

of AC signal, ∆VCE < RB IB = (RB /β)IC . Since, RB /β RC for bias stability thus,

∆VCE RC IC . This is in contrast with the standard biasing with emitter resistor in which

∆VCE is comparable to RC IC . Also, there is a feedback for the AC signals.

ECE65 Lecture Notes (F. Najmabadi), Winter 2006

194

Problem 2. Compute Io assuming identical transistors.

Because both bases and emitters of the transistors Q1 and Q2

are connected together, KVL leads to vBE1 = vBE2 . As BJT’s

are identical, they should have similar iB (iB1 = iB2 = iB )

and, therefore, similar iE = iE1 = iE2 and iC = iC1 = iC2 .

Using iC = βiB and iE = (β + 1)iB to illustrate the impact

of β:

iE

iB =

β+1

KCL:

iE3

iB3

KCL:

βiE

Io = i C =

β+1

I ref

Io

Q3

i B3

iC

Q1

iB

2i B

iB

iC

Q2

−VEE

2iE

= 2iB =

β+1

iE3

2iE

=

=

β+1

(β + 1)2

Iref = iC + iB3 =

V CC

2iE

βiE

+

β + 1 (β + 1)2

1

1

β

Io

=

≈

=

Iref

β + 2/(β + 1)

1 + 2/β(β + 1)

1 + 2/β 2