* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download CMOS Analog Design Lecture Notes Rev 1.5L_02_06_11

Oscilloscope types wikipedia , lookup

Coupon-eligible converter box wikipedia , lookup

Schmitt trigger wikipedia , lookup

Power electronics wikipedia , lookup

Electronic engineering wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Analog television wikipedia , lookup

Radio transmitter design wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Broadcast television systems wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Integrated circuit wikipedia , lookup

Power MOSFET wikipedia , lookup

Operational amplifier wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Telecommunication wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Current mirror wikipedia , lookup

Rectiverter wikipedia , lookup

CMOS Analog Design

LECTURE NOTES

Prof. Dr. Bernhard Hoppe

Introduction

Prof. Dr. Hoppe

CMOS Analog Design

2

Analog Integrated Circuits Design Steps:

1.

2.

3.

4.

5.

6.

7.

Definition

Implementation

Simulation

Geometrical description

Simulation including the geometrical parasitics

Fabrication

Testing and verification

Prof. Dr. Hoppe

CMOS Analog Design

3

Analog Integrated Circuits Design:

Tools & Methods:

•

•

•

Simulation

Design Capture

Hand Calculations

Prof. Dr. Hoppe

Bottom – Up

Flow

CMOS Analog Design

4

Discrete Analog Circuit Design

- Using breadboards

Integrated Analog Circuit Design

- Using computer simulation techniques

Prof. Dr. Hoppe

CMOS Analog Design

5

Pros and Cons of Computer simulations

Advantages:

1.

2.

3.

4.

5.

No breadboards required

Every node in the circuit is accessible

Feedback loops may be opened

Modification of the circuit is easy

Modification of processes and ambient conditions is

possible

Prof. Dr. Hoppe

CMOS Analog Design

6

Pros and Cons of Computer simulations

Drawbacks:

1. Accuracy of models

2. Convergence problems of the simulator: circuit may

not converge to a stable operating point

3. Time required to perform simulations of large circuits

4. Use of the computer as a substitute for thinking

Prof. Dr. Hoppe

CMOS Analog Design

7

The PN junction

Prof. Dr. Hoppe

CMOS Analog Design

8

PN junction

Used for:

1. Insulation purposes

2. Diodes and zeners

3. Basic structure of MOS and Bipolar transistor

Prof. Dr. Hoppe

CMOS Analog Design

9

Important features for device properties

And modelling aspects

•

•

•

•

Depletion region width

Depletion region capacitance

Reverse bias breakdown voltage

Diode equation iD Vs VD

Prof. Dr. Hoppe

CMOS Analog Design

10

Diode Model:

Step function

change of impurity

concentration =>

Idealization

Prof. Dr. Hoppe

CMOS Analog Design

11

Diode Model:

Space charge

width

Xd = Xn - Xp

Equilibrium

condition:

Field forces =

Diffusion forces

Prof. Dr. Hoppe

CMOS Analog Design

12

Xd = ?, E0 = ?, Φ0 = ?

Due to electrical neutrality, the charge on either side of

the junction must be equal

Thus,

qNDXn = qNAXp

where q = 1.6 x 10-19 C

To calculate the fieldstrength from the charge,

Gauss equation:

dE(x) = qN

dx

εSi

where εSi = 11.7x8.85x10-14 F/cm – Si dielectric constant

Prof. Dr. Hoppe

CMOS Analog Design

13

On integration we get the max electric field at the

junction, E0

E0 = 0

∫

Therefore,

Prof. Dr. Hoppe

E0

dE = Xp

∫

0

E0 =

–qNA / εSi dx

-qNDXn

εSi

CMOS Analog Design

=

qNAXp

εSi

14

Voltage is found by integrating the electric field, resulting

in

Φ0 - VD

-E0(Xn – Xp)

=

2

where VD = applied external voltage

Φ0 = barrier potential

Prof. Dr. Hoppe

CMOS Analog Design

15

Barrier potential Φ0 is given as

Φ0 = (kT / q) ln (NAND / ni2) = (Vt) ln (NAND / ni2)

where k = Boltzmann‘s constant 1.38 x 10-23 J/K

ni = intrinsic concentration of silicon

1.45 x 1010 /cm3 at 300K

Vt = 25.9 mV at 300K

Prof. Dr. Hoppe

CMOS Analog Design

16

Using equations for E0 and Φ0 – VD, and solving for Xn

or Xp we get

Xn =

and

Prof. Dr. Hoppe

(

Xp = -

2εSi(Φ0 – VD)NA

qND(NA + ND)

(

)

2εSi(Φ0 – VD)ND

qNA(NA + ND)

CMOS Analog Design

1/2

)

1/2

17

Width of the depletion region Xd is given as

Xd = Xn – Xp =

Prof. Dr. Hoppe

(

2εSi(NA + ND)

qNAND

CMOS Analog Design

)

1/2

(Φ0 - VD)1/2

18

Conclusions:

1.

2.

3.

4.

Xd is proportional to (Φ0 - VD)1/2 or (- VD)1/2

If NA >> ND then Xd ~ Xn

If ND >> NA then Xd ~ Xp

Lower doped side determines Xd

Prof. Dr. Hoppe

CMOS Analog Design

19

Depletion charge and depletion layer

capacitance:

Depletion charge Qj is given as

Qj = |AqNAXp| = AqNDXn

(

Qj = A

2εSiqNAND

(NA+ND)

)

1/2

(Φ0 - VD)1/2

where A is the cross sectional area of the pn junction

Prof. Dr. Hoppe

CMOS Analog Design

20

Depletion charge and depletion layer

capacitance:

Magnitude of the electric field at the junction

E0

=

2qNAND

( ε (N +N ) )

Si

Prof. Dr. Hoppe

A

1/2

(Φ0 - VD)1/2

D

CMOS Analog Design

21

Depletion charge and depletion layer

capacitance:

Depletion layer capacitance Cj is given as

dQj

Cj = dV = A

D

(

=

Prof. Dr. Hoppe

εSiqNAND 1/2

-1/2

(Φ

V

)

0

D

2(NA+ND)

)

Cj0

[1-(VD /Φ0)]m

CMOS Analog Design

22

Depletion charge and depletion layer

capacitance:

where Cj0 is capacitance when VD = 0

m is a grading coefficient

m = 1/2 => step junction

m = 1/3 => linearly graded junction

1/3 <= m <= 1/2 => real junctions

(experimental fit)

Prof. Dr. Hoppe

CMOS Analog Design

23

Plot of the space charge capacitance:

Ideal

Actual

Prof. Dr. Hoppe

CMOS Analog Design

24

Example:

Calculate Xd, Xn ,Xp, E0, Cj0, and Cj

for VD = -4 V,

NA = 5 x 1015 /cm3,

ND = 1020 /cm3,

A = 10 μm x 10 μm

Temperature = 300 K

Results: 0=0.917V

Cj(-4V) = 9.18fF

Prof. Dr. Hoppe

xn 0 xp= 1.128µm Cj0 = 20.3fF

CMOS Analog Design

25

Breakdown voltage of a reverse biased diode:

BV =

(

εSi(NA + ND)

2qNAND

)(E

2

)

max

assuming |VD > Φ0|

Emax is the maximum electric field that can exist

across the depletion region

For silicon, Emax ~ 3 x 105 V/cm

Prof. Dr. Hoppe

CMOS Analog Design

26

Breakdown mechanisms:

1. Avalanche breakdown: Multiplication of carrier

concentrations due to collisions of minority carriers

with the electrons of the atoms in the lattice. It has a

negative temperature coefficient.

2. Zener breakdown: Valence band breakdown. It

occurs at comparatively lower voltages. It does not

depend upon temperature (tunneling effect).

Prof. Dr. Hoppe

CMOS Analog Design

27

Breakdown mechanisms:

Reverse biased current (due to avalanche effect)

iRA = MiR =

([1- (V

1

n]

/BV)

R

) xi

R

where M = avalanche multiplication factor

n = empirical parameter 3 <= n <= 6

iR = ‘normal‘ reverse current

Prof. Dr. Hoppe

CMOS Analog Design

28

Typical pn junction characteristics:

Prof. Dr. Hoppe

CMOS Analog Design

29

Voltage-Current relationship of diode:

Impurity concentration profile for diffused pn junction

under forward bias: Minorities pile up at the boundaries of

the depletion region!

Prof. Dr. Hoppe

CMOS Analog Design

30

Voltage-Current relationship of diode:

Minority carrier concentration for diffused pn

junction:

no applied voltage: no excess minority carrier

concentration: np(0) = np0 and pn(0) =pn0

Reverse biased (vD negative): minority carrier

concentration is depleted below the equilibrium

value!

Current in reverse biased pn-junction is a diffusion

current, depending on the slope of the minority

carrier concentration at the boundaries of the

depletion region.

Prof. Dr. Hoppe

CMOS Analog Design

31

Voltage-Current relationship of diode:

Terminologies:

pn0 and np0 = equilibrium concentrations of the minority

carriers in n-type and p-type regions

pn(0) = pn0 exp(VD/Vt) is value of the excess

concentration at x = 0

np(0) = np0 exp(VD/Vt) is value of the excess

concentration at x‘ = 0

Prof. Dr. Hoppe

CMOS Analog Design

32

Voltage-Current relationship of diode:

The total current in an pn junction diode is given as

iD = qA

(

Dppn0

Dnnp0

(exp(VD/Vt) – 1)

Lp + Ln

)

Or

iD = Is (exp(VD/Vt) – 1)

Prof. Dr. Hoppe

CMOS Analog Design

33

Voltage-Current relationship of diode:

where

Is = qA

(

Dppn0

Dnnp0

Lp + Ln

)

is a constant called the saturation current

A = area of the pn junction

Dp = diffusion constant of holes in n-type semiconductor

Dn = diffusion constant of electrons in p-type

semiconductor

Lp = diffusion length for holes in n-type semiconductor

Ln = diffusion length for el. in p-type semiconductor

Prof. Dr. Hoppe

CMOS Analog Design

34

Example:

Calculate the saturation current of a pn junction diode

with

NA = 5 x 1015 /cm3, ND = 1020 /cm3,

A = 1000 μm2 , Dn = 20 cm2 / s,

Dp = 10 cm2 / s, Ln = 10 μm,

Lp = 5 μm.

Prof. Dr. Hoppe

CMOS Analog Design

35

The MOS transistor

Prof. Dr. Hoppe

CMOS Analog Design

36

N-well technology:

Physical structure of an n-MOS and p-MOS device:

Prof. Dr. Hoppe

CMOS Analog Design

37

N-well technology:

•

•

•

•

•

•

pMOS formed within a lightly doped n- material

called the N-well

nMOS formed within a lightly doped p- substrate

Both types of transistors are four terminal devices

The p-bulk connection is common throughout the

integrated circuit and is connected to Vss (the most

negative supply)

Multiple n-wells can be connected to different

potentials (but +ve w.r.t. Vss)

nMOS and pMOS devices are complementary:

nMOS equations can be mapped to pMOS

equations

Prof. Dr. Hoppe

CMOS Analog Design

38

nMOS threshold voltage equation:

Cross section of an n-channel transistor with all

terminals grounded:

Prof. Dr. Hoppe

CMOS Analog Design

39

nMOS threshold voltage equation:

Terminologies:

Cox = Area specific oxide capacitance in F/m2

ΦF = Equilibrium electrostatic potential (Fermi potential) in

the semiconductor

ΦS = Surface potential of the semiconductor

ΦMS = Difference in the work functions between the gate

material and bulk silicon in the channel region

QSS = Undesired +ve charge present in the interface

between the oxide and the bulk silicon

Qb0 = Fixed charge in the depletion region

VSB = Substrate bias (VSource - VSubstrate)

Prof. Dr. Hoppe

CMOS Analog Design

40

nMOS threshold voltage equation:

Threshold voltage VT consists of following contributions:

1. ΦMS = ΦF (substrate) - ΦF (gate)

where ΦF (metal) = 0.6 V

2. [-2ΦF – (Qb /Cox)]: voltage required to change the

surface potential and offset the depletion layer charge

3. Undesired +ve charge QSS due to impurities and

imperfections at the interface – must be compensated

by a gate voltage of – QSS /Cox

Prof. Dr. Hoppe

CMOS Analog Design

41

nMOS threshold voltage equation:

Summation of the contributions:

VT = ΦMS + [-2ΦF – (Qb /Cox )] + (– QSS /Cox )

= ΦMS - 2ΦF – (Qb0 /Cox ) – (QSS /Cox ) - (Qb - Qb0 ) / Cox

The threshold voltage can be rewritten as

VT VT 0

2F VSB 2F

where VT0 = ΦMS - 2ΦF – (Qb0 /Cox ) – (QSS /Cox )

Prof. Dr. Hoppe

CMOS Analog Design

42

Body effect coefficient:

The body factor, body effect coefficient, or bulk-threshold

parameter γ is defined as

γ=

Prof. Dr. Hoppe

√2qεSiNA

Cox

CMOS Analog Design

(unit: V1/2)

43

Sign conventions in threshold voltage equation:

n-channel device p-channel device

p type substrate n type substrate

Parameter

ΦMS

_

_

metal

_

_

n+ Si

+

+

p+ Si

_

+

ΦF

_

+

Qb0, Qb

+

+

QSS

+

_

VSB

+

_

γ

Prof. Dr. Hoppe

CMOS Analog Design

44

Example:

Calculate the threshold voltage and body factor γ for an

n-channel transistor with an n+-silicon gate for no

substrate bias and a Vsb od 2V if

tox = 200 Angström ,

NA = 3 x 1016 /cm3,

gate doping ND = 4 x 1019 /cm3,

surface charge density NSS = 1010 /cm2,

temperature = 300 K.

Prof. Dr. Hoppe

CMOS Analog Design

45

Solution (1):

tox = 200 Angström,

NA = 3 x 1016 /cm3,

ND = 4 x 1019 /cm3,

NSS = 1010 /cm2,

Temperature of 300 K means

• kBT/q = 0.026V (Temperature Voltage)

• ni = 1.45 x 1010 /cm3 (Intrinsic Carrier Concentration)

Si 11,7 0

Prof. Dr. Hoppe

CMOS Analog Design

46

Solution (2):

Formula for the threshold-voltage:

VT VT 0

with the Fermi-potential:

ni

k BT

ln

q

NA

F

sub

The zero substrate bias threshold voltage is:

VT 0 MS

Qb0 QSS

2F

Cox Cox

2F VSB 2F

F gate

k BT N D

ln

q

ni

Pdoped

Ndoped

The space charge in the channel

Qb0 2q N A Si 2F

The work-function difference

MS F sub F gate

Prof. Dr. Hoppe

CMOS Analog Design

47

Solution (3):

The work-function difference and

MS F sub F gate 0.026V ln

1.45e 10

4.0e 19

0.026V ln

3e 16

1.45e 10

0.38V 0.57V 0.95V

the space charge induced potential in the channel

Qb 0 2q N A Si 2F

ox

Cox

tox

2 (1.6e 19) (3.0e 16) 11.7 (8.854e 14) 0.76 As / cm 2

3.9 (8.854e 14) /(200.0e 10)

As / Vcm 2

(8.7e 8) As / cm 2

0.51V

2

(170.0e 9) As / Vcm

Prof. Dr. Hoppe

CMOS Analog Design

48

Solution (4):

The body-factor reads

2q N A Si 2F

Cox

Qb 0

2F Cox

0.51

V 0.58 V

0.87

So the threshold voltage without substrate bias is

VT 0 0.95V 0.76V 0.51V 0.01V 0.33V

and for Vsb = 2V we get:

VT 0.33V 0.58( 0.76 2.0 0.76)V 0.78V

Prof. Dr. Hoppe

CMOS Analog Design

49

Current voltage relation of the MOS transistor:

1. Linear mode: - Sah equation

iD = (W/L)μnCox [(VGS – VT) – (VDS/2)] VDS

holds good for (VGS – VT) >= VDS and VGS >= VT

2. Saturation mode:

iD = (W/2L)μnCox [(VGS – VT)2]

holds good for (VGS – VT) <= VDS

Prof. Dr. Hoppe

CMOS Analog Design

50

Device transconductance parameter:

The factor μnCox is defined as the device

transconductance parameter, given as

K‘ = μnCox = μnεox / tox

Prof. Dr. Hoppe

CMOS Analog Design

51

CMOS device modeling

Prof. Dr. Hoppe

CMOS Analog Design

52

Pinch-off Saturation:

•

•

•

•

Voltage drop in the channel is constant

The Field pulling the electrons from the source

remains constant

iD remains constant

Electrons are injected from the channel into the

space charge region => ballistic transport to drain

node

Prof. Dr. Hoppe

CMOS Analog Design

53

How large is the saturation current ?:

Saturation condition:

VDS = (VGS – VT)

Saturation current equation:

iD = (W/2L)μnCox [(VGS – VT)2]

holds good for 0 <= (VGS – VT) <= VDS

Prof. Dr. Hoppe

CMOS Analog Design

54

Output characteristics of the MOSFET for

VT = 1V:

Prof. Dr. Hoppe

CMOS Analog Design

55

Channel length modulation effect:

•

•

•

•

Constant saturation current – only for long channel

devices i.e. Pinch-off point „close“ to the drain

Long channel devices have length L >= 10 μm

For lengths shorter than 1 μm, short channel effects

are observed

Most important effect: Channel length modulation

effect

Prof. Dr. Hoppe

CMOS Analog Design

56

Channel length modulation effect:

•

•

In reality, the saturation current depends linearly on

VDS

Modified current equation:

iD = (W/2L) μnCox [(VGS – VT)2 (1 + λVDS)]

where λ = channel length modulation factor (unit: 1/V)

Prof. Dr. Hoppe

CMOS Analog Design

57

Kleinsignalparameter

•

•

Kleinsignalparameter beschreiben das Verhalten eines

Systems in der Nähe eines Arbeitspunktes

In Sättigung gilt für die Abhängigkeit des Drainstroms

von der Gate Source Spannung (Vds und Vsb fest)

I D

Vds fest

Eingangsleitwert g m

V gs

W

2 n Cox I D

L

W

gm nCox V GS V TH

L

g m f VGS VTH

2 ID

VGS VTH

A g m R D

spannungsabhängig

Nichtlinearität!

Prof. Dr. Hoppe

CMOS Analog Design

58

Kleinsignalparameter

•

In Sättigung gilt für die Abhängigkeit des Drainstroms

von der der Drain-Source-Spannung bei fester Gate

Source Spannung

Ausgangsleitwert

g ds

I D

Vgs fest

V ds

1

W

gds nCox V GS V TH ² I D

2

L

1/gds = ro der Ausgangswiderstand des Transistors

Prof. Dr. Hoppe

CMOS Analog Design

59

Kleinsignalparameter

•

In Sättigung gilt für die Abhängigkeit des Drainstroms

von der

der Source-Bulk-Spannung bei fester Drain-Source- und

Gate Source Spannung

Substratabhängigkeit

gmbs

g mbs

I D

Vgs & Vds fest

V SB

I D VT

I D

I D

g

gm

m

VBS VSB

2 2 F VSB

VT VSB

Ändert sich VSB, dann ändert sich die Einsatzspannung und damit der Strom im Transistor!

Prof. Dr. Hoppe

CMOS Analog Design

60

Kleinsignalparameter Leitwerte gm und gds

•

In Sättigung gilt für die Abhängigkeit des Drainstroms

von der der Drain-Source-Spannung bei fester Gate

Source Spannung

I D

Vgs fest

g ds

V ds

1

W

gds nCox V GS V TH ² I D

2

L

1/gds = ro der Ausgangswiderstand des Transistors

Prof. Dr. Hoppe

CMOS Analog Design

61

Transfer characteristics of the MOSFET:

iD plotted against VGS for fixed VDS, VT = 2V

Prof. Dr. Hoppe

CMOS Analog Design

62

Short channel effects:

•

•

•

As technology scaling reaches channel lengths

shorter than 1 μm, second order effects become

significant

MOSFETs with L < 1 μm are called short channel

devices

Main effects:

1. velocity saturation

2. threshold voltage variation

3. hot carrier effect

Prof. Dr. Hoppe

CMOS Analog Design

63

Review of classical derivation of iD:

Gradual Channel Approximation:

x-direction perpendicular to the surface,

y-direction from 0 to L: the channel

VT is assumed to be constant along the channel

Electrical field in y-direction much larger than the field in x-direction

Current flow in the channel in y-direction only

The whole channel is assumed to be inverted: VGS > VT VGD = VGS - VDS > VT

Prof. Dr. Hoppe

CMOS Analog Design

64

Review of classical derivation of iD:

The mobile charge in the channel flows along the y-direction driven by Ey

The mobile charge at position y depends on VGS and the channel voltage Vc(y) is

Q(y) = -Cox [VGS - Vc(y) - VT]

...(1)

Note:

The channel is tapered as we move from source to drain as the gate to channel voltage

causing surface inversion is smaller at the drain end!

Prof. Dr. Hoppe

CMOS Analog Design

65

Review of classical derivation of iD:

The incremental resistance of the segment dy reads:

dR

dy

W n Q( y )

……2

Current iD is flowing from source and drain in y-direction (1-dimensional model)

Voltage drop along dy:

iD dy

…….3

dV i dR

D

Prof. Dr. Hoppe

W n Q( y )

CMOS Analog Design

66

Review of classical derivation of iD:

Integration along y from 0 to L yields :

L

i

D

dy W n

0

VDS

Q( y )dV

C

0

We insert equ.1 for Qc(y) and obtain

iD L W Cox n

VDS

V

GS

Vc ( y ) VT dVc

0

Assuming that the Channel Voltage is the only voltage depending on y

we obtain for the current iD

iD

Prof. Dr. Hoppe

W

2

nCox 2 VGS VT VDS VDS

2L

CMOS Analog Design

67

Review of classical derivation of iD:

iD depends on µn and Cox = ox/tox : technology dependent

and on geometry W and L, channel width (W) and length (L)

W/L is the most important design parameter

W

2

iD

nCox 2 VGS VT VDS VDS

2L

Example: µn = 600cm2/Vs Cox= 7,0*10-8F/cm2 W=20µm L = 2µm VT=1.0V

2

iD 0, 21mA / V 2 2 VGS 1,0 VDS VDS

iD curves are inverted parabolas with maximum at VDS=VGS-VT

Beyond this voltage: negative differential transconductance

Not observed in real MOSFETs

Prof. Dr. Hoppe

CMOS Analog Design

68

Review of classical derivation of iD:

iD

W

2

nCox 2 VGS VT VDS VDS

2L

Dashed curves represent unphysical behaviour!

Prof. Dr. Hoppe

CMOS Analog Design

69

Review of classical derivation of iD:

iD-formula derived for complete channel is inverted

VGS VT

VGD VGS VDS VT

This is the linear operating region

not valid beyond the linear/saturation boundary:

VDS VGS VT VDSAT

Above VDSAT current increases no more

iD

W

2

nCox 2 VGS VT VDSAT VDSAT

2L

2

W

nCox VGS VT , saturation current

2L

Prof. Dr. Hoppe

CMOS Analog Design

70

Channel length modulation

If VDS > VDSAT the channel is no longer inverter at the drain end.

Surface potential is too low: Pinch off effect!

VDS VGS VT VDSAT

Above VDSAT the channel charge at the drain end becomes zero (very small)

Q(y=L) 0

Prof. Dr. Hoppe

CMOS Analog Design

71

Channel length modulation

Saturation effect = onset of pinch-off of channel at the drain end y = L

If VDS > VDSAT the pinch off at L‘ = L - L

Pinched off part of channel is depleted:

Q( y ) 0 für L ' y L

Vc ( y L ') VDSAT

Gradual channel approximation valid from y = 0 to y = L‘:

2

W

iD

nCox VGS VT

2L '

As L‘ reduces with increasing VDS further beyond VDSAT iD is growing in

saturation with drain-source-voltage

Prof. Dr. Hoppe

CMOS Analog Design

72

Channel length modulation

We may rewrite the saturation current

1 W

2

iD

C

V

V

L 2 L n ox GS T

1

L

L may be shown to be proportional to

L VDS VDSAT

There is the following empirical relationship

L

1

1 VDS with VDS 1

L

1 W

2

W

2

iD

n Cox VGS VT

n Cox VGS V 1 VDS

2L

1 L 2 L

L

Prof. Dr. Hoppe

CMOS Analog Design

73

Channel length modulation

Prof. Dr. Hoppe

CMOS Analog Design

74

Equivalent derivation of iD using gradual

channels:

iD = - vn(y)Q(y)W

...(2‘)

Current is charge at surface times width of the channel

moving with the electron velocity vn ~ E, therefore

vn = - μnE(y) = - μndV/dy

...(3‘)

Substituting eq.(1) and (3) in (2) we get

iDdy = μn CoxW [VGS - V(y) - VT] dV

Prof. Dr. Hoppe

CMOS Analog Design

...(4‘)

75

Review of classical derivation of iD:

Integrating eq.(4) along the channel for 0 to L gives

iD = (W/L)μnCox [(VGS – VT) – (VDS/2)] VDS

This derivation shows, that drain current is depending on

the carrier mobility, which was assumed to be

constant as in the case of the drift velocity in

conductors like copper.

However the velocity saturates at strong fields giving rise

to the velocity saturation effect in short channel

transistors and hence the mobility gets field

dependent!

Prof. Dr. Hoppe

CMOS Analog Design

76

Velocity saturation effect:

Measurements of vn as a function of E

•

•

The most important short-channel effect in

MOSFETs is the velocity saturation of carriers in the

channel.

A plot of electron drift velocity versus electric field is

shown above.

Prof. Dr. Hoppe

CMOS Analog Design

77

Impact of velocity saturation:

Velocity of electrons as a function of E:

vn =

μ nE

1 + E/Ec

vn = vsat

for E < Ec

for E >= Ec

where Ec is the critical electric field at which velocity

saturation occurs

Inserting a factor in the equation of iD, we get:

iD = K(VDS)(W/L)μnCox [(VGS – VT) – (VDS/2)] VDS

Prof. Dr. Hoppe

CMOS Analog Design

78

Impact of velocity saturation:

where

1

K(VDS) =

1 + VDS/EcL

is a SPICE parameter for modeling.

For L >> 1 μm, K(VDS) ~ 1

For short channel devices, K(VDS) < 1 resulting into

smaller iD than expected

Prof. Dr. Hoppe

CMOS Analog Design

79

Impact of velocity saturation:

How large is the current?

Assume that carrier velocity has reached limit value vn = 107 cm/s

The effective channel length Leff will be shorter than L:

Leff

iD ( sat ) W vn ( sat ) q n( x ) dx W vn ( sat ) Q

0

Since the voltage at Leff is VDSAT we have:

Leff

iD ( sat ) W vn ( sat ) q n( x ) dx W vn ( sat ) Cox VDSAT

0

Drain current is independent of channel length

Drain current is linear with drain-source-voltage

Prof. Dr. Hoppe

CMOS Analog Design

80

Impact of velocity saturation:

Short channel transistors enter the saturation region

before VDS = VGS – VT

iD ( sat ) W vn ( sat ) Cox VDSAT W µn VDSAT Cox VDSAT

VDSAT 2

W

iD ( sat ) K Cox µn VGS VT VDSAT

L

2

gleichsetzen und nach VDSAT auflösen

VDSAT

Prof. Dr. Hoppe

2

K VGS VT

3

CMOS Analog Design

81

Impact of velocity saturation (second impact):

For short channel devices, K(VGS – VT) < 1

Two transistors with same W/L and VGS = VDD will have

the following characteristics:

Prof. Dr. Hoppe

CMOS Analog Design

82

Velocity saturation (0,25µm CMOS)

W/L=25µm/2,5µm,

Imax = 5,4mA

W/L=2.5µm/0,25µm,

Imax = 2,2mA

W/L=10µm/1,0µm,

Imax = 4,3mA

Prof. Dr. Hoppe

CMOS Analog Design

83

A simple model for hand calculations:

(1) Velocity saturation occurs abruptly at E = Ec

vn = μnE

for E < Ec

vn = vsat = μnEc

for E >= Ec

(2) VDSsat at which Ec is reached is given as

VDSsat = LEc = Lvsat /μn

(3) Approximate saturation current for a short channel

device is given as

iDsat = vsat CoxW [VGS – VT – VDSsat]

Prof. Dr. Hoppe

CMOS Analog Design

84

iD Vs VGS characteristics for long and short channel

devices:

Two transistors, both with W/L = 1.5 will have

the following characteristics:

Prof. Dr. Hoppe

CMOS Analog Design

85

Threshold voltage variations in long and short

channel devices:

Long channel nMOS:

VT = f (technology, source – bulk voltage)

Short channel nMOS:

VT = f (technology, source – bulk voltage, L, W, VDS)

Prof. Dr. Hoppe

CMOS Analog Design

86

Disadvantages of short channel devices:

•

•

•

•

Reduction in gain

Cannot switch off properly due to reduction in VT

More leakage current in the „off“ condition

More dependence on transistor variables

Prof. Dr. Hoppe

CMOS Analog Design

87

Hot carrier effect:

•

•

•

•

•

•

During the last decade, transistor dimensions were

scaled down but not the power supply

Increase in the field strength causes increase in the

kinetic energy of electrons (hot electrons)

Some of the electrons become so ‘hot‘ that they can

jump over the barriers and tunnel into the oxide

Electrons are trapped in the oxide and these

additional charges increase VT of the transistors

This leads to a long term reliability problem

For an electron to become hot, a field strength

greater than 104 V/cm is needed, which is easily

possible for technologies with L < 1 µm

Prof. Dr. Hoppe

CMOS Analog Design

88

iD Vs VDS characteristics degradation:

Hot carrier effect degrades the V-I characteristics of

short channel transistors due to extensive usage or

aging problem

Prof. Dr. Hoppe

CMOS Analog Design

89

Process variations:

Device parameters vary between different wafer runs

and even on the same die!....why?

Answers :

(1) Variations of process parameters:

– impurity concentrations

– oxide thickness

– diffusion depths

(2) Temperature effects due to non uniform conditions:

– variations in sheet resistances

– variations in threshold voltages

– variations in parasitic capacitances

Prof. Dr. Hoppe

CMOS Analog Design

90

Process variations:

(3) Variations in geometry of the devices:

– limited resolution of the lithographic processes

results into variations in W/L ratios for the

neighbouring transistors

– device mismatch in circuits built on the basis of

transistor pairs, for ex: differential stages

Prof. Dr. Hoppe

CMOS Analog Design

91

Transistor typical parameter values:

0.25 µm technology, VDD = 2.5V, Minimum channel length

device

n-channel device p-channel device

Parameter

0.43

-0.40

VT0 (V)

0.4

-0.4

γ (V1/2)

0.65

-1.0

VDSsat (V)

115

-30

K‘ (μA/V2)

0.06

-0.1

λ (V-1)

0.7

0.8

2F

Prof. Dr. Hoppe

CMOS Analog Design

92

Basic Transistor Formulas:

iD 0

cutoff

linear

iD

VGS VT

W

2

nCox 2 VGS VT VDS VDS

2L

VGS VT VDSSAT

VGS VT VDSSAT

W

2

saturation iD n Cox VGS VT (1 VDS )

2L

VDSSAT = VGS-VT if not otherwise stated in the parameter table

VT VT 0

Prof. Dr. Hoppe

2F VSB 2F

CMOS Analog Design

93

Passive components

Prof. Dr. Hoppe

CMOS Analog Design

94

Passive components for building analog circuits

in CMOS technology:

•

•

•

MOS technology – planar technology

Capacitors and resistors are compatible with MOS

technology fabrication steps

Inductors are not compatible

Prof. Dr. Hoppe

CMOS Analog Design

95

Capacitors:

•

•

Used more frequently in analog integrated circuits

than in discrete designs

Applications:

– compensation capacitors in amplifiers

– used in gain determining components in charge

amplifiers

– charge storage devices in switched capacitor

filters and digital to analog converters

Prof. Dr. Hoppe

CMOS Analog Design

96

Desired characteristics for capacitors:

•

•

•

•

•

Good matching accuracy

Low voltage coefficient

High ratio of desired capacitance to parasitic

capacitance

High capacitance per unit area

Low temperature dependence

Note: Analog CMOS processes meet these criteria, pure

digital processes do not!

Prof. Dr. Hoppe

CMOS Analog Design

97

Types of capacitances in analog CMOS processes:

(1) Poly Si / oxide / channel capacitor (MOS cap)

- like a gate capacitance of MOS transistor, but n+

implant introduced to form a well between „electrodes“

for this plate capacitor

Prof. Dr. Hoppe

CMOS Analog Design

98

Types of capacitances in analog CMOS processes:

(2) Poly / oxide / poly capacitor

- top and bottom plates are made up of poly silicon

Prof. Dr. Hoppe

CMOS Analog Design

99

Types of capacitances in analog CMOS processes:

(3) Metal 3 / oxide / metal 2 capacitor

- structure similar to the poly 2 / poly 1 capacitor

Prof. Dr. Hoppe

CMOS Analog Design

100

Types of resistors:

(1) Diffused resistor:

Prof. Dr. Hoppe

CMOS Analog Design

101

Types of resistors:

(1) Diffused resistor:

- Standard process: sheet resistance is in the range

50 Ω/sq to 150 Ω/sq

- Salicided process: surface layer on silicon containing

TaSi or TiSi compounds. Sheet resistance is in the

range 5 Ω/sq to 15 Ω/sq

- Problems:

(a) capacitance to n-well

(b) voltage coefficient 100....250 ppm/V

Prof. Dr. Hoppe

CMOS Analog Design

102

Types of resistors:

(2) Polysilicon resistor:

Prof. Dr. Hoppe

CMOS Analog Design

103

Types of resistors:

(2) Polysilicon resistor:

- surrounded by a thick oxide layer

- sheet resistance is in the range 30 Ω/sq to 200 Ω/sq,

depending on doping levels

- Polysilicide process: sheet resistance is around

10 Ω/sq

Prof. Dr. Hoppe

CMOS Analog Design

104

Types of resistors:

(3) N-well resistor:

Prof. Dr. Hoppe

CMOS Analog Design

105

Types of resistors:

(3) N-well resistor:

- n-well is not heavily doped, hence the sheet

resistance is high in the range 1 kΩ/sq to 10 kΩ/sq

- Voltage coefficient is very high, so it acts as a good

pull up resistor...but not suitable for generating a

precise voltage drop

Prof. Dr. Hoppe

CMOS Analog Design

106

Performance summary of passive components in

a 0.8 µm CMOS technology:

Component type

Range of

process

values

MOS cap

2.2 to 2.7

fF/µm2

0.05 %

50 ppm/K

50 ppm/V

Poly-poly cap

0.8 to 1.0

fF/µm2

0.05 %

50 ppm/K

50 ppm/V

M1-M2 cap

0.021 to

0.025 fF/µm2

1.5 %

-

-

P+ diffusion

resistor

80 to 150

Ω/sq

0.4 %

1500 ppm/K

200 ppm/V

Prof. Dr. Hoppe

Matching Temperature

accuracy coefficient

CMOS Analog Design

Voltage

coefficient

107

Performance summary of passive components in

a 0.8 µm CMOS technology:

Component type

Range of

process

values

n+ diffusion

resistor

50 to 80 Ω/sq

0.4 %

1500 ppm/K

200 ppm/V

Polysilicon

resistor

20 to 40 Ω/sq

0.4 %

1500 ppm/K

200 ppm/V

N-well resistor

1 to 2 kΩ/sq

?

8000 ppm/K

10,000

ppm/V

Prof. Dr. Hoppe

Matching Temperature

accuracy coefficient

CMOS Analog Design

Voltage

coefficient

108

Temperature dependence of

MOS devices

Prof. Dr. Hoppe

CMOS Analog Design

109

Temperature dependence of MOS components:

•

•

Temperature dependence of MOS components –

important performance characteristic in analog circuit

design

The temperature behavior of passive components is

usually expressed in terms of a fractional temperature

coefficient TCF defined as:

TCF = 1.dX

X dT

•

X can be resistance or capacitance of the passive

component. Usually TCF is multiplied by 106 and

expressed in units of part per million per oC

Prof. Dr. Hoppe

CMOS Analog Design

110

Temperature dependence of drain current iD of a

MOS transistor:

•

•

•

•

Most sensitive parameters in the drain current

equation are µ (mobility) and VT (threshold voltage)

Due to scattering at thermally induced lattice

vibrations, temperature dependence of µ is given as

µ = KµT -1.5

Temperature dependence of VT is approximated as

VT(T) = VT(T0) – α (T - T0)

α = 2.3 mV/oC and the expression is valid over the

range 200 - 400 K

In total iD decreases with increasing temperature

iD | 125 oC = 0.7 iD | 25 oC

Prof. Dr. Hoppe

CMOS Analog Design

111

Temperature dependence of reverse biased diode

current:

•

When VD < 0, the diode current is given as

-iD = Is = qA

(

)

Dppn0

Dnnp0

qAD .(ni)2

+

=

Lp

Ln

L

N

= KT3exp(- VG0 / Vt)

where D, L, N are diffusion constant, diffusion length and

impurity concentration of the dominant term (either n or p)

VG0 = band gap voltage of Si at 300 K (1.205V)

Vt = thermal voltage kT/q

Prof. Dr. Hoppe

CMOS Analog Design

112

Temperature dependence of reverse biased diode

current:

•

Differentiating with respect to T results in

dIs/dT = (3KT3/T)exp(-VG0 / Vt)

+ (qKT3VG0/KT2)exp(-VG0 / Vt)

3IS ISVG0

=

+

T

TVt

•

The TCF for the reverse diode current is

1 dIS 3 VG0

= +

IS dT T TVt

•

Reverse diode current doubles for every 5 oC increase

Prof. Dr. Hoppe

CMOS Analog Design

113

Example:

Calculate the TCF for the reverse diode current for 300 K

and Vt = 0.025 V

Prof. Dr. Hoppe

CMOS Analog Design

114

Analog CMOS subcircuits

Prof. Dr. Hoppe

CMOS Analog Design

115

MOS switch:

•

•

•

•

MOS switch – a very useful device

Analog circuits: the MOS switch is used in

multiplexers, modulation and switched capacitor

filters

Digital circuits: used in transmission gate logic,

dynamic latches, etc.

MOS transistor as a switch:

Prof. Dr. Hoppe

CMOS Analog Design

116

Model for a switch:

•

•

An ideal switch is a short circuit when ON and an

open circuit when OFF

Equivalent circuit for a voltage controlled non ideal

switch:

Prof. Dr. Hoppe

CMOS Analog Design

117

Model for a switch:

VC

= control voltage

A, B, C = terminals; C being the control terminal

rON

= ON resistance

rOFF

= OFF resistance (very high)

VOS

= offset voltage between A and B when the

switch is ON

IA, IB = leakage currents

IOFF

= offset current when the switch is OFF

CA, CB = parasitic capacitances at the terminals to GND

CAC, CBC = capacitive coupling between A and B,

contribute to the effect called charge

feedthrough – big problem in MOS switches!

Prof. Dr. Hoppe

CMOS Analog Design

118

ON resistance of a MOS switch:

•

•

•

•

rON consists of the series combination of rD, rS and

the channel resistance

rD, rS – parasitic drain and source resistances (~ 1Ω)

rchannel – channel resistance (~ 50Ω)....dominant!

Expression for small-signal channel resistance:

1

rON =

diD/dVDS

Q

L

=

K‘W(VGS - VT - VDS)

where Q designates the quiesent point of the

transistor

Prof. Dr. Hoppe

CMOS Analog Design

119

Range of voltages at the terminals of a MOS

switch compared to the gate (control) voltage:

•

•

•

•

•

nMOS: VG larger than the source to drain voltage to

switch the transistor ON (at least higher by VT)

pMOS: VG has to be less than the source to drain

voltage to switch the transistor ON

nMOS: Bulk has to be connected to the most

negative voltage

pMOS: Bulk has to be connected to the most

positive voltage

Consider nMOS switch:

VG = VDD , VBulk = VSS , then the transistor is ON until

VDD – VT >= VBA = VSD

Prof. Dr. Hoppe

CMOS Analog Design

120

Small signal on-resistance of a MOS switch as

a function of the Control Voltage:

Prof. Dr. Hoppe

CMOS Analog Design

121

Large signal behavior of the MOS-switch

For the NMOS-switch VDS must never exceed VGS-VT

Otherwise the device switches off and ron is in the

100kOhm range!

Hence the maximum voltage VDD or (any voltage

above VGS – VT) can never be transferred from drain

to source of a switch. Instead VDD –VT (a degraded

voltage) is observed at the output of the switch!

The corresponding abservations will be made for a

PMOS-switch!

Prof. Dr. Hoppe

CMOS Analog Design

122

Single stage amplifiers

Prof. Dr. Hoppe

CMOS Analog Design

123

Applications of CMOS amplifiers:

•

•

Analog applications:

- to overcome noise

- to drive a next stage

- used in feedback systems

- to provide logic levels for interfacing to digital

circuits

Digital applications:

- to drive a load

Prof. Dr. Hoppe

CMOS Analog Design

124

Basic notions:

•

Generalised system

transfer curve:

x may be current or

voltage

•

y(t) = α0 + α1x(t) + α2x2(t) + ...... + αnxn(t)

for x1 <= x <= x2

In a narrow range of x, y can be approximated with

a linear relationship:

y(t) ~ α0 + α1x(t)

where α0 = operating point

α1 = linear (small signal) gain

•

Prof. Dr. Hoppe

CMOS Analog Design

125

Basic notions:

•

•

•

•

If α1x(t) << α0, then the operating point OP is very

slightly disturbed and linearization around OP is

possible – small signal analysis

Δy = α1Δx : linear relationship between increments

of input and output

If x(t) varies over a large range, then the higher

order terms become important – large signal

analysis

If the slope of the characteristics varies with the

signal - Nonlinearity

Prof. Dr. Hoppe

CMOS Analog Design

126

Competing design targets for amplifiers:

1.

2.

3.

4.

5.

6.

7.

8.

Gain

Speed

Power consumption

Supply voltage

Linearity

Noise

Maximum voltage swing at the output

Input and output impedance

Prof. Dr. Hoppe

CMOS Analog Design

127

Amplifier design octagon:

- Several targets...and complex dependencies !

Prof. Dr. Hoppe

CMOS Analog Design

128

Digital circuit design targets:

•

Three targets:

- die size

- speed

- power consumption

Prof. Dr. Hoppe

CMOS Analog Design

129

CMOS amplifiers

Prof. Dr. Hoppe

CMOS Analog Design

130

Basic principles:

•

•

MOSFET translates variations in its gate-source

voltage to a small signal drain current

If a resistive load is used, these current variations in

turn produce variations in the output voltage

Prof. Dr. Hoppe

CMOS Analog Design

131

Amplifier configurations:

1.

2.

3.

4.

5.

Common source stage (CS)

Source follower or common drain stage (SF)

Common gate stage (CG)

Cascode stage: cascade of CS and CG stage

Differential amplifiers

Prof. Dr. Hoppe

CMOS Analog Design

132

Common source amplifier configuration (CS):

Small signal model for the

saturation region:

Prof. Dr. Hoppe

CMOS Analog Design

133

Input – output characteristics:

1. Vin < VTH:

Vout = VDD

2. Vin >= VTH:

M1 is ON

saturation region

3. Vin >= Vout + VTH:

M1 in linear

region

Prof. Dr. Hoppe

CMOS Analog Design

134

Input – output characteristics:

1. Vin < VTH:

Vout VDD

2. Vin >= VTH:

1

W

2

Vout V DD R D n Cox

Vin VTH

2

L

3. Vin >= Vout + VTH:

Vout

1

W

2

2Vin VTH Vout Vout

VDD R D n Cox

2

L

Prof. Dr. Hoppe

CMOS Analog Design

135

Supressing short channel effects:

•

•

•

Analog circuits: Lmin of technology is not utilized.

Instead analog circuits use 4...5 times Lmin

For C35 process analog Lmin ~ 1.5 µm

Longer transistor length results in

(1) negligible subthreshold current

(2) small channel length modulation effect

(3) small velocity saturation effect

Prof. Dr. Hoppe

CMOS Analog Design

136

Deep triode region:

If Vin is high enough to drive M1 into deep triode region,

Vout << 2(Vin - VTH) and from the equivalent circuit

V out V DD

R

R

on

RD

Ron

on

R

D

VDD

1 RD / Ron

RD

1

W

nCox

V in V T VDS

L

Vout

Prof. Dr. Hoppe

V DD

W

1 n Cox R D V in V TH

L

CMOS Analog Design

137

Small signal gain:

•

In deep triode region, we have a voltage divider while in

the saturation region we have the proper amplifier

operation due to the quadratic dependence of the

current:

1

W

2

Vout V DD R D

Vin VTH

n Cox

2

L

•

The small signal gain is given as:

Vout

A

Vin

W

Vin VTH

R D n Cox

L

gmR D

Prof. Dr. Hoppe

CMOS Analog Design

138

Transconductance gm:

•

•

Small signal parameter

In saturation,

ID

VDS fixed

gm

Vin

W

VGS VTH

n Cox

L

2 ID

W

2 n Cox I D

L

VGS VTH

g m f VGS VTH

Prof. Dr. Hoppe

CMOS Analog Design

139

Transconductance gm:

•

•

Thus transconductance gm is dependent on input

voltage!

Gain A varies with Vin...Nonlinearity problem for

large signals!

Prof. Dr. Hoppe

CMOS Analog Design

140

How to maximize the voltage gain?

W

VRD

2

C

A

ID

n ox

L

ID

Where VRD is voltage drop across load resistance

W VRD

A 2 n Cox

L

ID

•

To increase the gain:

- make W/L larger

- make VRD large.... make RD large

- make ID smaller (make transistor weaker)

Prof. Dr. Hoppe

CMOS Analog Design

141

Trade-offs in maximizing the voltage gain:

•

•

•

Larger W/L larger input capacitance

Larger VRD smaller output swing

If VRD is kept constant ID has to be made smaller

RD must be increased

higher time constants at the output !

•

Trade-off: gain, BW, voltage swing !

Prof. Dr. Hoppe

CMOS Analog Design

142

Trade-offs in maximizing the voltage gain:

•

For large values of RD, the effect of channel length

modulation in M1 becomes significant

•

1

W

2

C

Vout VDD R D

Vin VTH 1 Vout

n ox

2

L

Vout

W

Vin VTH 1 Vout

R D n Cox

Vin

L

Vout

1

W

2

Vin VTH

R D n C ox

2

L

Vin

•

Using the approximation

I D 1 2 n Cox W LVin VTH

2

Prof. Dr. Hoppe

CMOS Analog Design

143

Trade-offs in maximizing the voltage gain:

We obtain:

A R Dg m R D I DA

•

Hence

gmR D

A

1 R D I D

•

Thus

Prof. Dr. Hoppe

decreases the amplification factor !

CMOS Analog Design

144

Small signal model for channel length modulation:

•

•

gmR D

A

1 R D I D

I D 1 rO ,

rO R D

A g m

rO R D

Since

Prof. Dr. Hoppe

CMOS Analog Design

145

Intrinsic gain:

•

•

Intrinsic gain = upperbound of the overall gain

Ideal current source infinite impedance

• lim R D , A g m

rO

rO

1

RD

results in

A g m rO

•

Todays technology:

gmrO is between 10 to 30

Prof. Dr. Hoppe

CMOS Analog Design

146

CS stage with diode connected load:

•

•

•

•

In MOS technology, resistors are complicated to

implement

Hence „active loads“ or so called „diode connected

transistors“ are used

MOSFET acts as small signal resistor when gate and

drain is shorted

Diode connected transistors are always in saturation

because VDS = VGS

Prof. Dr. Hoppe

CMOS Analog Design

147

Small signal equivalent circuit:

•

As VDS = VGS

V1 = VX

VX

IX

g m VX

rO

1

1

Impedence

rO

gm

gm

Prof. Dr. Hoppe

CMOS Analog Design

148

Active load with body effect:

Vx is the source potential of the transistor in

the operating point: hence Vbs equals Vx = V1

VX

I X g m g mb VX

rO

Prof. Dr. Hoppe

CMOS Analog Design

149

Active load with body effect:

•

VX

1

Impedance

IX g g 1

m

mb

rO

1

1

rO

g m g mb

g m g mb

•

Thus the body effect reduces the impedance !

Prof. Dr. Hoppe

CMOS Analog Design

150

Voltage gain of CS stage with diode connected

load:

•

For negligible λ,

1

A g m1

g m 2 g mb 2

g mb 2

g m1 1

where

gm2 1

gm2

•

Considering device dimensions,

A

Prof. Dr. Hoppe

2 n C ox W L 1 I D1

2 n C ox W L 2 I D 2

1

1

CMOS Analog Design

151

Voltage gain of CS stage with diode connected

load:

•

Since ID1 ID2 ,

A

Prof. Dr. Hoppe

W L 1 1

W L 2 1

CMOS Analog Design

152

CS stage with diode connected load – Large

signal analysis:

•

ID1 ID2

1

1

W

W

2

2

n Cox Vin VTH1 n Cox VDD Vout VTH 2

2

2

L 1

L 2

W

W

Vin VTH 1 VDD Vout VTH 2

L 1

L 2

Note: If VTH2 depends only slightly on Vout (weak body

effect), then we have a linear behavior and Vout is

proportional to Vin

Prof. Dr. Hoppe

CMOS Analog Design

153

CS stage with diode connected load – Large

signal analysis:

•

Differentiating both sides w.r.t Vin

W

W Vout VTH 2

Vin

L 1

L 2 Vin

•

With application of the chain rule

Vout

VTH 2 VTH 2 Vout

Vin Vout Vin

Vin

we get

Vout

A

Vin

Prof. Dr. Hoppe

W L 1 1

W L 2 1

CMOS Analog Design

The result matches

with the small

signal analysis !

154

Input / output characteristics of active load CS

stage:

•

•

At point A, M1 enters the triode region (strong

nonlinearity !)

Above VTH1 and below VA,

Vout Vin (linear behavior)

Prof. Dr. Hoppe

CMOS Analog Design

155

CS stage with pMOS active load:

•

•

•

•

To improve amplification we use CS

stage with pMOS active load

pMOS output node can charge upto

full VDD .....more voltage swing !

No body effect 0

A

•

n W L 1

p W L 2

Gain depends very weakly on device dimensions

Prof. Dr. Hoppe

CMOS Analog Design

156

CS-Stufe mit pMOS-Last

Ausgangsspannungsbereich

•

Vout(max) = VDD – Vtp

•

Vout(min): komplizierter:

Vout(min)

VDD

vds1 vgs1 Vtn vout vin Vtn

M1 ungesättigter Bereich:

v ²

v ²

W

W

id 1 µnCox ((vgs1 Vtn )vds1 ds1 ) µnCox ((vDD Vtn )vout out )

L

2

L

2

id 2

Prof. Dr. Hoppe

µ p Cox W

µ p Cox W

(vsg 2 Vtp )²

(vDD vout Vtp )²

2 L

2 L

CMOS Analog Design

157

CS-Stufe mit pMOS-Last

Ausgangsspannungsbereich: Gleichsetzen

•

id1 = id2 und auflösen nach Vout

ergibt

VDD VT

vout (min) VDD VT

µ pW p

1

µnWn

Annahme: Einsatzspannung von pMOS (Betrag) und

nMOS gleich VT

Prof. Dr. Hoppe

CMOS Analog Design

158

CS-Stufe mit pMOS-Last

Verstärkung A = Vout/Vin und

Ausgangswiderstand Rout:

Aufsummieren aller Ströme, die in den

Ausgangsknoten fließen:

0 gm1vin gds1vout gm 2vout gds 2vout

Vout

g m1

µn COX W1 L2

Vin g ds1 g m 2 g ds 2

µ p COX W2 L1

1

1

Rout

gds1 gm 2 gds 2 gm 2

Prof. Dr. Hoppe

CMOS Analog Design

159

CS-Stufe mit pMOS-Last

3dB Frequenz: Verstärkung sinkt hier auf 70%:

-3dB = 1/[Rout(Cout)]

•

Cout ist die gesamte kapazitive Last am Ausgang:

– Externe Eingangskapazität

– Leitungskapazität

– Parasitäre Transistorkapazitäten

Beispiel: Rout = ro für einen pMOS-Transistor W/L = 3/1, in

dem der Drainstrom 60µA fließt ist bei Cout = 5 pF:

1/ ro gm 2µ p Cox (W / L) I D 2 60 3 50µA / V 134µA / V

roC 5 pF /134µA / V 0,037 106 s

3dB 27 Mrad / s f 3dB 4,3MHz

Prof. Dr. Hoppe

CMOS Analog Design

160

AMS 0,35µm CMOS Technology

AMS CSD 0,35µm CMOS 3,3V Prozess

Parameter

Beschreibung

Parameterwerte

NMOS

PMOS

Einheit

Vth0

Einsatzspannung VBS = 0

0,5 0,05 -0,65 0,5

V

K’

Transistorleitwert

175 10% 60 10%

µA/V2

Substratsteuerfaktor

0,58

V1/2

Kanallängenmodulationsfaktor

0,06L=1µm 0,06 L=1µm

0,04L=2µm 0,04 L=2µm

V-1

2F

Oberflächenpotential

starker Inversion

0,8

V

bei

0,42

0,8

*Level 1 SPICE Modell CSD 0,35

.MODEL MOSN NMOS VTO=0.5 KP=175U GAMMA=0.58 LAMBDA=0.06 PHI= 0.8

.MODEL MOSP PMOS VTO=-0.65 KP=60U GAMMA=0.42 LAMBDA=0.06 PHI=0.8

Prof. Dr. Hoppe

CMOS Analog Design

161

CS-Stage with pMOS-Load

NMOS: W/L =5.5 PMOS = 1.0 CSD technology

*Common Source Amplifier

VDD 1 0 DC 3.3

VIN 2 0 DC 0

MP out out 1 1 MODP W = 1U L = 1U

MN out 2 0 0 MODN W = 5.5U L = 1U

CL out 0 5P

.model MODN NMOS VTO=0.5 KP=175U GAMMA=0.58 LAMBDA=0.06 PHI= 0.8

.MODEL MODP PMOS VTO=-0.65 KP=60U GAMMA=0.42 LAMBDA=0.06

PHI=0.8

.DC VIN 0.0 3.3 5U

.PRINT DC V(out) V(in)

.END

Prof. Dr. Hoppe

CMOS Analog Design

162

CS-Stage with pMOS-Load

NMOS: W/L =5.5 PMOS = 1.0 CSD technology

Prof. Dr. Hoppe

CMOS Analog Design

163

CS-Stage with pMOS-Load

NMOS: W/L =5.5 PMOS = 1.0 CSD technology

*Common Source Amplifier

VDD 1 0 DC 3.3

VIN 2 0 DC 0.9 AC 1.0

MP out out 1 1 MODP W = 1U L = 1U

MN out 2 0 0 MODN W = 5.5U L = 1U

CL out 0 5P

.model MODN NMOS VTO=0.5 KP=175U GAMMA=0.58 LAMBDA=0.06 PHI= 0.8

.MODEL MODP PMOS VTO=-0.65 KP=60U GAMMA=0.42 LAMBDA=0.06 PHI=0.8

*.DC VIN 0.0 3.3 5U

.AC DEC 20 100 10MEG

.PRINT AC VDB(out)

.END

Prof. Dr. Hoppe

CMOS Analog Design

164

CS-Stage with pMOS-Load

NMOS: W/L =5.5 PMOS = 1.0 CSD technology

Prof. Dr. Hoppe

CMOS Analog Design

165

CS-Stufe mit pMOS-Last

Designrezeptur: W zu L bei geg. Verstärkung

Hängt von den Vorgaben ab. In der Regel wird eine

Verstärkung vorgegeben, aus der sich alles weitere

ableitet.

Im Labor werden wir einen Verstärker entwerfen, der eine

Verstärkung von A = - 4 haben soll. Daraus folgt:

Aus Gleichung auf Folie 155 folgt dann ein

Weitenverhältnis für pMOS- und nMOS-Transistor.

Nächster Schritt ist dann zu verifizieren, dass die

Verstärkung auch tatsächlich erreicht wird. Dazu ist die

Kennlinie also Vout = f(Vin) aufzunehmen.

Die Verstärkung folgt dann als Ableitung von Vout nach Vin

Prof. Dr. Hoppe

CMOS Analog Design

166

CS-Stufe mit pMOS-Last

Designrezeptur: Arbeitspunkt

Aus der simulierten Verstärkung folgt dann der

Arbeitspunkt, der implizit für die Kleinsignalanalyse

verwendet wurde, aus der die Formel für A stammt.

Aus der VerstärkungskennLinie kann nun der Arbeitspunkt abgelesen werden:

Kennlinie

Vin = 0,67V / Vout = 1,91V

Verstärkung

Prof. Dr. Hoppe

CMOS Analog Design

167

CS-Stufe mit pMOS-Last

Designrezeptur: Output Swing

Aus der Verstärkungskennlinie kann die minimale und

maximale Ausgangsspannung abgelesen werden:

Simulation:

Vout(max) = 2,98V

Vout(min) = 0,06V

Theorie:

Vout(max) = 2,8V

Vout(min) = 0,08V

Prof. Dr. Hoppe

CMOS Analog Design

168

CS-Stufe mit pMOS-Last

Designrezeptur: Frequenzverhalten

Am Arbeitspunkt können wir den Strom in M1 und damit in

M2 ausrechnen

damit folgt gm2 (Eingangsleitwert

pMOS)

Wp

2

1

iD1 iD 2 µ pCox

VgsPMOS ( Arbeitspunkt ) VTp

2

Lp

g m 2 2µ p Cox (W / L) p I D

roC C / g m 2

3dB

Prof. Dr. Hoppe

g m 2 rad

3dB

f 3dB

Hz

C s

2

CMOS Analog Design

169

CS-Stufe mit pMOS-Last

Designrezeptur: Frequenzverhalten

Simulation:

f-3dB = 4,1 MHz

Verst. = 12,1 dB

Theorie:

f-3dB = 6,2 MHz

Verst. = 12 dB

Prof. Dr. Hoppe

CMOS Analog Design

170

Source follower:

•

•

CS stage has a good voltage gain, but load impedance

has to be high

If the load impedance is low, a „buffer“ is needed for

impedance matching

Prof. Dr. Hoppe

CMOS Analog Design

171

Source follower:

•

Source follower (or „common drain stage“) may

operate as a voltage buffer

Prof. Dr. Hoppe

CMOS Analog Design

172

Source follower – input/output characteristics:

•

Vout follows Vin with a voltage difference (level shift)

equal to VGS

Vout

Prof. Dr. Hoppe

1

W

2

Vin VTH Vout R S

n Cox

2

L

CMOS Analog Design

173

Small signal gain (large signal analysis):

Vout

•

1

W

Vin VTH Vout 2 R S

n Cox

2

L

Differentiating both sides w.r.t. Vin

VTH Vout

Vout 1

W

R S

n Cox

2 Vin VTH Vout 1

Vin 2

L

Vin Vin

Vout

VTH

• since

Vin

Vin

W

n Cox

Vin VTH Vout R S

Vout

L

Vin 1 C W V V V R 1

n ox

in

TH

out

S

L

Prof. Dr. Hoppe

CMOS Analog Design

174

Small signal gain (large signal analysis):

•

W

With g m n Cox

Vin VTH Vout we get:

L

gmRS

A

1 g m g mb R S

Prof. Dr. Hoppe

CMOS Analog Design

175

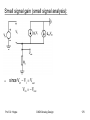

Small signal gain (small signal analysis):

•

since Vin V1 Vout

Vbs Vout

Prof. Dr. Hoppe

CMOS Analog Design

176

Small signal gain (small signal analysis):

Vout

g m1V1 g mb 1Vout

•

RS

Vout

A

will result in

Vin

gmRS

A

1 g m g mb R S

•

Maximum possible gain = 1

Prof. Dr. Hoppe

CMOS Analog Design

177

Drawback of RS implemented as ohmic resistor:

•

•

•

•

ID1 depends strongly on input DC level

If Vin changes from 1.5 to 2.0 V (10 % increase)

then ID1 increases by a factor of „2“

Hence VGS – VTH increases by √2

highly non linear I/O characteristics !

Improvement: instead of RS we take

a constant current source M2 to get

a linear behavior

Prof. Dr. Hoppe

CMOS Analog Design

178

Output impedance of SF with constant current

source as load:

•

V1 VX

I X g m VX g mb VX 0

Prof. Dr. Hoppe

CMOS Analog Design

179

Output impedance of SF with constant current

source as load:

VX

1

R out

• Hence

IX

g m g mb

•

Note: Body effect decreases the output resistance of the

source follower !

Prof. Dr. Hoppe

CMOS Analog Design

180

Example:

Source follower:

W/L = 20µm/0.5µm

VTH0 = 0.6 V

|2ΦF| = 0.7 V

µnCox = 50 µA/V2

γ = 0.4 V2

I1 = 200 µA

Q1: What is Vout for Vin = 1.2 V?

Q2: If I1 is produced by an nMOS device, what is the

minimum W/L ratio for which M2 remains saturated?

Prof. Dr. Hoppe

CMOS Analog Design

181

Solution A1:

•

VTH depends on Vout

Iterative solution:

(1) we calculate Vout for VTH0

(2) we calculate VTH for Vout obtained in (1)

1

W

2

I D n C ox Vin VTH Vout

2

L

2I D

2

Vin VTH Vout

W

n C ox

L

2*200 A 2

2

1.2 0.6 Vout

V

50 A *40

Prof. Dr. Hoppe

CMOS Analog Design

182

Solution A1:

Vout 0.153 V

•

Now,

VTH VTH 0 2F VSB 2F

VTH 0.6 0.4 0.7 0.153 0.7

0.635 V

•

•

Using the new VTH the improved value of Vout is 0.119 V,

which is approximately 35 mV less than the calculated

value.

The next iterations yield VTH = 0.635V 0.627V and

Vout = 0.117V 0.125V

Prof. Dr. Hoppe

CMOS Analog Design

183

Solution A2:

•

•

•

•

Consider transistor in place of current source:

Drain-source voltage of M2 is 0.119 V

Device is saturated only if VGS – VTH < 0.119 V

In the saturation region we have,

1

W

2

I D 200 A n Cox 0.119

2

L 2

283 m

W

L 2 min 0.5 m

Prof. Dr. Hoppe

CMOS Analog Design

184

Drawbacks of the SF configuration:

•

Source followers exhibit a high input impedance and a

moderate output impedance, but at the cost of two

drawbacks:

(1) nonlinearity

(2) voltage headroom limitation

Prof. Dr. Hoppe

CMOS Analog Design

185

Nonlinearity of the SF configuration:

•

•

•

•

Even with an ideal current source I1 the I/O

characteristics display a nonlinearity due to the

dependence of VTH on Vsource

Submicron technology: rO of the transistor also changes

with VDS additional nonlinear effects !

Nonlinearity due to body effect can be eliminated if the

bulk is tied to the source

Because all nMOS devices have a common bulk

potential, this is only possible for pMOS devices in a

n-well technology

Prof. Dr. Hoppe

CMOS Analog Design

186

Nonlinearity of the SF configuration:

•

pMOS source follower with no body effect:

•

Price paid: PFET have a lower carrier mobility leading to

higher output impedance than for a nMOS source

follower

Prof. Dr. Hoppe

CMOS Analog Design

187

Voltage headroom limitation of SF:

•

Source followers shift the level of the signal by VGS

consuming voltage headroom and hence limiting the

voltage swing

Prof. Dr. Hoppe

CMOS Analog Design

188

Voltage headroom limitation of SF:

•

•

•

Without source follower: Vmin at node X is VGS1 – VTH1 for

having M1 in saturation

With the source follower: Vmin at node X should be

greater than VGS2 + (VGS3 – VTH3) so that M3 is in

saturation

For same overdrive voltages in M1 and M3, voltage

swing allowable at X is reduced by VGS2

Prof. Dr. Hoppe

CMOS Analog Design

189

Common gate stage (CG):

Prof. Dr. Hoppe

CMOS Analog Design

190

Common gate stage (CG):

•

•

•

•

•

In the CS-Stage and for Source-Followers input signal is

applied to a gate of a MOSFET.

If the input is applied to the source terminal of a

MOSFET and output is taken at the drain terminal we

have a Comon Gate Stage

Gate is connected to a dc voltage to establish proper

operating conditions

Bias current flows directly through input signal source

– direct coupling

M1 can be biased by a constant current source, with the

signal capacitively coupled to the circuit

– capacitive coupling

Prof. Dr. Hoppe

CMOS Analog Design

191

Direct coupling – Large signal analysis:

•

•

•

Assume that Vin decreases from a large positive value

Vin >= Vb – VTH: M1 is off and Vout = VDD

For lower values of Vin: M1 goes into saturation

1

W

2

Vb Vin VTH

I D n Cox

2

L

•

As Vin decreases, so does Vout, eventually driving M1 into

the triode region if

1

W

Vb Vin VTH 2 R D Vb VTH

VDD n Cox

2

L

Prof. Dr. Hoppe

CMOS Analog Design

192

CG input – output characteristics:

•

If M1 is saturated, output voltage can be expressed as:

Vout

1

W

Vb Vin VTH 2 R D

VDD n Cox

2

L

Prof. Dr. Hoppe

CMOS Analog Design

193

CG stage small signal gain:

•

Small signal gain can be obtained by differentiating w.r.t.

Vin

Vout

W

VTH

n Cox Vb Vin VTH 1

Vin

L

Vin

•

R D

Since VTH Vin VTH VSB , we have

Vout

W

n Cox

R D Vb Vin VTH 1

Vin

L

A g m 1 R D

Prof. Dr. Hoppe

Gain is positive !

CMOS Analog Design

194

CG stage input impedance:

•

For λ = 0, the impedance seen at the source of M1 is the

same as the output impedance in the case of source

follower

1

1

g m g mb g m 1

•

•

Thus, the body effect decreases the input impedance!

Low input impedance is useful for certain applications

Prof. Dr. Hoppe

CMOS Analog Design

195

CG stage input can be a current:

•

Vout

The transconductance

can be obtained by by

I in

creating the small signal

VDD

equivalent circuit and by

RD

Vout

replacing the current source

by an effective voltage source.

Prof. Dr. Hoppe

CMOS Analog Design

Vb

Iin

Rp

196

CG stage input can be a current:

•

Small signal circuit:

Vout

+

V1

gmV1

ro

gmbVbs

RD

_

Rp

Vin

Vout

( g m g mb )ro 1

I in ro ( g m g mb )ro RP RD

Prof. Dr. Hoppe

CMOS Analog Design

197

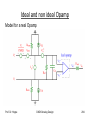

Cascode stage:

•

•

Input signal of a CG-stage may be a current

A common source stage converts a voltage signal

into a current signal

• Cascade of a common source and a common gate

stage is called a „cascode stage“

• A cascode (cascaded triode, vacuum tube days)

offers advantages over simple CS-stages:

1. High output impedance!

2. High voltage gain!

Prof. Dr. Hoppe

CMOS Analog Design

198

Cascode stage:

•

•

•

•

•

•

Prof. Dr. Hoppe

Cascade of a common

source and a common

gate stage is called a

„cascode stage“

M1 generates small signal

drain current proportional

to Vin

M2 routes this current to

RD

M1 is the input device

M2 is the cascode device

M1 and M2 carry the same

current

CMOS Analog Design

199

Cascode stage bias conditions:

•

•

•

M1 is saturated if VX >= Vin – VTH1

To keep M1 and M2 both in saturation,

VX = Vb – VGS2

Hence, Vb – VGS2 >= Vin – VTH1

Or Vb = Vin + VGS2 – VTH1

•

•

M2 in saturation Vout >= Vb – VTH2

Hence Vout >= Vin – VTH1 + VGS2 – VTH2

•

If Vb is chosen to keep M1 at the edge of saturation,

minimum output voltage for which both transistors

operate in saturation is equal to the overdrive voltage of

M1 plus that of M2

Prof. Dr. Hoppe

CMOS Analog Design

200

Voltages in cascode stage:

Prof. Dr. Hoppe

CMOS Analog Design

201

Cascode stage – large signal analysis:

•

•

Vin = 0 V

Vin < VTH1

•

Vin >= VTH1

•

Vin sufficiently

large

Prof. Dr. Hoppe

Vout = VDD

M1 and M2 are „off“

Vout = VDD

VX = Vb – VTH2

M1 is „on“

Vout drops as M1 draws current

VGS2 increases as ID2 increases

hence VX drops

VX drops below Vin by VTH1

- M1 enters triode region

Vout drops below Vb by VTH2

- M1 and M2 are in triode region

CMOS Analog Design

202

Cascode stage – large signal analysis:

•

Main advantages of cascode structure:

- high output impedance

2

- high voltage gain proportional to g m

Prof. Dr. Hoppe

CMOS Analog Design

203

Cascode stage – SPICE-Simulation

•

•

AMS C35 with pull-up 3/1, NMOS Transistors 30/1

VBIAS = VDD/2

Prof. Dr. Hoppe

CMOS Analog Design

204

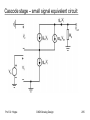

Cascode stage – small signal equivalent circuit:

Prof. Dr. Hoppe

CMOS Analog Design

205

Cascode stage – output impedance:

•

The circuit can be viewed as a degenerate commonsource with a source resistor rO1

Prof. Dr. Hoppe

CMOS Analog Design

206

Cascode stage – output impedance:

•

Using the equation of output resistance for common

source stage,

R out 1 g m 2 g mb 2 rO 2 rO1 rO 2

•

•

Assuming g m rO

1 , we have

R out g m 2 g mb 2 rO 2 rO1

M2 boosts the output impedance of M1 by a factor of

g m2 g mb 2 rO2 !!

Prof. Dr. Hoppe

CMOS Analog Design

207

Cascode stage – voltage gain:

•

Voltage gain of a cascode stage is given as:

A gm1 gm2 gmb2 rO 2 rO1

•

•

•

The maximum voltage gain is roughly equal to the

square of the intrinsic gain of the transistors

High output impedance of the cascode stage results in a

high voltage gain !

A simplified formula without body effect:

A

gm1

2 K N '(W1 / L1 )

gds 3

3P 2 I

Transistor „3“ is a PMOS-Fet connected to Vdd implementing

the pull-up-resistor

Prof. Dr. Hoppe

CMOS Analog Design

208

Cascode stage – Design Procedure:

•

The following relations determine the properties of the

amplifier:

Prof. Dr. Hoppe

CMOS Analog Design

209

Cascode stage – Design Procedure:

•

For cascode amplifiers we have the folllowing design

parameters:

1. The W/L-ratios for three transistors

2. The dc current I

3. The bias voltages

•

Typical specifications are: supply voltage VDD, small

signal gain A, the max. and min. output voltage swing

vout(max) and vout(min), and the power dissipation P

•

Example: VDD = 3,3V, A =-50 V/V, P = 1mW, Vout(max) =

2,8V and Vout(min) = 1,4V, Slew Rate 10V/µs @ 10pF

Prof. Dr. Hoppe

CMOS Analog Design

210

AMS 0,35µm CMOS Technology

AMS CSD 0,35µm CMOS 3,3V Prozess

Parameter

Beschreibung

Parameterwerte

NMOS

PMOS

Einheit

Vth0

Einsatzspannung VBS = 0

0,5 0,05 -0,65 0,5

V

K’

Transistorleitwert

175 10% 60 10%

µA/V2

Substratsteuerfaktor

0,58

V1/2

Kanallängenmodulationsfaktor

0,06L=1µm 0,06 L=1µm

0,04L=2µm 0,04 L=2µm

V-1

2F

Oberflächenpotential

starker Inversion

0,8

V

bei

0,42

0,8

*Level 1 SPICE Modell CSD 0,35

.MODEL MOSN NMOS VTO=0.5 KP=175U GAMMA=0.58 LAMBDA=0.06 PHI= 0.8

.MODEL MOSP PMOS VTO=-0.65 KP=60U GAMMA=0.42 LAMBDA=0.06 PHI=0.8

Prof. Dr. Hoppe

CMOS Analog Design

211

Cascode stage – Design Procedure:

1. P sets an upper bound 1mW/3,3V = 330µA, Slew Rate

sets a lower bound 100µA: We take I = 200µA

2. We calculate (W/L)3 since all other numbers are known in

the relation for M3 in the figure

W3

2I

400µA

26,7

L3 K P '(VDD vout (max))2 60µA / V 2 (3.3 2.8)2V 2

•

The current source on the upper left-hand side has the

same dimensions if IBIAS = I

3. Next we obtain (W/L)1 from the relation on the lower right

of the figure

2

2

W1 A I 50 0.06 200µA

L1

Prof. Dr. Hoppe

2KN '

2 175µA / V

CMOS Analog Design

2

51,5

212

Cascode stage – Design Procedure:

4. Next we calculate (W/L)2

•

First we need VDS1(sat) and use the vout(min)-spec to

obtain VDS2(sat)

vDS 1 ( sat )

2I

400µA

0,67V

2

K N '(W1 / L1 )

175µA / V 51,5

•

Subtracting this figure from 1.4V yields VDS2(sat)=0.73V

•

Therefore

W2

2I

400µA

4,3

2

2

2

L2 K N 'VDS 2 ( sat ) (0,73) 175µA / V

Prof. Dr. Hoppe

CMOS Analog Design

213

Cascode stage – Design Procedure:

5. At last we need the bias voltage VGG2

•

First we need VDS1(sat) and use the vout(min)-spec to

obtain VDS2(sat)

VGG 2

2I

400µA

VDS 1 ( sat )

VTN 0.67V

K N '(W2 / L2 )

175µA / V 2 (4.3)