* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Slide 1

Spark-gap transmitter wikipedia , lookup

Power factor wikipedia , lookup

Chirp spectrum wikipedia , lookup

Electrical ballast wikipedia , lookup

Stray voltage wikipedia , lookup

Electrification wikipedia , lookup

Electric power system wikipedia , lookup

Control system wikipedia , lookup

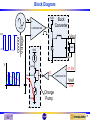

Resistive opto-isolator wikipedia , lookup

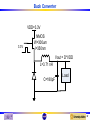

Three-phase electric power wikipedia , lookup

History of electric power transmission wikipedia , lookup

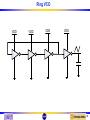

Electrical substation wikipedia , lookup

Power engineering wikipedia , lookup

Audio power wikipedia , lookup

Television standards conversion wikipedia , lookup

Opto-isolator wikipedia , lookup

Utility frequency wikipedia , lookup

Power inverter wikipedia , lookup

Voltage optimisation wikipedia , lookup

Integrating ADC wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Distribution management system wikipedia , lookup

Alternating current wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Mains electricity wikipedia , lookup

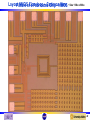

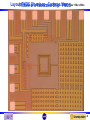

HVDC converter wikipedia , lookup

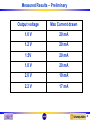

High Speed Fully Integrated On-Chip DC/DC Power Converter By Prabal Upadhyaya [email protected] Advisor Dr. Herbert Hess Sponsor: National Aeronautics and Space Administration (NASA) Microelectronics Research and Communications Institute (MRCI) University of Idaho February 8, 2007 1 Outline Overview Design of the High Speed DC/DC Power Converter Simulation Results Layout Measured Results Planned Future Work Conclusion 2 Overview Last 15 years has seen a significant reduction in size of portable electronics devices 3 Overview Portable system is a collection of various subsystems Sub-systems may demand multiple input voltages and variable currents 4 Overview On-chip fully integrated DC/DC power converters that provides point of use power conversion can be a possible solution Main power supply 3.3 Volts DC/DC Power Converter DC/DC Power Converter 1.2 V 15 mA 1.5 V 10 mA RF Tranceiver Analog Section 3.3 V 50 mA Digital Section 5 Overview All switch-mode power converters use inductor In the past, most DC/DC power converter were operated at low frequency and with discrete off chip inductor Quality factor (Q) of an inductor is the function of frequency Q L Q R f higher Q can be achieved at high frequency 6 Overview Benefits with high frequency switching Integrated solution for the power converter Reduced passive size Higher Q inductor available 7 Overview Challenges with high frequency design Parasitic capacitance Power dissipation Noise Attenuation 8 Design of the High Speed DC/DC Power Converter 9 Sub-Components Sub-components used in the power converter are • A Buck Converter • Two Comparators • A Voltage Control Oscillator (VCO) • A Charge Pump 10 Block Diagram VDD + VCO Control Voltage 3.3V 0V V COMPARATOR Buck Converter - Vout Load VDD Ipump 1 0 + <1.5V COMPARATOR - t Ipump Vref 1.5V Charge Pump 11 Buck Converter VDD=3.3V 3.3V NMOS W=300um l=350nm Vout = D*VDD L=3.71 nH C=180pF Load 12 Comparator Amplification stage Decision making Stage Buffer stage 13 Ring VCO VDD VDD VDD VDD 14 Charge Pump – Cadence View 15 Simulation Results Cadence Spectre 16 Simulation Results Output Voltage waveform has two kinds of output ripples •High frequency ripple due to switching at 1 GHz •Low frequency ripple due to control loop at 26 MHz Output Voltage = 1.5 V 17 Simulation Results •High frequency ripple is 19 mV •Low frequency ripple is 65mV Output waveform 18 Simulation Results • Vout changes with a change in the loading condition, but it takes less than 48 ns for the control loop to restore the output to the required voltage level Vout with variable load 19 Simulation Results •Comparator produces logic 1 and 0 depending upon the output of the buck converter Comparator Out 20 Simulation Results • Logic 1 or 0 from the comparator controls the operation of charge pump. •Logic 1 charges the capacitor •Logic 0 discharges the capacitor Charge Pump Out 21 Simulation Results •VCO produces a near triangular wave of 1.02 GHz VDD Rp Rn VCO Out V VDD * e CL t RC 22 Simulation Results •Duty-cycle of the PULSE driving the buck converter switch is altered based upon the near DC charge pump output voltage •Basic operation is to shift the DC level of the VCO signal to change the Dutycycle of the PULSE PWM 23 Simulation Results • Buck converter can supply upto 20mA of peak current. Iout 24 Simulation Results Vo=1.1 V Vo=1.3 V Vo=1.4 V Vo=1.5 V • Power converter has output range of 1.0 V to 1.8 V, but limited to loading conditions •Peak current of 20mA can be drawn only in the range of 1.0 V to 1.8 V •Output voltage range is limited by duty-cycle and comparator Vo=1.8 V 25 Simulation Results Vo=1.1 V Vo=1.3 V • Control loop created different duty cycles to adjust converter output Vo=1.5 V Vo=1.8 V PULSE with variable duty cycles 26 Power Converter Layout 27 Layout NMOSofCloseloop – Cadence View • Size 1180u x 900u Picture a Fabricated Chip - NMOS CONTROL CIRCUIT INDUCTOR CAPACITOR BANK 28 LayoutPicture PMOS of Closeloop– Cadence • Size 1180u x 900u a Fabricated Chip -View PMOS 29 Measured Results – Preliminary Output voltage Max Current drawn 1.0 V 20 mA 1.2 V 20 mA 1.5V 20 mA 1.8 V 20 mA 2.0 V 19 mA 2.2 V 17 mA 30 Planned Future Work Increase the switching frequency to achieve higher Q for inductor smaller passives Increase efficiency Eliminate low frequency ripple Use the concept over to manufacture power converters in the industrial basis 31 Planned Future Work – Control Ripple 32 Conclusion Fully integrated DC/DC converter realized in silicon The converter takes 3.3V supply and can successfully realize voltage from 1.0 V to 1.8 V while supplying up to 20 mA of current Diameter of the power converter is 1180u x 900u 33 High Speed Fully Integrated On-Chip DC/DC Power Converter Thank You! Acknowledgements I would like to express my deep gratitude to Mr. Parag Upadhyaya, Washington State University Dr. Deukhyoun Heo, Washington State University And MRCI team For technical discussion and support University of Idaho February 8, 2007 34