* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Basic CMOS OPAMPs

Survey

Document related concepts

Power inverter wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Integrating ADC wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Power MOSFET wikipedia , lookup

Stray voltage wikipedia , lookup

Current source wikipedia , lookup

Voltage optimisation wikipedia , lookup

Two-port network wikipedia , lookup

Voltage regulator wikipedia , lookup

Power electronics wikipedia , lookup

Alternating current wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Mains electricity wikipedia , lookup

Schmitt trigger wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Transcript

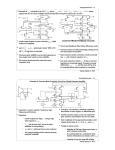

Basic CMOS OPAMPs Amplifiers Name Input Quan,ty Output Quan,ty Opera3onal Amplifier (OPAMP) Voltage Voltage Opera3onal Transconductance Amplifier (OTA) Voltage Current Opera3onal Current Amplifier (OCA) Current Current Current Mode Amplifier Current Voltage OPAMPs • An OPAMP is essen3ally a single pole amplifier. It exchanges gain for bandwidth. All other poles are beyond the GBW. • Mul3stage amplifiers have several poles and can work properly at one gain. They do not exchange gain for bandwidth. Two Stage Miller OPAMP VDD

Q8

Q5

Q7

Q1

Q2

Vout

Vin-

Vin+

Cc

Q3

Q4

+

I1

VSS

Q6

Two Stage Miller OPAMP • The gain can be wriJen simply as, (

A1 = −Gm1R1 = −gm1 r02 r04

(

)

A2 = −Gm 2 R2 = −gm 6 r06 r07

)

A = A1 A2

Rout = r06 r07

• The capacitances are, €

C1 = Cgd 2 + Cdb 2 + Cgd 4 + Cdb 4 + Cgs6

C2 = Cdb 6 + Cdb 7 + Cgd 7 + CL

€

Two Stage Miller OPAMP • From the previous discussion on frequency compensa3on, f p1 ≈

1

2πR1Gm 2 R2CC

fp2 ≈

Gm 2

2πC2

Gm 2

fz ≈

2πCC

• To achieve -‐20 dB/dec down to 0 dB, €

GBW = f t = A f p1 =

Gm1

2πCC

Two Stage Miller OPAMP • This frequency must be lower than fp2 and fz. Thus, G

G

m1

<

m2

CC

C2

Gm1 < Gm 2

• In prac3ce, C2 is typically equal to CL. C1 is a €

parasi3c capacitance and should be included into the calcula3ons as a correc3on. Gm1

Gm 2

1

GBW =

, f nd =

2πCC

2πCL 1+ Cn1

CC

Two Stage CMOS OPAMP • Assigning fnd as 3GBW and Cn1/CC as 0.3, we find a simple rule, Gm 2

CL

≈4

Gm1

CC

• This expression tells us to use larger current in the second stage. €

• Once CC is chosen, the design can be completed easily. Two Stage Miller OPAMP • The total phase at f=ft is simply φ total

⎛ f ⎞

⎛ ⎞

−1 f t

t

⎟⎟ + tan ⎜ ⎟

= 90° + tan ⎜⎜

⎝ f z ⎠

⎝ f p 2 ⎠

−1

• The phase of the zero is added, not subtracted €

because it is a posi3ve zero. ⎛ f ⎞

⎛ ⎞

−1 f t

t

⎟⎟ − tan ⎜ ⎟

PhaseM argin = 90° − tan ⎜⎜

⎝ f z ⎠

⎝ f p 2 ⎠

−1

€

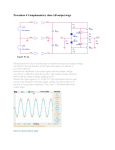

Two Stage Miller OPAMP • This zero is actually due to the feedforward through the capacitance. • The current passing through the capacitor cancels out the output current of the amplifier, causing a zero. • To get rid of this zero, we have to make the flow unidirec3onal; that is, cut the feedforward, but keep the feedback. Two Stage Miller OPAMP • There are several solu3ons by using source followers or cascodes, but they are complicated circuits. • The simplest solu3on is to use a resistance R in series with CC. • The func3onality of this resistor can be easily understood if we write the current through CC. Two Stage Miller OPAMP • Thus, Vi2

R+

1

sCC

= Gm 2Vi2

• The new loca3on of the zero is at s=

1

⎛ 1

⎞

CC ⎜

− R⎟

⎝ Gm 2

⎠

€

• By selec3ng R = 1/Gm2, the zero can be eliminated. €

• Even if complete matching cannot be achieved, the zero can be pushed to higher frequencies or converted to a nega3ve zero. Two Stage Miller OPAMP • However, too large a value should not be chosen either since the nega3ve zero is beneficial. Hence choose the zero to be less than 3GBW. • Thus, a range for R can be determined as, 1

1

<R<

Gm 2

3Gm1

€

Two Stage Miller OPAMP • Slew rate is generally due to the first stage and the compensa3on capacitance. • Slew rate is simply I/CC, where I is the tail current of the first stage. • Also, from these equa3ons, SR = VOVωt. Two Stage Miller OPAMP • Define a Figure of Merit (FOM) for our OPAMP designs as GBWxCL

FOM =

IBIAS

• This will be used to evaluate our designs. €

Two Stage Miller OPAMP • Let us try to design a two stage OPAMP with GBW of 400 MHz and CL = 5 pF. • We have two equa3ons rela3ng the three unknown variables, Gm1, Gm2, and CC. • If you start by choosing CC first, its minimum is about 3Cn1 and maximum is CL/{2-‐3}. • By adjus3ng CC, a minimum power point can be found. Two Stage Miller OPAMP 3.0E-‐05 2.5E-‐05 2.0E-‐05 I1 1.5E-‐05 I6 Itot 1.0E-‐05 5.0E-‐06 0.0E+00 0 1E-‐12 2E-‐12 3E-‐12 4E-‐12 5E-‐12 6E-‐12 Two Stage Miller OPAMP • This graph was drawn for GBW = 1MHz, CL = 10pF, Cn1 = 0.4pF, VGS – VT = 0.2V, and fnd = 3MHz. • You can play with these values in the excel chart to obtain your op3mum. • Note that Cn1 actually changes with the sizing of transistor M6. Thus, this graph is not exact. Two Stage Miller OPAMP • The second alterna3ve is to choose Gm2 first. The absolute minimum for this value is 3

(GBW)(2π)CL. • Now, choose a Gm2 which is 30% larger (corresponding to CC = 3Cn1). Then, the parasi3c Cn1 is determined right away. One can move from here to calculate other variables. • The third alterna3ve is to choose Gm1 first. This is useful to minimize noise. Two Stage Miller OPAMP • Concentrate the choices in coefficients: CL = αCC ,CC = βCn1 = βCGS 6 , f nd = γGBW

• Then, the GBW is given as €

€

gm 6

1

GBW =

2πCgs6 αβγ (1+1 β)

fT6 Two Stage Miller OPAMP •

•

•

•

Choose α,β,γ Calculate fT6 from GBW Calculate L6 for VGS – VT of 0.2V Calculate W6 from CL – Determine IDS6 – Determine Cn1 2 3 2 6.4 GHz 0.5 µm 417 µm 2.3 mA 0.83 pF • Calculate CC from CL and α 2.5 pF • Calculate gm1 and IDS1 0.63 mA Two Stage Miller OPAMP • The total current consump3on is 3.56 mA. • The FOM is 561 MHzpF/mA. • Remember fT in ac3ve region: µn

fT = 1.5

2 (VGS − VT )

2πL

• And fT in subthreshold region: €

€

1 It 1 1 ID

fT =

2π kT CD L2 IM

q

Two Stage Miller OPAMP • For smaller GBW values, the transistors can be biased in weak inversion or in the boundary. • Rewri3ng the above equa3ons by using the inversion coefficient technique, fT

= i 1 − e − i ≈ i for small i fTH

2 µ kT q

fTH =

2

2πL

(

)

Two Stage Miller OPAMP • Let us now do a design for GBW = 1MHz and CL = 5pF. • The transistors are probably in weak inversion. • Thus, it may be a good idea to use the EKV equa3ons. Two Stage Miller OPAMP • Choose α, β, and γ • Calculate minimum fT6 • Choose a channel length, L6 2 3 2 16 MHz 0.5 µm • Calculate inversion coefficient • Calculate W6 from CL 0.008 417 µm • Calculate CC • Calculate gm1 and IDS1 2.5 pF 1.6 µA – Calculate fTH6

– Calculate IDST6 – Calculate IDS6 – Calculate Cn1 2 GHz 0.33 mA 2.7 µA 0.83 pF OPAMP Specifica3ons • Introductory analysis – DC currents and voltages on all nodes – Small signal parameters of all transistors • DC Analysis – CM input voltage range vs supply voltage – Output voltage range vs supply voltage – Maximum output current (sink and source) OPAMP Specifica3ons • AC and transient analysis – AC resistance and capacitance on all nodes – Gain vs frequency – GBW vs biasing current – SR vs load capacitance – Output voltage range vs frequency – SeJling 3me – Input impedance vs frequency – Output impedance vs frequency OPAMP Specifica3ons • Specifica3ons related to offset and noise – Offset voltage vs CM input voltage – CMRR vs frequency – Input bias current and offset – Equivalent input noise voltage vs frequency – Equivalent input noise current vs frequency – Noise op3miza3on for capaci3ve/induc3ve sources – PSRR vs frequency – Distor3on OPAMP Specifica3ons • Other second order effects – Stability for induc3ve loads – Switching the biasing transistors – Switching or ramping the supply voltages – Different supply voltages, temperatures, … Common Mode Input Voltage Range • The maximum input voltage is VDD – VGS1 – VDS7 • The minimum input voltage is VSS + VGS3 + VDS1 – VGS1 • We can go closer to the nega3ve supply voltage. • The opposite is true for an NMOS input circuit. Output Voltage Range • If no resis3ve loads are present, the output can go rail to rail. • Otherwise, there is a resis3ve divider between the load and the output resistors. Slew Rate Revisited • The worst slewing condi3on occurs when an ideal square wave is applied to the OPAMP. • The square wave is converted to a triangular wave with VOUT,max = SR/4fmax. • As discussed above SR

4 πIDS1

=

GBW

gm1

IDS1 VGS1 − VT

=

gm1

2

IDS1 nkT

=

gm1

q

ICE1 kT

=

gm1

q

Strong inversion Weak inversion BJT Slew Rate • Actually, there are two types of slew rate, external and internal. IB

SRint =

CC

I

SRext = DS 7

CL

• SR is also related to seJling 3me. €

VOUT

7

t tot = t slew + t 0.1 =

+

SR 2πBW

ln(1000) ≈ 7

Output Impedance • In the open-‐loop configura3on, the output impedance is Rout = r06 r07

• However, this impedance starts dropping at the dominant pole and drops un3l R = 1 g

€

• At fnd, there is a second pole with CL. • Thus, the output impedance is not as large as €

expected. • Furthermore, the OPAMP is typically used with feedback. out

m6

Noise Behavior • The first stage is the dominant noise source all the way to GBW. • It is enough to calculate this noise. • The noise density is given by 2

v iN

= 4kT

4 3

Δf

gm

• Using the concept of noise bandwidth, the integrated noise is given by 4kT

3CC

€

€

A Few Comments on the Input Stage • Choose p-‐channel over n-‐channel for input differen3al amplifier due to – Lower noise – BeJer slew rate – BeJer GBW • Noise op3miza3on can be performed on the first stage by changing the NMOS mirror dimensions as well. Telescopic Cascode Amplifier Q9

VDD

VBIAS1

Q1

Q2

VIN+

Q5

Q6

Q7

Q8

VBIAS2

VBIAS3

Q3

Q4

VIN-

Telescopic Cascode Amplifier • Provides more gain at low frequencies. • GBW does not change. gm1

GBW =

2πCL

• You can actually use gain boos3ng to the €

cascodes to increase the gain further. However, the GBW will not change. Telescopic Cascode Amplifier • This is a single stage amplifier. No major issues about stability. • The output and input swings are quite small. • This circuit is more an OTA than an OPAMP due to its high output resistance. • High output resistance is not a big problem when driving capaci3ve loads. Telescopic Cascode Amplifier • The maximum output swing for a standard configura3on is given by [

(

Vswing = 2 VDD − 2Vov,n + 2Vov, p + Vcs

)]

• For our case, it is increased slightly. €

• The input swing is also limited. Telescopic Cascode Amplifier • Another very important limita3on related to the above is the voltage mismatch between input and outputs. Imagine unity gain F/B between gate of M2 and drain of M6. • For the new circuit, both transistors have to remain in ac3ve region. Thus, VBIAS3 must be chosen very carefully. Also, the swing is very limited. Folded Cascode OTA VDD

Q5

Q6

Q7

Q8

Q9

VBIAS4

Q1

Q2

VINVBIAS1

VIN+

Q3

Q10

VBIAS3

VBIAS2

Q4

Q11

VOUT

Folded Cascode OTA • This circuit is symmetrical since M1 and M2 see the same impedance. • The output is the only high resistance point; thus no compensa3on is necessary. • The input is again high-‐swing. • The output swing is slightly higher (by one current source voltage) than the telescopic cascode. Folded Cascode OTA -‐ DC • Choose bias current through M9 as 100 µA as an example. • M1 and M2 each conduct 50 µA. • Choose the currents through M10 and M11 as 100 µA. Then, the rest of the transistors will conduct 50 µA. • It is not a necessity to equate the currents through M9 and M10-‐11. However, good choice for symmetry. Folded Cascode OTA • The power consump3on is thus twice the telescopic OTA. • The Gain and GBW expressions are exactly the same. • Why bother with the folded cascode rather than the telescopic cascode? Same performance at twice the power? Folded Cascode OTA • The first non-‐dominant pole comes from the drains of M1 and M2. They form together one single non-‐dominant pole at approximately fT3/3. • The other non-‐dominant poles arising from M5-‐M6-‐M7-‐M8 are followed immediately by zeros and are not discernible. • Hence, this OTA has only one important non-‐

dominant pole and is quite easy to design. Folded Cascode OTA •

•

•

•

Choose Vov1,2 as 0.2V and Vov10,11 as 0.5V. Then, inputs can go all the way down to VSS. Hence, high input swing can be achieved. Input and output voltage levels can easily be matched. A Small Comparison • GBW = 100MHz, CL = 2pF, VGS – VT = 0.2V. Type ITOT Swing 2-‐stage Miller 1.1 large Telescopic 0.25 small Folded Cascode 0.5 average Symmetrical CMOS OTA VDD

Q7

Q9

Q8

VBIAS

Q1

Q2

Vout

Q5

Q3

B

:

1

Q4

Q6

1

:

B

Symmetrical CMOS OTA • Although this has 3 current mirrors as opposed to only one in a simple single stage amplifier, the performance is in essence the same. • However, this amplifier is the best you can achieve in terms of symmetry. • Furthermore, B can be used to obtain more gain. Symmetrical CMOS OTA • The gain is now gm1RoutB. • The BW is again given by BW =

• Thus, GBW is €

1

2πRout CL

GBW = B

gm1

2πCL

• How large c€an we make B? Symmetrical CMOS OTA • The two nodes drain of M1 and drain of M2 cause a single pole. The capacitance at this node is given by C = (1+ B)Cgs4 + Cdb 4 + Cdb 2 ≈ ( 3 + B)Cgs4

f nd =

gm 4

f

≈ T4

2πC 3 + B

• The pole at the drains of M5 and M7 is closely followed by a zero and can be ignored. €

• Thus, the maximum of B can be found by equa3ng fnd to 3GBW. It is typically 3…5. Symmetrical CMOS OTA • A symmetrical OTA can be built easily with cascodes as well. • This will increase gain at low frequencies, but not the GBW. Fully Differen3al Amplifiers VDD

Q5

VBIAS1

Q1

Q2

VIN-

VOUT+

VIN+

VBIAS2

Q3

Q4

VOUT-

Fully Differen3al Amplifiers • We can use this amplifier for differen3al opera3on which is desired in most applica3ons. • However, very good control of biasing voltages is necessary which is typically not possible. • Therefore Common Mode Feedback (CMFB) should be used. Fully Differen3al Amplifiers • A CMFB circuit senses the common mode level in the two outputs. Then, it feeds back a signal related to this to the tail current. • A typical sensing circuitry can be two resistors taking the average of the two outputs. • However, the resistors will load the circuit. You may use source followers to isolate the CMFB circuit. • Then, the CMFB signal can be compared against a reference and be fed back to the tail. Fully Differen3al Amplifiers • Fully differen3al amplifiers are almost always used in prac3ce. CMFB is also very commonly used. • The Miller OPAMP or cascode or folded cascode amplifiers can all be made differen3al. • CMFB will be discussed later.