* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download FINAL00sp

Mains electricity wikipedia , lookup

Loudspeaker wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Current source wikipedia , lookup

Control system wikipedia , lookup

Signal-flow graph wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Scattering parameters wikipedia , lookup

Buck converter wikipedia , lookup

Three-phase electric power wikipedia , lookup

Utility frequency wikipedia , lookup

Chirp spectrum wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Nominal impedance wikipedia , lookup

Schmitt trigger wikipedia , lookup

Negative feedback wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Two-port network wikipedia , lookup

Opto-isolator wikipedia , lookup

Zobel network wikipedia , lookup

Phase-locked loop wikipedia , lookup

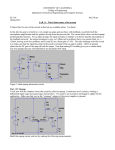

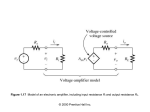

EECS 140 NAME and SID FINAL EXAM Spring 00 Note: Use the device parameters given in the class handout “Device Parameters & SPICE Models”. 1) (15pts) You have an opamp with a low frequency gain of 1000 and a pole at 10MHz and another pole at 100MHz. a) What is u? b) Draw a Bode plot of the open loop response. c) What is the phase margin (accurate to within a few degrees)? d) To get a phase margin of 45 degrees, what is the largest feedback factor that can be used, and the corresponding gain? e) What are the closed loop pole locations if f=1? f=0.01? Page 1 of 4 I0 Vref + - M2 Vi M1 2) (20pts) In the gain-boosting circuit above, assume that the opamp has infinite input impedance, zero output impedance, and a constant gain of A. It’s job is to try to keep the source of M2 at a constant voltage of Vref. Assume that both MOSFETs remain in saturation. Assume that the current source load has the same output impedance as the gain-boosted circuit that you are analyzing. a) Draw the low frequency small signal model of the circuit (replacing the opamp with the expression Vo=A(V+-V-) ) b) What is the low frequency impedance seen at the drain of M2? c) What is the gain of this circuit from Vi to the drain of M2, assuming an ideal current source load? d) What is the low frequency impedance seen at the source of M2? For the following parts of the problem, assume that you want as large an output swing as possible, so you would like to bias the drain of M1 at just a little bit above Vdsat1. The goal below is to pick the topologies for the opamp above that will work, and explain why some won’t. Hint: consider the common mode input range and output swing of the OTAs. e) Why can’t I use a simple NMOS input 5 transistor OTA to implement the opamp? f) Why can’t I use a simple PMOS input 5 transistor OTA to implement the opamp? g) Which of the following would work to implement the opamp? (circle the numbers of those that would work) i) NMOS input folded cascode ii) PMOS input folded cascode iii) NMOS input 2 stage Miller compensated iv) PMOS input 2 stage Miller compensated v) NMOS input telescopic cascode vi) PMOS input telescopic cascode Page 2 of 4 3) (40pts) Design a two-stage Miller-compensated CMOS opamp to be used in a unity gain feedback system with the following specifications: The output load consists of a 10k resistance in parallel with a 10pF capacitance. The phase margin should be 45 degrees. The 3dB frequency of the closed loop amplifier should be 100MHz. The low frequency gain should be accurate to 0.1% The negative supply is –2.5V, the positive supply is nominally 2.5V but may vary to 3.5V. Power consumption of the amplifier must not change by more than 10% over the range of supply voltages. You may use only one resistor in your circuit (presumeably in the bias circuitry). Other than that you may only use MOSFETs and capacitors. No ideal elements. a) Draw a rough schematic with transistor labels but without bias circuitry b) Calculate the required gain, unity gain frequency, and pole locations of the open loop amplifier c) Calculate gm, ro, Id, low frequency gain, and pole frequency for the first and second stages d) Draw the open loop bode plot of the uncompensated amplifier and calculate the phase margin e) Calculate the required compensation capacitor necessary to meet the phase margin specification, and calculate the corresponding zero frequency (you may assume that the zero will ultimately not affect the phase). f) Calculate the resistance value necessary to move the zero to infinity. g) Calculate the new pole locations assuming the compensation above, and draw the open loop Bode plot of the compensated amplifier h) Design a supply independent bias circuit to generate the necessary bias voltages and/or currents in your amplifier. i) Draw a final schematic with all of the transistors, W/L ratios, Vdsat, Id, and node bias voltages labeled. Page 3 of 4 Vdd Vdd 4) (25 points) M4a M4b M2a M2b M3a VBN M1a M3b M5a VBN M1b M5b M2a M2b M9 M9 M1a M1b Vref + - Vdd M2 M4a VBN M3a VBN M3b VBN M2a M5a M5b M1a M9 Page 4 of 4 M1