* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Lab 13

Induction motor wikipedia , lookup

Voltage optimisation wikipedia , lookup

Thermal runaway wikipedia , lookup

Commutator (electric) wikipedia , lookup

Electrical substation wikipedia , lookup

Electrification wikipedia , lookup

Skin effect wikipedia , lookup

Brushed DC electric motor wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Stepper motor wikipedia , lookup

Mains electricity wikipedia , lookup

Power engineering wikipedia , lookup

Electrical ballast wikipedia , lookup

History of electric power transmission wikipedia , lookup

Stray voltage wikipedia , lookup

Galvanometer wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Power electronics wikipedia , lookup

Earthing system wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Two-port network wikipedia , lookup

Opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

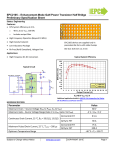

Alternating current wikipedia , lookup

Project 13 FET Current Sources Objective: The design of a constant current (independent current source) based on FET operation will be the basis of this project. Limitations on the operation will also be presented. Components: 2N7000 FET (enhancement) (4) Introduction: The independent current source is one of the basic building blocks in circuit design. This project will focus on the operation of two types of FET based current sources as shown in Figures 13-1 and 13-2. These circuits are designed so the current through the "load" is not dependent on the load but rather on the gate-tosource voltages associated with the reference and load branch FETs. The reference branch gate-to-source voltages are a function of the total supplied voltage, the FET parameters and the channel width to channel length (W/L) ratios for the two reference branch FETs, independent of the load being driven. These current sources are generally referred to as Current Mirrors since the current in the load branch effectively mirrors the reference current. The load currents as shown in Figure 13-1 are approximately equal to the reference current when all four FETs are identical while the load current in Figure 13-2 is a fraction of the reference current. The transistors are assumed to be matched so variations in the threshold voltage (VT), saturation region coefficient (K), and W/L ratios can generally be ignored in the analysis and design of the current mirrors. The two transistors in the reference branch are connected so the gate-to-source (VGS) and drain-to-source (VDS) voltages are equal. The two FETs are therefore operating in the saturation region since VDS > VGS VT (remember that VT > 0 for these FETs and VDS = VGS for this configuration). For identical FET devices VGS1 = VGS2 = - VSS/2 since, by KCL, ID1 = ID2 = K (W/L) (VGS - VT)2. It is interesting to note that the ratio of these two gate-to-source voltages can easily be changed at the time of fabrication by simply changing the channel width of one of the FET devices thereby changing the W/L ratios. The FET in each of the two load branches in Figure 13-1 has the same gate-to-source voltage as M2 and therefore have the same current as the reference branch since all four FET devices are assumed to be identical. The reference current is therefore mirrored through each load. The load current can be determined as indicated below: The reference gate-to-source voltages in Figure 13-2 are determined using the same procedure as for Figure 13-1. The load current however, is not equal to the reference current since VGS3 < VGS2 by Iload RS. It should be noted that the W/L ratios would be changed rather then including an RS if this current mirror were actually being integrated. A brief explanation of the reasoning behind the decision not to integrate a resistor can be found in the introduction for Project 11. The load current for Figure 13-2 an be determined using the following two equations: Again, the assumption of effectively identical FETs is employed. The value of RS can then be determined for specific values of load current. Parallel load branches can be added in a manner similar to that shown in Figure 13-1 with each load current being different. Notice that the load current(s) for the current mirror shown in Figure 13-2 is (are) always less than the reference current. Design: 1. Verify the operation of the current mirrors shown in Figures 13-1 and 13-2 with PSPICE®. You may represent the load as a positive voltage source in series with a variable resistor connected between ground and the load branch of the current source. 2. Design a current mirror based on the circuit in Figure 13-1 that will supply 10 mA to a load using the "nominal" specification sheet values of VT and K for each FET if the pre-lab was not completed during Lab 12. Determine any limitations on the load (represented as a resistor in series with a 10 V DC source). Discuss the reason for any limitations. 3. Design a current source illustrated in Figure 13-2 to supply 1 mA AND 10mA if RS is bypassed. You should again specify a VSS to achieve the desired currents. You should specify any limitations on your design. Figure 13 - 1: FET Current Mirror Figure 13 - 2: FET Current Mirror with Source resistance Lab Procedure: 1. Construct the current mirror designed in step 2 of the design procedures. Connect the resistance decade current (Y1 axis) and drain-source voltage (VDS) for M3 (Y2 axis) versus the load resistance (X axis). Discuss the results of the graphs in terms of circuit operation, limitations, and linearity. Comment on the ability to use this current mirror as an independent current source. 2. Repeat st Comment on any similarities/differences in the results from the two circuits. 3. Construct the current source designed in step 3 of the design section. Connect the resistance decade box (Y1 axis) and drain-source voltage (VDS) for M3 (Y2 axis) versus the load resistance (X axis). Discuss the results of the graphs in terms of circuit operation, limitations, and linearity. Comment on the ability to use this current mirror as an independent current source. -2 current mirror. Set the decade box resistance to the value of RS from step 3 of the design section. Vary the decade box resistance as appropriate to verify that the maximum current through the resistive load can increase to 10 mA. Plot the results; Iload on the Y1 axis and VDS3 on the Y2 axis versus the decade box resistance. Are the graphs as predicted by the design equations? Comment on the similarities/differences between the theoretical and experimental results. Questions: 1. Discuss some of the limitations placed on the number of parallel branches that can be added. Is there a limit since the gates effectively do not draw any current? 2. In the current source illustrated in Figure 13-2, can you assume the load FET is always saturated? Explain your answer. 3. The loads for these experiments were illustrated using resistances. What other devices/circuits/systems would be valid loads? What ones would not make valid loads? Discuss the justification for your answers. 4. How would you determine the "resistance" of each of the two current mirrors (single load branch with and without RS) as seen by the load? Would a high or low source (current mirror) be most beneficial? Explain your answer. 5. Discuss some of the limitations placed on the load and load source for proper current source operation. Are there limits on the load resistance if the load source is + 15 V? Explain your answers.