* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Lecture 3

Survey

Document related concepts

Switched-mode power supply wikipedia , lookup

Flexible electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Negative feedback wikipedia , lookup

Control system wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Power inverter wikipedia , lookup

Integrated circuit wikipedia , lookup

Schmitt trigger wikipedia , lookup

Opto-isolator wikipedia , lookup

Phase-locked loop wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Transcript

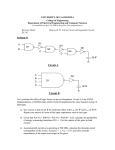

Class 03 Dynamic Logic Circuits Pass transistors circuits Synchronous dynamic circuit techniques Dynamic CMOS circuit techniques High-performance dynamic CMOS circuits 2 Register Stores a value as controlled by clock. May have load signal, etc. In CMOS, memory is created by: capacitance (dynamic); feedback (static). Variations in registers Form of required clock signal. How behavior of data input around clock affects the stored value. When the stored value is presented to the output. Whether there is ever a combinational path from input to output. Register terminology Latch: transparent when internal memory is being set from input. Flip-flop: not transparent—reading input and changing output are separate events. Clock terminology Clock edge: rising or falling transition. Duty cycle: fraction of clock period for which clock is active (e.g., for active-low clock, fraction of time clock is 0). Registerd parameters Setup time: time before clock during which data input must be stable. Hold time: time after clock event for which data input must remain stable. clock data Dynamic latch Stores charge on inverter gate capacitance: Latch characteristics Uses complementary transmission gate to ensure that storage node is always strongly driven. Latch is transparent when transmission gate is closed. Storage capacitance comes primarily from inverter gate capacitance. Latch operation = 0: transmission gate is off, inverter output is determined by storage node. = 1: transmission gate is on, inverter output follows D input. Setup and hold times determined by transmission gate—must ensure that value stored on transmission gate is solid. Non-dynamic latches Must use feedback to restore value. Some latches are static on one phase (pseudo-static)— load on one phase, activate feedback on other phase. Static v.s. Dynamic Static Logic Gates Valid logic levels are steady-state operating points Outputs are generated in response to input voltage levels after a certain time delay, and it can preserve its output levels as long as there is power. All gate output nodes have a conducting path to VDD or GND, except when input changes are occurring. Dynamic Logic Gates The operation depends on temporary storage of charge in parasitic node capacitances. The stored charge does not remain indefinitely, so must be updated or refreshed. This requires establishment of an update or recharge path to the capacitance frequently enough to preserve valid voltage levels. 12 Static v.s. Dynamic (Continued) Advantages of Dynamic Logic Gates Allow implementation of simple sequential circuits with memory functions. Use of common clock signals throughout the system enables the synchronization of various circuit blocks. Implementation of complex circuits requires a smaller silicon area than static circuits. Often consumes less dynamic power than static designs, due to smaller parasitic capacitances. 13 Latch versus Register Latch stores data when clock is low Register stores data when clock rises D Q D Q Clk Clk Clk Clk D D Q Q 14 static or dynamic Regs Registers can be static or dynamic. A static register holds state as long as the power supply is turned on It is ideal for memory that is accessed infrequently (e.g., reconfiguration registers or control information) Dynamic memory is based on temporary charge store on capacitors The primary advantage is the reduced complexity and higher performance/lower power. static and dynamic Regs However, charge on a dynamic node leaks away with time, and hence dynamic circuits have a minimum clock frequency. several fundamentally different approaches towards building a register. The most common and widely used approach is the master-slave configuration which involves cascading a positive latch and negative latch (or vice-versa). static and dynamic Regs Storage in a static sequential circuit relies on the concept that a cross-coupled inverter pair produces a bistable element and can thus be used to memorize binary values. This approach has the useful property that a stored value remains valid as long as the supply voltage is applied to the circuit, hence the name static. The major disadvantage of the static gate, however, is its complexity static and dynamic Regs When registers are used in computational structures, that are constantly clocked such as pipelined datapath, the requirement that the memory should hold state for extended periods of time can be significantly relaxed. This results in a class of circuits based on temporary storage of charge on parasitic capacitors. The principle is exactly identical to the one used in dynamic logic static and dynamic Regs Charge stored on a capacitor can be used to represent a logic signal. The absence of charge denotes a 0, while its presence stands for a stored 1. No capacitor is ideal, unfortunately, and some charge leakage is always present. A stored value can hence only be kept for a limited amount of time, typically in the range of milliseconds. If one wants to preserve signal integrity, a periodic refresh of its value is necessary. Hence the name dynamic storage. static and dynamic Regs Reading the value of the stored signal from a capacitor without disrupting the charge requires the availability of a device with a high input impedance. Latches vs. Registers A latch is an essential component in the construction of an edge-triggered register. It is level-sensitive circuit that passes the D input to the Q output when the clock signal is high. This latch is said to be in transparent mode. When the clock is low, the input data sampled on the falling edge of the clock is held stable at the output for the entire phase, and the latch is in hold mode. The inputs must be stable for a short period around the falling edge of the clock to meet set-up and hold requirements Latches vs. Registers A latch operating under the above conditions is a positive latch. Similarly, a negative latch passes the D input to the Q output when the clock signal is low. A wide variety of static and dynamic implementations exists for the realization of latches. Contrary to level-sensitive latches, edge-triggered registers only sample the input on a clock transition — 0-to-1 for a positive edge-triggered register, and 1-to-0 for a negative edge-triggered register Stored charge leakage Stored charge leaks away due to reverse-bias leakage current. Stored value is good for about 1 ms. Value must be rewritten to be valid. If not loaded every cycle, must ensure that latch is loaded often enough to keep data valid. 3-transistor dynamic RAM (DRAM) First form of DRAM—modern commercial DRAMs use one-transistor cell. 3-transistor cell can easily be made with a digital process. Dynamic RAM loses value due to charge leakage— must be refreshed. Memory operation Address is divided into row, column. Row may contain full word or more than one word. Selected row drives/senses bit lines in columns. Amplifiers/drivers read/write bit lines. Read-only memory (ROM) ROM core is organized as NOR gates—pulldown transistors of NOR determine programming. Mask-programmable ROM uses pulldowns to determine ROM contents. Flash memory Flash: electrically erasable PROM that can be programmed with standard voltages. Uses dual capacitor structure. Available in some digital processes for integrated memory, but raises the price of the manufacturing process. Static versus Dynamic Memory Memories can be static or dynamic. Static memories preserve the state as long as the power is turned on. Static memories are built using positive feedback or regeneration, where the circuit topology consists of intentional connections between the output and the input of a combinational circuit. Static memories are most useful when the register won’t be updated for extended periods of time. An example of such is configuration data, loaded at power-up time. This condition also holds for most processors that use conditional clocking Static versus Dynamic Memory where the clock is turned off for unused modules. In that case, there are no guarantees on how frequently the registers will be clocked, and static memories are needed to preserve the state information. Memory based on positive feedback fall under the class of elements called multivibrator circuits. The bistable element, is its most popular representative, but other elements such as monostable and astable circuits are also frequently used. Static versus Dynamic Memory Dynamic memories store state for a short period of time— on the order of milliseconds. They are based on the principle of temporary charge storage on parasitic capacitors associated with MOS devices. Capacitors have to be refreshed periodically to annihilate charge leakage. Dynamic memories tend to simpler, resulting in significantly higher performance and lower power dissipation. They are most useful in datapath circuits that require high performance levels and are periodically clocked. Static versus Dynamic Memory It is possible to use dynamic circuitry even when circuits are conditionally clocked, if the state can be discarded when a module goes into idle mode. Sequential CMOS and NMOS Logic Circuits Sequential logic circuits contain one or more combinational logic blocks along with memory in a feedback loop with the logic The next state of the machine depends on the present state and the inputs The output depends on the present state of the machine and perhaps also on the inputs Mealy machine: output depends only on the state of the machine Moore machine: the output depends on both the present state and the inputs Logic Circuit Classification: Sequential Circuit Types Sequential circuits (also called regenerative circuits) fall into three types: Bistable Monostable Astable Bistable circuits have two stable operating points and will remain in either state unless perturbed to the opposite state Memory cells, latches, flip-flops, and registers Monostable circuits have only one stable operating point, and even if they are temporarily perturbed to the opposite state, they will return in time to their stable operating point Astable circuits have no stable operating point and oscillate between several states Ring oscillator Writing into a Static Latch Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states CLK CLK Q CLK D D CLK D CLK Converting into a MUX Forcing the state (can implement as NMOS-only) 34 Storage Mechanisms Dynamic (charge-based) Static CLK CLK Q D Q CLK CLK D CLK 35 CMOS SR Latch: NOR Gate Version The NOR-based SR Latch contains the basic memory cell (back-to-back inverters) built into two NOR gates to allow setting the state of the latch. If Set goes high, M1 is turned on forcing Q’ low which, in turn, pulls Q high S=1 Q = 1 If Reset goes high, M4 is turned on, Q is pulled low, and Q’ is then pulled high R=1 Q’ = 1 If both Set and Reset are low, both M1 and M4 are off, and the latch holds its existing state indefinitely If both Set and Reset go high, both Q and Q’ are pulled low, giving an indefinite state. Therefore, R=S=1 is not allowed The gate-level symbol and truth table for the NOR-based SR latch are given at left To estimate Set time, add time to discharge Q’ + time to charge Q (pessimistic result) CMOS SR Latch: NAND Gate Version A CMOS SR latch built with two 2-input NAND gates is shown at left The basic memory cell comprised of two back-to-back CMOS inverters is seen The circuit responds to active low S and R inputs If S goes to 0 (while R = 1), Q goes high, pulling Q’ low and the latch enters Set state S=0 Q = 1 (if R = 1) If R goes to 0 (while S = 1), Q’ goes high, pulling Q low and the latch is Reset R=0 Q’ = 1 (if S = 1) Hold state requires both S and R to be high S = R = 0 if not allowed, as it would result in an indeterminate state Clocked SR Latch: NOR Version Shown at left is the NOR-based SR latch with a clock added. The latch is responsive to inputs S and R only when CLK is high When CLK is low, the latch retains its current state Timing diagram shows the level-sensitive nature of the clocked SR latch. Note four times where Q changes state: When S goes high during positive CLK On leading CLK edge after changes in S & R during CLK low time A positive glitch in S while CLK is high When R goes high during positive CLK Clocked CMOS SR Latch: Implementation CMOS implementation of clocked NOR-based SR latch shown at left with logic symbol circuit below Only 12 transistors required When CLK is low, two series legs in N tree are open and two parallel transistors in P tree are ON, thus retaining state in the memory cell When CLK is high, the circuit becomes simply a NOR-based CMOS latch which will respond to inputs S and R Clocked CMOS JK Latch: NAND Version The SR latch has a problem in that when both S and R are high, its state becomes indeterminate The JK latch shown at left eliminates this problem by using feedback from output to input, such all states in the truth table are allowable If J = K = 0, the latch will hold its present state If J = 1 and K = 0, the latch will set on the next positive-going clock edge, i.e. Q = 1, Q’ = 0 If J = 0 and K = 1, the latch will reset on the next positive-going clock edge, i.e. Q’ = 1 and Q =0 If J = K = 1, the latch will toggle on the next positive-going clock edge Note that in order to prevent the JK Latch above from oscillating continuously during the clock active time, the clock width must be kept smaller than the switching delay time of the latch. Otherwise, several oscillations may occur before the clock goes low again. In practice this may be difficult to achieve. JK Master-Slave Flip-Flop A Flip-Flop is defined as two latches connected serially and activated with opposite phase clocks First latch is the Master; Second latch is the Slave Eliminates transparency, i.e. a change occurring in the primary inputs is never reflected directly to the outputs, since opposite phase clocks are used to activate the M and S latches. A JK master-slave flip-flop (NOR-based version) is shown below: The feedback paths occur from Q and Q’ slave outputs to the master inputs gates does not exhibit any tendency to oscillate when J = K = 1 no matter how long the clock period, since opposite clock phases activate the master and slave latches separately. The NOR-based version can be done with four CMOS gates, requiring 28 transistors Can be susceptible to “ones catching”, i.e. a positive glitch in either the J or K input while the CLK is high, which can change the state of the master latch (and the slave latch on next edge) CMOS D-Latch Implementation A D-latch is implemented, at the gate level, by simply utilizing a NOR-based S-R latch, connecting D to input S, and connecting D’ to input R with an inverter. When CLK goes high, D is transmitted to output Q (and D’ to Q’) When CLK goes low, the latch retains its previous state The D latch is normally implemented with transmission gate (TG) switches, as shown at the left The input TG is activated with CLK while the latch feedback loop TG is activated with CLK’ Input D is accepted when CLK is high When CLK goes low, the input is opencircuited and the latch is set with the prior data D CMOS D-Latch Schematic View and Timing A schematic view of the D-Latch can be obtained using simple switches in place of the TG’s When CLK = 1, the input switch is closed allowing new input data into the latch When CLK = 0, the input switch is opened and the feedback loop switch is closed, setting the latch Timing diagram: In order to guarantee adequate time to get correct data at the first inverter input before the input switch opens, the data must be valid for a given time (Tsetup) prior to the CLK going low. In order to guarantee adequate time to set the latch with correct data, the data must remain valid for a time (Thold) after the CLK goes low. Violations of Tsetup and Thold can cause metastability problems and chaotic transient behavior. Alternate CMOS D-Latch Implementation An alternate (preferred) version of the CMOS D-Latch (shown at left) is implemented with two tri-state inverters and a normal CMOS inverter. Functionally it is similar to the previous chart D-Latch When CLK is high, the first tri-state inverter sends the inverted input through to the second inverter, while the second tri-state is in its high Z state. Output Q is following input D When CLK is low, the first tri-state goes into its high Z state, while the second tri-state inverter closes the feedback loop, holding the data Q and Q’ in the latch. CMOS Static Latches with Single Phase Clock Various types of D latch circuit with single phase clocks (a) shows the use of a weak inverter to allow removal of feedback loop X-gate but retain static latch function (b) D latch ckt with input inverter buffer (c) implementation of (b) utilizing tristate buffer/inverter circuits with clocks at center of tri-state Alternate schematic of (c) indicating layout convenience due to common tie point at output of tri-state buffers Clock skew problems can be solved onchip by using buffering in clock nets Inverter buffers to generate neg clk Transmission gate buffers for true clk Construction of D Register (Flip-Flop) in CMOS Two level-sensitive latches are combined to form a positive edgetriggered register, as is used to build a D register (a) shows negative level sensitive latch (valid when clock is negative) (b) shows positive level sensitive latch (valid when clock is positive) (c) shows positive edge-triggered D register (also called a Flip-Flop) comprised of a negative latch feeding a positive latch First latch is the Master Second latch is the Slave D register timing: Output Q valid at Tq (clock-to-Q) delay after clock edge Data must be valid Ts (setup time) prior to clock edge and Th (hold time) after clock edge CMOS D Flip-Flop: Falling Edge-Triggered Shown below is a D Flip-Flop, constructed by cascading two D-Latch circuits from the previous chart Master latch is positive level sensitive (receives data when CLK is high) Slave latch is negative level sensitive (receives data Qm when CLK is low) The circuit is negative-edge triggered The master latch receives input D until the CLK falls from high to low, at which point it sets that data in the master latch and sends it through to the output Qs Latch Metastability Consider the problem of setting a latch when the data is late and/or has a very long rise/fall time and is still changing during the clock transition if data change is delayed and overlaps clock edge (below), latch may set with new data rather than valid prior data Data delay = 2.2 ns latch sets correctly at Q=1 Data delay = 2.3 ns latch hangs momentarily at metastable point, but then sets correctly at Q=1 Data delay = 2.4 ns latch hangs momentarily and sets incorrectly at Q=0 Metastable point: non stable point in a latch where Vleft = Vright (neither “0” or “1”) thermal noise will cause latch to move off metastable point and set at a “0” or a “1” How to fix? speedup the data (register-based synchronizer) delay the clock (introduce an intentional clock delay ---- risky!!) Clocked SR Latch: NAND Version NAND version of clocked SR latch with active high clock is shown Circuit is implemented with four NAND gates, not with an AOI or OAI 16 transistors required The latch is responsive to S or R only if CLK is high When CLK is low, the latch retains its present state Latch-Based Design • N latch is transparent when = 0 • P latch is transparent when = 1 N Latch Logic P Latch Logic 50 Timing Definitions CLK t tsu D D thold DATA STABLE Q CLK t tc 2 Q Register q DATA STABLE t 51 Bistability Principle Static memories use positive feedback to create a bistable circuit — a circuit having two stable states that represent 0 and 1. Memory Cell: Two-Inverter Basic Bistable Element A memory cell is comprised of two inverters connected back-to-back, i.e. output of one to input of the other and vice-versa. The memory cell (or latch) has two stable states where the dc voltage transfer curves cross at the VOH and VOL points, but also exhibits an unstable state where the VTC’s cross near their Vth switching points. In actual physical circuits the memory cell will never stay at the unstable point, since any small electrical noise in the circuit will trigger it to one side or the other In numerical simulation (the circuit may actually remain in the unstable state (assuming no noise source) The CMOS SRAM cell at the left will either be in state “0” with V01 at GND and V02 at VDD or in state “1” with V01 at VDD and V02 at GND. Positive Feedback: Bi-Stability Vi2 V o11 o V 1 o V 5 2 i V V i1 V o2 A V i 2 = V o11 o V 5 2 i V C B V i 1 = V o2 54 Meta-Stability Gain should be larger than 1 in the transition region 55