* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Homework #3

Power factor wikipedia , lookup

Three-phase electric power wikipedia , lookup

Wireless power transfer wikipedia , lookup

Standby power wikipedia , lookup

Electrical substation wikipedia , lookup

Stray voltage wikipedia , lookup

Electrification wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electric power system wikipedia , lookup

Opto-isolator wikipedia , lookup

Audio power wikipedia , lookup

History of electric power transmission wikipedia , lookup

Surge protector wikipedia , lookup

Distribution management system wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Power over Ethernet wikipedia , lookup

Power engineering wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Voltage optimisation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power MOSFET wikipedia , lookup

Alternating current wikipedia , lookup

Buck converter wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mains electricity wikipedia , lookup

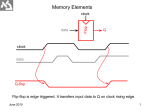

Flip-flop (electronics) wikipedia , lookup

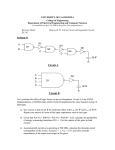

Homework #3 – Design of Latches, Race/Skew Issues 1. The gate below is called a “tri-state” inverter. It acts like an inverter when the Clk is HIGH, but when the Clk is LOW, the output is not explicitly driven. Clkb In Out Clk 8λ/2λ Clkb 8λ/2λ In Out Clk 4λ/2λ 4λ/2λ Notice that the sizes of the gates are ½ the size of minimum size inverter. Since this gate itself is used in the feedback loop of the latch/flip-flop, it’s drive strength does not need to be very large, and thus, will the smaller size, power is saved. 1a) Layout this device in Cadence. TURN in your group’s copy of this layout in Cadence, so I know that you actually did this design. 1b) From this device, we will now create a true Flip-Flop (Rising edge triggered). Clka Clkb Clkb Clka Clka Clk D OUT FO1 Clkb FO1 Clka Clk All FO1 Layout this device in Cadence, and turn it in. Notice that we will be measuring the delay: Clk -> Out. Note that there is some odd inverter buffering here—five inverter buffer delays, and the rising edge of Clka occurs three inverter delays after Clkb. This is to accentuate the issue of SETUP and HOLD time. Typically, there is only one-two inverters, and the rising edges of Clk and Clka are not so significantly “skewed”. Make the transmission gates minimum size—NMOS(4/2), PMOS(8/2), and its bulks tied to VDD/GND. 1c) Calculate in regards to buffer delays, the: 1. Setup Time – (how long D need needs to be stable before rising edge of Clk) 2. Hold Time – (How long D needs to be stable after rising edge of Clk) Do these simulations using the extracted parasitic HSPICE deck from the layout of the Flip-Flop. Measure the SETUP/HOLD times, for varying values of rise/fall time of Clk. i.e. vary rise/fall time of Clk = 50p, 100p, 500p, 1n Use the simulation deck ~pchiang/hspice/flipflop_*_sim_deck to help you simulate and sweep the rise and fall time across these varying conditions. 1d) Why do the SETUP/HOLD time vary for varying values of rise/fall time? 2. Leakage Power Since the project is focusing on designing digital integrated circuits with low power consumption, we have tried to understand the various ways to reduce power. (i.e. power supply reduction, bulk body bias, etc) We never measured the leakage power, the amount of power dissipated in gates when no gate is switching and power is consumed through current “leaking” from PMOS through to the output. 2a) Measure the leakage power of one FO4 inverter in 0.25um technology, assuming 2.5V supply voltage. This should be relatively simple—measure the current consumed through the voltage source “VDD”. 2b) Recalculate the leakage power of this FO4 inverter in 0.25um technology, but sweeping the supply voltage—2.5V, 1.8V, 1.2V, 1.0V, 0.8V. 2c) Redo part 2a) and 2b) for a 32nm FO4 device. Assume the nominal voltage for the 32nm device is 0.9V, 0.8V, 0.7V, 0.6V, 0.5V. 3. Clock Skews Consider the simple state machine shown above. A, B, and C represent combinational logic blocks with the following properties: tminA = 200 psec; tmaxA = 1 nsec; tminB = 300 psec; tmaxB = 2 nsec; tminC = 100 psec; tmaxC = 0.5 nsec; The L-units represent positive latches clocked by . L has a setup time of 150 psec and a delay of 250 psec (td-q when latch is transparent). Tc-q is 100 psec and thold is 100 psec. The clock has a period T and is high for a duration of Ton. The duty cycle of the clock hence equals 100 Ton/T %. a) Determine the conditions on the clock necessary to avoid the occurrence of races. b) Determine the absolute minimum clock period for this circuit to work correctly as well as the maximum duty cycle. c) Suppose that due to some sloppy clock-network routing, the clock signal at L1 arrives 100ps earlier than the clock signal at L2. Calculate the absolute minimum clock period for this circuit to work properly as well as the maximum duty cycle.