* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download High AC input voltage limiting circuit

Mercury-arc valve wikipedia , lookup

Stepper motor wikipedia , lookup

Ground (electricity) wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electrical ballast wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power engineering wikipedia , lookup

Power inverter wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Three-phase electric power wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Two-port network wikipedia , lookup

Current source wikipedia , lookup

Power electronics wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage regulator wikipedia , lookup

Stray voltage wikipedia , lookup

Surge protector wikipedia , lookup

Distribution management system wikipedia , lookup

Voltage optimisation wikipedia , lookup

Alternating current wikipedia , lookup

Current mirror wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mains electricity wikipedia , lookup

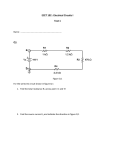

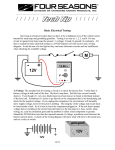

AN2625 Application note High AC input voltage limiting circuit Introduction The requirements on the switched mode power supply applications regarding the input AC voltage range are constantly increasing: for example, the ultra wide input voltage range of 90 to 440 VAC is now commonly required in many applications (electricity meters, lighting, factory automation). This inevitably leads to an increased working voltage levels and thus limited safe operation of the power supply components. This application note is describing one possible approach that can be used for safe operation of primary switchers with high input voltages. The circuit is aiming to limit (clamp) input AC voltages higher than 260 V to levels safe for the operation of ST off-line SMPS primary switchers (e.g. VIPer12A-E, VIPer22A-E, VIPer53A-E). It is presumed that the input AC voltage can reach 440 V maximum (line-toline voltage of a 3phase power net 230 / 400 V +10% tolerance). As the maximum breakdown voltage of the embedded VIPer MOSFET is between 620 - 730 V, there is no safe voltage margin if the switcher is operated at 440 VRMS input voltage. The circuit is based on using a MOSFET (N-channel 500 V, 2.7 Ω Power MOSFET, STP4NK50Z) working as a low frequency (100 Hz) switch and a comparator setting the clamped high voltage level. The comparator is built by using a combination of NPN transistor and a zener diode (Figure 1). The circuit is tested by supplying two different ST switchers demo board VIPer12A-E (AN 2103, Ref.2) and demo board VIPer22A-E (AN 1736, Ref.3), connected to the input bulk capacitors. Accordingly, a minimum changes were introduced to the original configuration of the demo boards by the connection of the clamping circuit. The circuit was also tested under simple resistive loads. The proposed circuit strives to achieve efficiency higher than 50% in the power range of 5 to 10 W at high input voltage (up to 440 VAC) and low input voltage 90 VAC. It is intended to be used as an input stage with VIPerX2, VIPer53A-E based SMPS in cases when "ultra-wide" ranges (90 VRMS to 440 VRMS) of input AC voltages are expected. January 2008 Rev 1 1/17 www.st.com Contents AN2625 Contents 1 2 Circuit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 1.1 Bill of material . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 1.2 Evaluation results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 1.2.1 Waveforms at steady-state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 1.2.2 Waveform at start-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 EMC evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 2.1 EMC results - VIPer12A-E demo board load, output power 6 W . . . . . . . 12 2.2 EMC testing - resistive load, output power 10 W . . . . . . . . . . . . . . . . . . . 14 3 Conclusions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 4 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 2/17 AN2625 List of figures List of figures Figure 1. Figure 2. Figure 3. Figure 4. Figure 5. Figure 6. Figure 7. Figure 8. Figure 9. Figure 10. Figure 11. Figure 12. Figure 13. Figure 14. Figure 15. Figure 16. Figure 17. High input AC voltage limiting circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Evaluation set-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Current and voltage waveforms at VIN = 440 VAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Current and voltage waveforms at VIN = 440 VAC with output voltage measurement . . . . . 8 Magnified view of Figure 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Maximum magnified view of Figure 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Voltages and currents at VIN = 90 VAC, Po = 6.4 W; no clamping - normal operation . . . . 10 Voltages and currents at VIN = 90 VAC, Po = 9.44 W; no clamping - normal operation . . . 10 Voltage and current waveforms at start-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Peak detection, LINE, VIPer12A-E demo board as load . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Average detection, LINE, VIPer12A-E demo board as load . . . . . . . . . . . . . . . . . . . . . . . . 12 Peak detection, NEUTRAL, VIPer12A-E demo board as load . . . . . . . . . . . . . . . . . . . . . . 13 Average detection, NEUTRAL, VIPer12A-E demo board as load . . . . . . . . . . . . . . . . . . . 13 Peak detection, LINE, resistive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Average detection, LINE, resistive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Peak detection, NEUTRAL, resistive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Average detection, NEUTRAL, resistive load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 3/17 Circuit description 1 AN2625 Circuit description The schematic of the circuit is shown in Figure 1. Figure 1. High input AC voltage limiting circuit 630 V max L1 L2 R1 1 mH 1 mH 30 Ω J1 220 nF /440 VAC 2 Line / Neutral VIN RMS = 90 - 440 V – + C D2 5.6 V R4 7. 5 kΩ 360 VDC R3 620 kΩ R2 620 kΩ D1 4X1N4007 C1 1 Line A Q1 2N3904 C2 D3 15 V + 4.7 µF / 400 V Q2 STP4NK50Z B AI14514 In steady state the MOSFET Q2 works as an 100 Hz operated switch interrupting the charge of C2 (the bulk capacitor at the input of the SMPS). Before the voltage at point C reaches the threshold level of 6.3 V the MOSFET Q2 is ON - Q1 is OFF sinking minimum Icbo current and the zener D3 breaks down to 15 V assuring stable ON state of Q2. This is also the normal operating condition for the MOSFET at input AC voltages ≤ 260 VRMS.(The AC level of the input voltage at which the 6.3 V level is reached, is chosen to be 360 V for this evaluation. Accordingly, 360 V is the level at which the input AC voltage is limited). The threshold level is set up by the zener voltage of D2 and B-E junction voltage of Q1. The negative temperature coefficient of the B-E junction partially cancels the breakdown zener diode's positive temperature coefficient (Vz > 5 V), thus achieving a temperature independence of the threshold level. As it can be seen from Figure 3 and Figure 4 (paragraph 1.2. Waveforms at steady state), the IDS current flows only for a fraction of the whole conduction ON time interval of Q2 - the current flows only when the voltage across C2 becomes less than the rectified input AC voltage allowing for the rectifying diodes of D1 bridge to be forward biased. Accordingly, C2 starts charging during that time. If there were not a switching circuitry (R2, R4, D2, Q1), the voltage across C2 would follow the input AC rectified waveform until the rectifying diodes of the D1 bridge were reverse biased. But the input AC voltage reaches the 360 V threshold level and the MOSFET Q2 is turned OFF - at voltage ≥ 6.3 V at point C, Q1 turns ON diverting and sinking the whole current from the zener D3, the Vgs of Q1 drops to zero and Q2 is switched OFF. The rectifying diodes of D1 bridge are still forward biased but they do not conduct current as the MOSFET Q2 is OFF. Accordingly, the voltage across C2 gets limited as there is no charging current flowing. The rectifying diodes of D1 bridge are forward biased up to the moment when the rectified input AC voltage starts to fall below the voltage across C2. Hence, a time interval follows when both the rectifying diodes and the MOSFET are OFF. At the moment when the rectified input AC voltage falls below the threshold level of 360 V (i.e. 6.3 V at point C), the 4/17 AN2625 Circuit description MOSFET is turned ON again but current does not flow as the rectifying diodes are still reverse biased. C2 discharges at a rate determined by the output power level. Eventually, the voltage across C2 decreases enough to forward bias the bridge D1 rectifying diodes and thus allowing short charging current pulses to flow and replenish the energy loss of C2 to the limited value. It can be seen from Figure 5 and Figure 6, the switching power dissipation of Q2 is very small - during every switching period the MOSFET is ON only for 450 µs. No temperature rise of Q2 is observed. Hence, the overall power loss of the circuit is determined by the passive components rather then by the switch Q2. The current thru the switch Q2 is sharply interrupted when the rectifying diodes are forward biased. As they are 50 Hz rectifying diodes, this current interruption causes the ringing observed on VDS (Figure 6). 1.1 Bill of material Table 1. 1.2 BOM for 360 V limited level Item Qty Ref. Description Manufacturer 1 2 L1, L2 1mH / 0.2 A choke General purpose component 2 1 C1 220 nF / 440 VAC General purpose component 3 4 D1 1N4007 General purpose component 4 1 Q1 2N3904 General purpose component 5 1 D2 5.6 V / 0.5 W Zener Diode General purpose component 6 1 D3 15 V / 0.5 W Zener Diode General purpose component 7 1 Q2 STP4NK50Z STMicroelectronics 8 1 C2 4.7 µF / 400 V General purpose component 9 1 R4 7.5 kΩ/ 0.25 W, 5% General purpose component 10 2 R2, R3 620 kΩ / 0.25 W, 5% General purpose component Evaluation results The circuit uses the component values shown on Figure 1 and Table 1. The clamped output voltage was set to 360 V. Under resistive loading, the following measurements were made, Table 2: Table 2. Measurements with resistive load(1) Resistive load VIN RMS (V) VCLAMPED DC (V) PO (W) PIN (W) Efficiency (%) 20 kΩ 440 350 6 7.3 82 13 kΩ 440 348 9.15 10.7 85 EN55022, Class B 260 285, Rload = 8 kΩ 10 — pass 1. Bulk capacitor, 10 µF / 400 V capacitor was used as C2 output capacitor. 5/17 Circuit description AN2625 Next, the circuit was loaded with non-linear loads, Figure 2. The following measurements were made, when the load of the clamping circuit is the VIPer12A-E SMPS, output power of 6.4 W (Table 3): Table 3. Measurements with VIPer12A-E reference design as load VIN RMS (V) IIN RMS (mA) PIN (W) VC3MAX (clamp level) (V) Total PO (W) Efficiency (%) 440 144 9.66 358 6.4 66 380 126 9.32 358 6.4 68 320 124 9.19 358 6.4 69 260 72 8.72 358 6.4 73 Above 260 VAC the limiting circuit is clamping the DC bus voltage of VIPer12A-E SMPS to 358 V max; 200 69 8.31 274 6.4 77 160 80 8.17 220 6.4 77 100 130 8.75 138 6.4 73 90 145 9.1 120 6.4 70 At 80 VAC the VIPer12A-E SMPS is loosing regulation. When the load of the clamping circuit is the VIPer22A-E SMPS, output power 10 W, the evaluation results are shown in Table 4: Table 4. Measurements with VIPer22A-E reference design as load VIN RMS (V) IIN RMS (mA) PIN (W) VC6MAX (clamp level) (V) Total PO (W) Efficiency (%) 440 195 15.6 354 9.6 61 380 192 15.45 354 9.6 62 320 182 15.14 354 9.6 63 260 98 14.22 354 9.6 67 Above 260 VAC the limiting circuit is clamping the DC bus voltage of VIPer22A-E SMPS to 354 V max; 200 104 13.25 268 9.6 72 160 118 12.72 216 9.6 75 100 168 13.95 132 9.6 68 90 211 14.4 110 9.6 66 At 80 VAC the VIPer22A-E SMPS is loosing regulation. At high line voltage 440 VAC the efficiency is decreased because of the combined energy losses in both the converter and clamping circuit. At low line voltage of 90 VAC, the efficiency is decreased because of the increased conduction loss in Q2 of the clamping circuit (Figure 7 and Figure 8). 6/17 1 Line 30 Ω R1 220 nF/ 440 Vac 1 mH 1 mH 2 Line / Neutral VIN RMS = 90 - 440 V J1 L2 L1 D1 4X1N4007 C1 – + C R5 7.5 kΩ Q1 2N3904 D2 5.6 V R2 620 kΩ 630 V max STP4NK50Z B C2 4.7 µF / D3 400 V 15V Q2 10 µ F / 400 V C4 + + 360 VDC R3 620 kΩ A 1 1 2 L4 4 30 mH 3 2 L3 4 45 mH 3 + + 22 µF/ 400 V C5 10 µF/ 400 V C3 AN1736: VIPer22A-E Demo board; 10 W, 5 V / 1.0 A, 12 V / 0.42 A output; Efficency: 75% specifications. TEST 2 (Table 4) AN2103: VIPer12A-E Demo board; 6 W, 12 V / 0.5 A output; Efficency: 75% specifications. +12 V / 0.42 A +5 V / 1.0 A +12 V / 0.5 A AI14515 R7 30 Ω R6 5Ω R4 22 Ω Figure 2. TEST 1 (Table 3) AN2625 Circuit description Evaluation set-up 7/17 Circuit description 1.2.1 AN2625 Waveforms at steady-state All measurements are referenced to the schematic shown on Figure 1. Figure 3. Current and voltage waveforms at VIN = 440 VAC Ch1. - the voltage after the rectifier bridge. Figure 4. Current and voltage waveforms at VIN = 440 VAC with output voltage measurement Ch1 - the voltage across C2. The other channels are measuring: - Ch.2 - gate-source voltage of Q2; Ch3 - drain-source voltage of Q2; Ch4. - the drain-source current peaks thru Q2. 8/17 AN2625 Circuit description Figure 5. Magnified view of Figure 4 Ch3. - drain-source voltage of Q2. Figure 6. Maximum magnified view of Figure 4 Ch.3.- drain-source voltage of Q2, note the ringing. The other channels are measuring: - Ch.2 - gate-source voltage of Q2; Ch.1 - VC2 voltage; Ch4. - the drain-source current peaks thru Q2. 9/17 Circuit description AN2625 Figure 7. Voltages and currents at VIN = 90 VAC, Po = 6.4 W; no clamping - normal operation Figure 8. Voltages and currents at VIN = 90 VAC, Po = 9.44 W; no clamping - normal operation The channels are as follows: - Ch.1 - the voltage across C2; Ch.2 - gate-source voltage of Q2; Ch3. - Q2 drain-source voltage; Ch.4 - Q2 drain-source current peaks. 10/17 AN2625 1.2.2 Circuit description Waveform at start-up Test conditions: VIN RMS = 440 V; VIPer12A-E SMPS at full load (max. power 6.4 W). Figure 9. Voltage and current waveforms at start-up Figure 9 shows a start-up sequence. In all cases the inrush current reaches about 6 A peak - the only inrush limiting device is R1 (30 Ω, 2 W) and the RDS(ON) of Q2 (< 2.7 Ω). The channels are as follows: - Ch.1 - the voltage across C2; Ch.2 - gate-source voltage of Q2; Ch3. - Q2 drain-source voltage; Ch.4 - Q2 drain-source current peaks. 11/17 EMC evaluation 2 AN2625 EMC evaluation The clamping circuit was tested for conducted EMI compliance, according to EN 55022 Class B using Peak and Average detection. It should be noted that the only measure for EMI suppression implemented in the circuit, are the simple chokes L1 and L2 - 1 mH / 0.2 A (Figure 1). The capacitor C1 220 nF / 440 VAC is a simple snubber element across the rectifying diodes of D1 bridge. The EMI filters in the demo boards were preserved in their original place as shown in Figure 2. The circuit was tested at maximum 260 VAC with the clamped voltage set to 300 VDC. VIPer12A-E demo board, output power of 6 W, was the load of the clamping circuit. For output power of 10 W, the clamping circuit was tested under resistive loading (Table 1). 2.1 EMC results - VIPer12A-E demo board load, output power 6W Figure 10. Peak detection, LINE, VIPer12A-E demo board as load Figure 11. Average detection, LINE, VIPer12A-E demo board as load 12/17 AN2625 EMC evaluation Figure 12. Peak detection, NEUTRAL, VIPer12A-E demo board as load Figure 13. Average detection, NEUTRAL, VIPer12A-E demo board as load 13/17 EMC evaluation 2.2 EMC testing - resistive load, output power 10 W Figure 14. Peak detection, LINE, resistive load Figure 15. Average detection, LINE, resistive load 14/17 AN2625 AN2625 EMC evaluation Figure 16. Peak detection, NEUTRAL, resistive load Figure 17. Average detection, NEUTRAL, resistive load 15/17 Conclusions 3 AN2625 Conclusions As it can be seen from Table 2 and Table 3, the circuit shows total efficiency of 60% to 68% in the power range of 5 W to 10 W. Provided the SMPS efficiency is 80%, the overall efficiency can be expected to rise to more than 70%. The evaluation results show that the proposed low components count circuit can successfully limit high input AC voltages in the power range of up to 10 W and accordingly, buffered with this circuit the primary switchers can easily work above the levels they have been originally designed for. 4 Revision history Table 5. 16/17 Document revision history Date Revision 18-Jan-2008 1 Changes Initial release AN2625 Please Read Carefully: Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice. All ST products are sold pursuant to ST’s terms and conditions of sale. Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein. UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK. Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST. ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners. © 2008 STMicroelectronics - All rights reserved STMicroelectronics group of companies Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com 17/17