* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer General Description

Power inverter wikipedia , lookup

Audio power wikipedia , lookup

Alternating current wikipedia , lookup

Loudspeaker wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Ringing artifacts wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Mains electricity wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Buck converter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Stage monitor system wikipedia , lookup

Chirp spectrum wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Opto-isolator wikipedia , lookup

Regenerative circuit wikipedia , lookup

Utility frequency wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

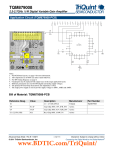

19-0512; Rev 0; 6/06 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer Features The MAX2058 high-linearity digital-variable-gain amplifier (DVGA) is designed to provide 62dB of total gain range and typical output IP3 and output P1dB levels of +32.3dBm and +19dBm, respectively. The device is ideal for a variety of applications, including RFID handheld and portal readers, as well as single and multicarrier 700MHz to 1200MHz GSM/EDGE, cdma2000 ®, WCDMA, and iDEN ® base stations. The MAX2058 yields a high level of component integration, which includes two 5-bit, 31dB digital attenuators, a two-stage driver amplifier, a loopback mixer, and a serial interface to control the attenuators. The MAX2058 is pin compatible with the MAX2059 1800MHz to 2200MHz DVGA, facilitating an easy design-in for applications where a common PC board layout is used for both frequency bands. The MAX2058 is available in a 40-pin thin QFN package with an exposed paddle. Electrical performance is guaranteed over a -40°C to +85°C temperature range. ♦ +32.3dBm Typical Output IP3 Applications ♦ Lead-Free Package Available ♦ +19dBm Typical Output 1dB Compression Point ♦ 700MHz to 1200MHz RF Frequency Range ♦ 1800MHz to 2200MHz RF Frequency Range (MAX2059) ♦ 10.5dB Typical Small-Signal Gain ♦ Includes Two Independent 31dB Attenuator Stages, Yielding 62dB of Total Gain-Control Range with 1dB Steps ♦ 3-Wire SPI™/MICROWIRE™-Compatible ♦ Integrated Loopback Mixer for Tx/Rx SelfDiagnostics ♦ +5V Single-Supply Operation ♦ External Current-Setting Resistors for Scalable Device Power GSM 850/GSM 900 2G and 2.5G EDGE BaseStation Transmitters and Power Amplifiers Cellular cdmaOne™, cdma2000, and Integrated Digital Enhanced Network (iDEN) Base-Station Transmitters and Power Amplifiers Ordering Information PART TEMP RANGE PIN-PACKAGE PKG CODE WCDMA 850MHz and Other 3G Base-Station Transmitters and Power Amplifiers MAX2058ETL -40°C to +85°C 40 Thin QFN-EP** T4066-3 (6mm x 6mm) Transmitter Gain Control MAX2058ETL-T -40°C to +85°C 40 Thin QFN-EP** T4066-3 (6mm x 6mm) MAX2058ETL+ -40°C to +85°C 40 Thin QFN-EP** T4066-3 (6mm x 6mm) MAX2058ETL+T -40°C to +85°C 40 Thin QFN-EP** T4066-3 (6mm x 6mm) Receiver Gain Control Broadband Systems Automatic Test Equipment Digital and Spread-Spectrum Communication Systems Microwave Terrestrial Links RFID Handheld and Portal Readers **EP = Exposed paddle. +Denotes lead-free package. T = Tape-and-reel. Pin Configuration/Functional Diagram appears at end of data sheet. SPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp. cdma2000 is a registered trademark of Telecommunications Industry Association. iDEN is a registered trademark of Motorola, Inc. cdmaOne is a trademark of CDMA Development Group. ________________________________________________________________ Maxim Integrated Products For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com. www.BDTIC.com/maxim 1 MAX2058 General Description MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer ABSOLUTE MAXIMUM RATINGS VCC to GND ...........................................................-0.3V to +5.5V RSET1, RSET2......................................................+1.2V to +4.0V LBBIAS .......................................................(VCC - 1.5V) to +5.5V LB_EN, DATA, CS, CLK .............................-0.3V to (VCC + 0.3V) ATTEN_INA, ATTEN_INB, ATTEN_OUTA, ATTEN_OUTB Input Power .................................................................+24dBm AMPIN, Differential LO Input Power ...............................+12dBm Continuous Power Dissipation (TA = +70°C) 40-Pin TQFN (derated 26.3mW/°C above +70°C) ......2100mW Operating Temperature Range (Note A) .............-40°C to +85°C Junction Temperature ......................................................+150°C θJC ....................................................................................10°C/W θJA ....................................................................................38°C/W Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10s) .................................+300°C Note A: TC is the temperature on the exposed paddle of the package. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. DC ELECTRICAL CHARACTERISTICS (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, R1 = 1.2kΩ, R2 = 3.92kΩ, R3 = 2kΩ, TC = -40°C to +85°C. Typical values are at VCC = +5.0V and TC = +25°C, unless otherwise noted.) (Note 1) PARAMETER SYMBOL Supply Voltage VCC Total Supply Current ICC CONDITIONS MIN TYP MAX UNITS 4.75 5.0 5.25 V LB mixer disabled (LB_EN = 1) 134 156 LB mixer enabled (LB_EN = 0) 158 186 Reference to VCC, VCCLB, VCCLOGIC, VCCBIAS1, VCCBIAS2, VCCAMP mA LOGIC INPUTS (DATA, CS, CLK, LB_EN) Input High Voltage VIH Input Low Voltage VIL 2.4 V Input Current with Logic-High IIH 0.01 µA Input Current with Logic-Low IIL 0.01 µA 0.8 V AC ELECTRICAL CHARACTERISTICS (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, PLO = -6dBm, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) (Note 1) PARAMETER SYMBOL RF Frequency (Note 2) Small-Signal Gain AV POUT Output Power Flatness 2 MAX MAX2059 1800 2200 fRF = 940MHz, TC = +25°C 8.4 10.5 TC = -40°C to +25°C -0.014 TC = +25°C to +85°C -0.021 PIN = 0dBm, fRF = 940MHz, TC = +25°C PIN = 0dBm OIP3 TYP 1200 8.4 10.5 800MHz to 900MHz 0.13 900MHz to 1000MHz -0.52 Attenuation Range Output Third-Order Intercept Point MIN 700 All attenuation settings Gain Variation vs. Temperature Output Power CONDITIONS MAX2058 Two tones: fRF1 = 940MHz, fRF2 = 941MHz, POUT1 = POUT2 = +5dBm 12.8 UNITS MHz dB dB/°C 12.8 dBm dB 62 dB 32.3 dBm _______________________________________________________________________________________ www.BDTIC.com/maxim 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, PLO = -6dBm, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) (Note 1) PARAMETER Output -1dB Compression Point (Note 3) RMS Error Vector Magnitude SYMBOL OP1dB EVM Spurious Emissions in 30kHz Bandwidth (Note 4) Noise Figure CONDITIONS POUT = +12dBm, EDGE modulation POUT = +12dBm, EDGE modulation MIN TYP UNITS 19 dBm 0.5 % 200kHz offset -39.2 400kHz offset -73.5 600kHz offset -82.7 1.2MHz offset -85.7 NF MAX dBc 6.8 dB Input Return Loss 50Ω source, minimum attenuation setting 18 dB Output Return Loss 50Ω load, minimum attenuation setting 20 dB Attenuator measured separately ZS = ZL = 50Ω 3.3 dB Attenuator measured separately ZS = ZL = 50Ω, two tones: fRF1 = 940MHz, fRF2 = 941MHz, PIN1 = PIN2 = +5dBm 44 dBm 31 dB 5-BIT DIGITAL ATTENUATORS Insertion Loss Input Third-Order Intercept Point IIP3 Control Range Attenuation Step Size Variation vs. Frequency Attenuation Variation vs. Temperature 800MHz to 900MHz ±0.08 900MHz to 1000MHz ±0.06 800MHz to 1000MHz, TC = -40°C to +25°C ±0.002 800MHz to 1000MHz, TC = +25°C to +85°C ±0.003 Step Size dB dB/°C 1 -0.2 +0.4 -0.2 +0.5 dB Relative Step Accuracy 800MHz to 1000MHz dB Absolute Step Accuracy 800MHz to 1000MHz Spurious Emissions in 300kHz Bandwidth (Note 5) No RF input, attenuator A stepped from 0 to 2dB, 7dB to 9dB, 15dB to 17dB, 0 to 31dB, 31dB to 0dB, with attenuator B at 0dB; attenuator B stepped from 0 to 2dB, 7dB to 9dB, 15dB to 17dB, 0 to 31dB, 31dB to 0dB, with attenuator A at 0dB -85 dBm Switching Speed From chip select transitioning high to the output settling to within 1dB of steady state output 0.3 µs dB _______________________________________________________________________________________ www.BDTIC.com/maxim 3 MAX2058 AC ELECTRICAL CHARACTERISTICS (continued) MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer AC ELECTRICAL CHARACTERISTICS (continued) (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, PLO = -6dBm, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) (Note 1) PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS 100 MHz LOOPBACK MIXER LO Frequency (Note 2) fLO LO Input Power PLO 40 Output Power (Note 6) PIN = +5dBm, fRF = 940MHz, TC = +25°C Gain Accuracy PIN = +5dBm, TC = -40°C to +25°C Output Third-Order Intercept Point (Note 6) OIP3 Output Noise Floor ON/OFF Switching Time ATTEN_OUTB to LBOUT Isolation Output Return Loss LO Port Return Loss -6 0 dBm -12.7 -10.8 dBm 800MHz to 900MHz ±1.7 900MHz to 1000MHz ±1.7 dB Two tones: fRF1 = 940MHz, fRF2 = 940.2MHz, PIN1 = PIN2 = +2dBm, TC = +25°C 10.6 dBm PIN = +5dBm -137 dBc/Hz LB_EN enable time 0.12 LB_EN disable time 0.12 Mixer enabled, attenuators A and B both set to 31dB, PIN = +5dBm LBOUT to ATTEN_OUTB Isolation -14.7 µs 67 dB dB Mixer disabled, PIN = 0dBm 50 Mixer enabled, 50Ω load 22 Mixer disabled, 50Ω load 23 50Ω source 32 dB 38 MHz dB SERIAL PERIPHERAL INTERFACE (SPI) Maximum Clock Speed Data to Clock Setup Time tCS 1 ns Data to Clock Hold Time tCH 9 ns Clock to CS Setup Time tES 4 ns CS Positive Pulse Width tEW 18 ns CS Negative Pulse Width tEWN 24 ns CLOCK Pulse Width tCW 13 ns Note 1: All limits include external component losses. Output measurements taken at RFOUT or LBOUT ports of the Typical Application Circuit. Note 2: Operating outside this range is possible, but with degraded performance of some parameters. Note 3: Compression point characterized. It is advisable not to continuously operate the VGA RF input above +15dBm. Note 4: Input RF source contribution to spurious emissions (Agilent ESG 4435B, PSA E4443A): 200kHz = -39.2dBc, 400kHz = -73.5dBc, 600kHz = -83.2dBc, 1.2MHz = -85.7dBc Note 5: No SPI clock input applied. Note 6: Guaranteed by design and characterization. 4 _______________________________________________________________________________________ www.BDTIC.com/maxim 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer TC = -40°C 12 9 TC = +25°C 10 VCC = 5.0V 9 VCC = 4.75V 8 TC = +85°C 7 -5 -15 7 -25 6 900 1000 1100 RF FREQUENCY (MHz) 1200 700 900 1000 1100 700 1200 MAX2058 toc04 1.0 5 GAIN (dB) ERROR (dB) -0.5 0 -25 -1.0 900 1000 1100 RF FREQUENCY (MHz) 1200 700 ATTEN B ABS ACCURACY vs. RF FREQUENCY 700 1200 800 900 1000 1100 RF FREQUENCY (MHz) 1200 OUTPUT IP3 vs. RF FREQUENCY ATTEN B REL ACCURACY vs. RF FREQUENCY 34 TC = +5°C TC = -40°C 33 0 -0.5 OUTPUT IP3 (dBm) 0.5 ERROR (dB) 0.5 -1.0 700 900 1000 1100 RF FREQUENCY (MHz) 1.0 MAX2058 toc07 1.0 800 MAX2058 toc08 800 -5 -15 -0.5 -1.0 1200 15 0.5 0 900 1000 1100 RF FREQUENCY (MHz) GAIN vs. RF FREQUENCY ADJUSTING ATTEN B ATTEN A REL ACCURACY vs. RF FREQUENCY 0.5 700 800 RF FREQUENCY (MHz) ATTEN A ABS ACCURACY vs. RF FREQUENCY 1.0 800 MAX2058 toc06 800 MAX2058 toc05 700 MAX2058 toc09 6 ERROR (dB) 5 GAIN (dB) 10 8 ERROR (dB) VCC = 5.25V 11 GAIN (dB) GAIN (dB) 11 15 MAX2058 toc03 12 13 MAX2058 toc02 TC = +5°C MAX2058 toc01 13 0 -0.5 900 1000 1100 RF FREQUENCY (MHz) 1200 31 TC = +25°C TC = +85°C 30 29 -1.0 800 32 700 800 900 1000 1100 RF FREQUENCY (MHz) 1200 800 850 900 950 RF FREQUENCY (MHz) 1000 _______________________________________________________________________________________ www.BDTIC.com/maxim 5 MAX2058 Typical Operating Characteristics (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) GAIN vs. RF FREQUENCY GAIN vs. RF FREQUENCY GAIN vs. RF FREQUENCY (MAXIMUM GAIN) ADJUSTING ATTEN A (MAXIMUM GAIN) Typical Operating Characteristics (continued) (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) TC = +85°C 9 TC = +25°C 10 MAX2058 toc12 MAX2058 toc10 VCC = 5.25V 33 NOISE FIGURE vs. RF FREQUENCY NOISE FIGURE vs. RF FREQUENCY 10 MAX2058 toc11 OUTPUT IP3 vs. RF FREQUENCY 34 9 32 31 VCC = 5.0V VCC = 4.75V 30 NOISE FIGURE (dB) NOISE FIGURE (dB) OUTPUT IP3 (dBm) VCC = 5.25V 8 7 6 VCC = 5.0V 7 6 VCC = 4.75V TC = +5°C 5 8 5 TC = -40°C 4 4 1000 700 OUTPUT P1dB vs. RF FREQUENCY 21 TC = -40°C TC = +5°C 22 21 VCC = 5.25V 18 TC = +25°C 16 19 18 VCC = 5.0V 17 VCC = 4.75V 16 TC = +85°C 15 15 14 14 800 900 1000 1100 RF FREQUENCY (MHz) 0 5 0dB 4dB 2dB 10 15 20 25 16dB, 31dB 900 1000 1100 RF FREQUENCY (MHz) 1200 700 0 OUTPUT RETURN LOSS (dB) MAX2058 toc16 5 10 31dB 15 20 0dB, 1dB 900 1000 1100 RF FREQUENCY (MHz) 700 1200 OUTPUT RETURN LOSS vs. RF FREQUENCY ATTEN A VARIED INPUT RETURN LOSS vs. RF FREQUENCY ATTEN B VARIED 0 800 10 31dB 20 30 800 700 6 800 900 1000 1100 RF FREQUENCY (MHz) 1200 16dB, 31dB 4dB 20 30 2dB 800 900 1000 1100 RF FREQUENCY (MHz) 1200 8dB 0dB 1dB 40 700 1200 10 0dB 40 900 1000 1100 RF FREQUENCY (MHz) 0 25 30 1dB OUTPUT RETURN LOSS vs. RF FREQUENCY ATTEN B VARIED OUTPUT RETURN LOSS (dB) 800 8dB 30 MAX2058 toc17 700 1200 INPUT RETURN LOSS vs. RF FREQUENCY ATTEN A VARIED INPUT RETURN LOSS (dB) 19 17 700 1200 20 OUTPUT P1dB (dBm) 20 OUTPUT P1dB (dBm) 900 1000 1100 RF FREQUENCY (MHz) OUTPUT P1dB vs. RF FREQUENCY MAX2058 toc13 22 800 MAX2058 toc15 850 900 950 RF FREQUENCY (MHz) MAX2058 toc14 800 MAX2058 toc18 29 INPUT RETURN LOSS (dB) MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer 700 800 900 1000 1100 RF FREQUENCY (MHz) _______________________________________________________________________________________ www.BDTIC.com/maxim 1200 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer -60 ATTEN A, 31dB -70 18 17 16 15 800 900 1000 1100 RF FREQUENCY (MHz) 800 MIXER CONV LOSS vs. RF FREQUENCY VCC = 5.0V 800 1000 TC = +5°C TC = -40°C 12 850 900 950 RF FREQUENCY (MHz) 1000 MIXER OUTPUT IP3 vs. RF FREQUENCY 13 VCC = 5.25V 12 PLO = -6dBm 17 16 OUTPUT IP3 (dBm) PLO = -3dBm 18 11 10 9 TC = +25°C 11 10 VCC = 4.75V VCC = 5.0V 9 PLO = 0dBm 8 14 8 TC = +85°C 7 7 1000 800 11 10 PLO = -6dBm PLO = 0dBm 9 0 MIXER OUT RETURN LOSS (dB) 12 MAX2058 toc25 PLO = -3dBm, 0dBm TC = +5°C TC = -40°C 20 30 TC = +85°C 850 900 950 RF FREQUENCY (MHz) 1000 1000 0 10 20 30 TC = +25°C VCC = 4.75V, 5.0V, 5.25V 40 40 7 850 900 950 RF FREQUENCY (MHz) MIXER OUTPUT RETURN LOSS vs. RF FREQUENCY (MIXER ENABLED) 10 8 800 800 1000 MIXER OUTPUT RETURN LOSS vs. RF FREQUENCY (MIXER ENABLED) MIXER OUTPUT IP3 vs. RF FREQUENCY 13 850 900 950 RF FREQUENCY (MHz) MIXER OUT RETURN LOSS (dB) 850 900 950 RF FREQUENCY (MHz) MAX2058 toc26 800 MAX2058 toc27 15 OUTPUT IP3 (dBm) VCC = 5.25V 16 MIXER OUTPUT IP3 vs. RF FREQUENCY OUTPUT IP3 (dBm) CONVERSION LOSS (dB) 19 850 900 950 RF FREQUENCY (MHz) 13 MAX2058 toc22 20 17 14 14 1200 VCC = 4.75V 18 15 MAX2058 toc23 700 19 TC = -40°C TC = +5°C ATTEN B, 31dB MAX2058 toc21 TC = +25°C CONVERSION LOSS (dB) -50 20 MAX2058 toc20 TC = +85°C 19 CONVERSION LOSS (dB) ATTEN A AND B, 0dB GAIN (dB) 20 MAX2058 toc19 -40 -80 MIXER CONV LOSS vs. RF FREQUENCY MIXER CONV LOSS vs. RF FREQUENCY -30 MAX2058 toc24 REVERSE GAIN vs. RF FREQUENCY ADJUSTING ATTEN A AND B 700 800 900 1000 1100 RF FREQUENCY (MHz) 1200 700 800 900 1000 1100 RF FREQUENCY (MHz) 1200 _______________________________________________________________________________________ www.BDTIC.com/maxim 7 MAX2058 Typical Operating Characteristics (continued) (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) Typical Operating Characteristics (continued) (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) MIXER OUTPUT RETURN LOSS vs. RF FREQUENCY (MIXER DISABLED) 20 30 VCC = 4.75V, 5.0V, 5.25V 20 900 1000 1100 RF FREQUENCY (MHz) TC = -40°C 40 700 1200 900 1000 1100 RF FREQUENCY (MHz) 0 1200 -10 VCC = 4.75V, 5.0V, 5.25V GAIN (dB) -10 20 -20 -40 -40 100 150 200 700 800 900 1000 1100 300 1200 350 400 450 500 550 LO FREQUENCY (MHz) RF FREQUENCY (MHz) RF FREQUENCY (MHz) ATTEN A ONLY ABS ACCURACY vs. RF FREQUENCY ATTEN A ONLY ABS ACCURACY vs. RF FREQUENCY (NMT 450MHz BAND) ATTEN A ONLY REL ACCURACY vs. RF FREQUENCY 1.0 0.5 0.5 ERROR (dB) 1.0 0 0.5 0 -0.5 -0.5 -1.0 -1.0 -1.5 -1.5 800 900 1000 RF FREQUENCY (MHz) 1100 1200 0 -0.5 -1.0 -2.0 -2.0 MAX2058 toc36 1.5 ERROR (dB) 1.5 1.0 MAX2058 toc35 2.0 MAX2058 toc34 2.0 700 -20 -30 -30 40 200 0 MAX2058 toc32 MAX2058 toc31 10 50 100 150 LO FREQUENCY (MHz) ATTEN A ONLY GAIN vs. RF FREQUENCY (NMT 450MHz BAND) 0 30 8 800 ATTEN A ONLY GAIN vs. RF FREQUENCY GAIN (dB) LO RETURN LOSS (dB) 0 50 TC = +25°C TC = +5°C LO RETURN LOSS vs. LO FREQUENCY (MIXER ENABLED) 0 TC = +85°C 20 30 30 40 800 10 TC = +25°C 40 700 MAX2058 toc30 MAX2058 toc29 10 MAX2058 toc33 TC = +85°C 0 LO RETURN LOSS (dB) TC = -40°C 0 MIXER OUT RETURN LOSS (dB) 10 TC = +5°C LO RETURN LOSS vs. LO FREQUENCY (MIXER ENABLED) MIXER OUTPUT RETURN LOSS vs. RF FREQUENCY (MIXER DISABLED) MAX2058 toc28 MIXER OUT RETURN LOSS (dB) 0 ERROR (dB) MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer 300 350 400 450 RF FREQUENCY (MHz) 500 550 700 800 900 1000 RF FREQUENCY (MHz) _______________________________________________________________________________________ www.BDTIC.com/maxim 1100 1200 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer GAIN (dB) GAIN (dB) 0 -20 -40 -40 -1.0 400 450 500 700 550 800 900 1000 1100 300 1200 350 500 550 2.0 1.5 1.0 1.0 0.5 0.5 0 MAX2058 toc41 1.5 450 ATTEN B ONLY ABS ACCURACY vs. RF FREQUENCY (NMT 450MHz BAND) ATTEN B ONLY ABS ACCURACY vs. RF FREQUENCY 2.0 400 RF FREQUENCY (MHz) RF FREQUENCY (MHz) RF FREQUENCY (MHz) ERROR (dB) 350 MAX2058 toc40 300 -20 -30 -30 -0.5 ERROR (dB) ERROR (dB) -10 -10 0.5 ATTEN B ONLY GAIN vs. RF FREQUENCY (NMT 450MHz BAND) 0 MAX2058 toc38 0 MAX2058 toc37 1.0 ATTEN B ONLY GAIN vs. RF FREQUENCY MAX2058 toc39 ATTEN A ONLY REL ACCURACY vs. RF FREQUENCY (NMT 450MHz BAND) 0 -0.5 -0.5 -1.0 -1.0 -1.5 -1.5 -2.0 -2.0 700 800 900 1000 RF FREQUENCY (MHz) 1100 1200 300 350 400 450 500 550 RF FREQUENCY (MHz) _______________________________________________________________________________________ www.BDTIC.com/maxim 9 MAX2058 Typical Operating Characteristics (continued) (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) Typical Operating Characteristics (continued) (MAX2058 Typical Application Circuit, VCC = +4.75V to +5.25V, digital attenuators set for maximum gain, 700MHz ≤ fRF ≤ 1200MHz, 40MHz ≤ fLO ≤ 100MHz, TC = -40°C to +85°C. Typical values are at VCC = 5.0V, PIN = 0dBm, fRF = 940MHz, fLO = 45MHz, fLBOUT = fRF - fLO, and TC = +25°C, unless otherwise noted.) ATTEN B ONLY REL ACCURACY vs. RF FREQUENCY (NMT 450MHz BAND) ATTEN B ONLY REL ACCURACY vs. RF FREQUENCY 0.5 ERROR (dB) 0 -0.5 -0.5 -1.0 -1.0 700 800 900 1000 1100 1200 300 350 400 450 500 550 RF FREQUENCY (MHz) RF FREQUENCY (MHz) SUPPLY CURRENT vs. SUPPLY VOLTAGE (MIXER DISABLED) SUPPLY CURRENT vs. SUPPLY VOLTAGE (MIXER ENABLED) TC = +85°C 130 110 4.750 TC = +25°C 4.875 TC = +5°C 170 SUPPLY CURRENT (mA) 140 120 180 MAX2058 toc44 150 10 0 TC = -40°C TC = +85°C MAX2058 toc45 ERROR (dB) 0.5 MAX2058 toc43 1.0 MAX2058 toc42 1.0 SUPPLY CURRENT (mA) MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer TC = +25°C 160 150 TC = +5°C TC = -40°C 140 5.000 VCC (V) 5.125 5.250 130 4.750 4.875 5.000 VCC (V) 5.125 5.250 ______________________________________________________________________________________ www.BDTIC.com/maxim 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer PIN NAME 1 LO+ 2 LO- FUNCTION Loopback Mixer Local Oscillator Positive Input Loopback Mixer Local Oscillator Negative Input Loopback Mixer Supply Voltage. +5V supply for the internal loopback mixer. Bypass to GND with 100pF and 0.1µF capacitors as close as possible to the pin. 3 VCCLB 4 LBOUT Loopback Mixer RF Output. Internally matched to 50Ω. AC-couple with a capacitor. 5 LB_EN Loopback Mixer Logic Input. Set to logic-low 0 to enable the mixer. Set to logic-high 1 to disable the mixer. 6 DATA SPI Digital Data Input 7 CLK SPI Clock Input 8 CS SPI Chip-Select Input 9 VCCLOGIC 10, 11, 13, 14, 16, 17, 19, 22, 24, 25, 26, 30, 32, 34, 35, 37, 38 GND 12 Logic Supply Voltage. +5V supply for the internal logic circuitry. Bypass to GND with 100pF and 0.1µF capacitors as close as possible to the pin. Ground ATTEN_OUTB Attenuator B Output. Internally matched to 50Ω. Attenuator B Supply. +5V supply for attenuator B. Bypass to GND with 100pF and 0.01µF capacitors as close as possible to the pin. 15 VCC 18 ATTEN_INB 20 RSET2 Output Amplifier Bias-Current-Setting Resistor. Sets the bias current for the output amplifier stage. Connect a 3.92kΩ resistor to ground. 21 VCCBIAS2 Bias Circuit Supply Voltage. +5V supply for the internal bias circuitry. Bypass to GND with 1000pF and 0.1µF capacitors as close as possible to the pin. 23 AMPOUT RF Amplifier Output. Internally matched to 50Ω. 27 VCCAMP RF Amplifier Supply Voltage. +5V supply for the RF amplifier. Bypass to GND with 1000pF and 0.1µF capacitors as close as possible to the pin. 28 AMPIN 29 VCCBIAS1 31 RSET1 33 Attenuator B Input. Internally matched to 50Ω. RF Amplifier Input. Internally matched to 50Ω. Bias Circuit Supply Voltage. +5V supply for the internal bias circuitry. Bypass to GND with 1000pF and 0.1µF capacitors as close as possible to the pin. Input Amplifier Bias-Current-Setting Resistor. Sets the bias current for the input amplifier stage. Connect a 1.2kΩ resistor to ground. ATTEN_OUTA Attenuator A Output. Internally matched to 50Ω. 36 VCC 39 ATTEN_INA 40 LBBIAS EP GND Attenuator A Supply Voltage. +5V supply for attenuator A. Bypass to GND with 100pF and 0.01µF capacitors as close as possible to the pin. Attenuator A Input. Internally matched to 50Ω. Loopback Mixer Bias-Current-Setting Resistor. Sets the bias current for the mixer. Connect a 2kΩ resistor to ground. Exposed Ground Paddle. Solder the exposed paddle to GND using multiple vias. ______________________________________________________________________________________ www.BDTIC.com/maxim 11 MAX2058 Pin Description MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer Detailed Description The MAX2058 high-linearity DVGA consists of two 5-bit, 31dB digital attenuators, a fixed-gain two-stage driver amplifier, a loopback mixer, and a serial interface to control the attenuators. This high level of component integration makes the MAX2058 ideal for base-station transmitter applications. The MAX2058 is designed to operate in the 700MHz to 1200MHz frequency ranges. The overall cascaded performance of the MAX2058 produces a typical 10.5dB gain, a +32.3dBm OIP3, a 19dBm OP1dB, and a total 62dB gain-control range. 5-Bit Attenuators The MAX2058 integrates two 5-bit digital attenuators to achieve a high dynamic range. Each attenuator has a 31dB control range, a 1dB step size, and is programmed with the 3-wire SPI. See the Applications Information section and Table 1 for attenuator programming details. The attenuators can be used for both static and dynamic power control. Table 1. Attenuator Programming ATTENUATOR A (5 MSBs) ATTENUATOR B (5 LSBs) Bit 9 = 16dB step Bit 4 = 16dB step Bit 8 = 8dB step Bit 3 = 8dB step Bit 7 = 4dB step Bit 2 = 4dB step Bit 6 = 2dB step Bit 1 = 2dB step Bit 5 = 1dB step Bit 0 = 1dB step DATA MSB BIT 9 BIT 8 BIT 1 BIT 0 LSB Driver Amplifier The MAX2058 includes a two-stage medium power amplifier with a fixed 17.5dB gain. The driver amplifier circuit is optimized for high linearity and medium output power capability for the 800MHz to 1000MHz frequency range. The driver amplifier is intended to amplify a modulated signal and drive a high-power amplifier in base-station transmitters. In a typical application, the driver amplifier is cascaded in between the two digital attenuators. See the Typical Application Circuit. The two-stage amplifier stage can be disabled for applications where only the digital attenuators and/or loopback mixer are used. To disable the two-stage amplifier, ground or leave unconnected the amplifier supplies VCCBIAS2, VCCAMP, VCCBIAS1, and also the inputs for setting the amplifier bias currents RSET1, RSET2. This reduces the supply current by approximately 132mA under typical conditions. Loopback Mixer The MAX2058 loopback mixer uses a double-balanced active architecture designed to operate with a 700MHz to 1200MHz RF frequency range, and a 40MHz to 100MHz LO frequency range. The RF port of the mixer is connected internally (with an on-chip switch) to the input of the first attenuator stage. The mixer’s IF port is matched for a single-ended 50Ω impedance, while the LO port requires a differential input impedance of 100Ω. The loopback mixer facilitates a self-diagnostic mode for cellular transceivers, whereby the Tx band signal at the input of the mixer can be translated up or down to the corresponding Rx band. This translated signal can then be fed back to the radio’s receiver for complete Tx/Rx loop diagnostics. The loopback mixer is enabled and disabled with LB_EN. Set LB_EN to a logic-low 0 to enable the mixer, set LB_EN to a logic-high 1 to disable the mixer. Applications Information CLOCK tCH tCS tCW SPI Interface and Attenuator Settings CS tEWN tES tEW NOTES: DATA ENTERED ON CLOCK RISING EDGE. ATTENUATOR STATE CHANGE ON CS RISING EDGE. Figure 1. SPI Timing Diagram 12 The two 5-bit attenuators are programmed with the 3wire SPI/MICROWIRE-compatible serial interface using 10-bit words. Bit 9 of the 10-bit data is shifted in first, along with all remaining data bits, on the rising edge of the clock regardless of CS being high or low. Once all the data bits are shifted in, all will be sent to the attenuators on the rising edge of CS, thus changing the attenuation state. For standard SPI operation, pull CS low for the duration of a valid 10-bit data set (tEWN). This CS negative pulse width includes the setup time of the rising clock edge to CS transitioning high (tES). See Figure 1. ______________________________________________________________________________________ www.BDTIC.com/maxim 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer from the EP. In addition, provide the EP with a lowinductance path to electrical ground. The EP MUST be soldered to a ground plane on the PC board, either directly or through an array of plated via holes. Table 2. Component List Referring to the Typical Application Circuit External Bias Bias currents for the two-stage amplifier and the loopback mixer are set and optimized with external resistors. Resistor R1 (pin 31) sets the bias current for the input amplifier, R2 (pin 20) sets the bias current for the output amplifier, and R3 (pin 40) sets the bias for the loopback mixer. The external biasing resistor values can be increased for reduced current operation at the expense of performance. Contact the factory for details. COMPONENT VALUE DESCRIPTION C1, C4, C10, C13, C16 0.1µF Microwave capacitors (0603) C2, C5, C8, C17 100pF Microwave capacitors (0402) C3, C6, C14, C19 47pF Microwave capacitors (0402) C7, C18 0.01µF Microwave capacitors (0402) C9, C12, C15 1000pF Microwave capacitors (0402) C11 3.9pF Microwave capacitor (0402) Board Layout R1 1.2kΩ ±1% resistor (0402) The pin configuration of the MAX2058 has been optimized to facilitate a very compact physical layout of the device and its associated discrete components. The exposed paddle (EP) of the MAX2058’s thin QFNEP package provides a low thermal-resistance path to the die. It is important that the PC board on which the MAX2058 is mounted be designed to conduct heat R2 3.92kΩ ±1% resistor (0402) R3 2.0kΩ ±1% resistor (0402) R4 110Ω MAX5873 DUAL DAC MAX4395 QUAD AMP ±1% resistor (0402) T1 2:1 RF transformer (100:50) Mini-Circuits TC2-1T U1 — MAX2058 MAXIM IC MAX2021/MAX2022/MAX2023* ZERO-IF MODS/DEMODS MAX2058/MAX2059* RF DIGITAL VGAs I 12 90° 0° 31dB ∑ 17.5dB 31dB RF OUT Q 12 SPI LOGIC MAX9491* VCO + PLL *FUTURE PRODUCTS—CONTACT FACTORY FOR SAMPLES 45, 80, OR 95MHz LO LOOPBACK Rx SPI OUT OFF CONTROL (FEEDS BACK INTO Rx CHAIN FRONT-END) Figure 2. Direct Conversion Transmitter for GSM/EDGE Basestations ______________________________________________________________________________________ www.BDTIC.com/maxim 13 MAX2058 The 5 MSBs of the 10-bit word program attenuator A, and the 5 LSBs of the 10-bit word program attenuator B. Each bit sets the attenuators to a corresponding attenuation level. For example, logic-low 0 for bit 5 and bit 0 of attenuator A and B, respectively, sets both attenuators at 1dB. 00000 configures both attenuators for 31dB attenuation and 11111 sets for 0dB attenuation. See Table 1 for programming details. Direct-Conversion Base-Station Transmitter together with the MAX2021/MAX2022/MAX2023* directconversion modulators/demodulators, the MAX5873 dual-channel DAC, and the MAX4395 quad amplifier, form an ideal total transmitter lineup. This overall system is highly efficient and low cost, while maintaining high linearity and low noise performance. The MAX2058/MAX2059 are designed to interface directly with Maxim’s direct-conversion quadrature modulators and high-speed DACs to provide a complete solution for GSM/EDGE base-station transmitter applications. See Figure 2. The MAX2058/MAX2059, Typical Application Circuit VCC T1 40 LO+ R4 LOVCCLB VCC C1 C2 C3 39 38 1 36 37 35 34 33 RSET1 R1 GND GND GND VCC GND GND LBBIAS ATTN_INA C19 R3 LO INPUT C18 ATTEN_OUTA C17 RF INPUT 32 31 VCC 30 5-BIT ATTENUATOR A GND C15 2 29 3 28 VCCBIAS1 C16 C14 AMPIN MAX2058 LBOUT LB_EN 4 27 5 DATA CLK 25 6 SPI 7 VCCAMP 26 GND DRIVER AMP LBOUT 24 C12 VCC C13 GND GND C11 CS VCCLOGIC VCC C4 C5 GND 23 8 9 E.P. 5-BIT ATTENUATOR B 22 10 21 AMPOUT GND VCCBIAS2 C9 C6 C8 20 RSET2 19 GND 18 ATTEN_INB 17 GND 16 GND 15 VCC 14 GND 13 GND 12 ATTEN_OUTB 11 GND MAX2058 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer R2 C7 RF OUTPUT 14 ______________________________________________________________________________________ www.BDTIC.com/maxim VCC C10 700MHz to 1200MHz High-Linearity, SPI-Controlled DVGA with Integrated Loopback Mixer GND ATTEN_OUTA GND RSET1 37 GND GND 38 VCC ATTEN_INA 39 GND LBBIAS 40 36 35 34 33 32 31 5-BIT ATTENUATOR A LO+ 1 30 GND LO- 2 29 VCCBIAS1 VCCLB 3 28 AMPIN MAX2058 LBOUT 4 27 VCCAMP LB_EN 5 26 GND DRIVER AMP 25 GND DATA 6 CLK 7 24 GND SPI 23 AMPOUT CS 8 5-BIT ATTENUATOR B VCCLOGIC 9 22 GND GND 10 11 12 13 14 15 16 17 18 19 20 GND ATTEN_OUTB GND GND VCC GND GND ATTEN_INB GND RSET2 21 VCCBIAS2 Chip Information PROCESS: SiGe BiCMOS Package Information For the latest package outline information, go to www.maxim-ic.com/packages. Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 15 © 2006 Maxim Integrated Products is a registered trademark of Maxim Integrated Products, Inc. www.BDTIC.com/maxim MAX2058 Pin Configuration/Functional Diagram

![NMEA GPS Module - main [gps.0xdc.ru]](http://s1.studyres.com/store/data/006332431_1-f6d741b7c1fd26623b37b5b0b457162e-150x150.png)