* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Interfacing LVPECL 3.3V Drivers with Xilinx 2.5V Differential Receivers Summary

UniPro protocol stack wikipedia , lookup

Serial digital interface wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Power MOSFET wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Integrating ADC wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

FTA receiver wikipedia , lookup

Two-port network wikipedia , lookup

Power electronics wikipedia , lookup

Voltage regulator wikipedia , lookup

Operational amplifier wikipedia , lookup

Current mirror wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Regenerative circuit wikipedia , lookup

Opto-isolator wikipedia , lookup

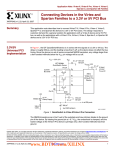

Application Note: Virtex-II Pro, Virtex-4, Virtex-5, Spartan-3/3E Families Interfacing LVPECL 3.3V Drivers with Xilinx 2.5V Differential Receivers R Author: Mark Wood XAPP696 (v1.3) May 1, 2008 Summary This application note describes how to interface 3.3V differential Low-Voltage Positive Emitter Coupled Logic (LVPECL) drivers with Xilinx® 2.5V differential receivers, including Virtex®-II Pro, Virtex-II Pro X, Virtex-4, Virtex-5, Spartan®-3E, and Spartan-3 FPGA 2.5V LVPECL and Low Voltage Differential Signaling (LVDS). Several interface modifications are presented with supporting IBIS simulation results. By reducing the 3.3V LVPECL common mode voltage, it is safe to interface with Virtex-II Pro through Virtex-5 and Spartan-3/3E FPGA 2.5V LVPECL and LVDS receivers (and future Xilinx devices that support 2.5V differential inputs). Introduction Differential 3.3V LVPECL is commonly used for the transmission of high-speed, low-jitter clocks and high bit-rate data. LVPECL offers the advantage of high noise immunity over relatively long interconnects. Differential input buffers configured with Virtex-E and Virtex-II FPGA LVPECL can be directly connected to 3.3V LVPECL drivers from other vendors. However, Virtex-II Pro through Virtex-5 and Spartan-3/3E FPGA differential receivers cannot directly receive 3.3V LVPECL output levels with standard receiver termination. For the Spartan-3A FPGA families, designs should use the 3.3V LVDS and LVPECL input standards. Virtex-II Pro through Virtex-5 and Spartan-3/3E FPGA Differential 2.5V Input Specification A standard 2.5V LVPECL interface is shown in Figure 1. The recommended termination technique for interfacing Xilinx differential receivers to 2.5V differential standards is a parallel 100Ω termination between the receiver inputs (as shown in Figure 1). The acceptable input level range for Virtex-II Pro through Virtex-5 and Spartan-3 FPGA differential input receivers is summarized in Table 1. An IBIS simulation of the interface is shown in Figure 2. The driver and receiver used in the simulation were Virtex-II Pro FPGA 2.5V LVPECL, and the receiver voltages were probed at the die pads (see Figure 2 for simulation results). Virtex-II Pro/X FPGA 2.5V LVPECL/LVDS or Spartan-3/3E FPGA LVDS Receiver Virtex-II Pro/X FPGA 2.5V LVPECL Driver Z0 = 50Ω 70Ω U (H0) + + 100Ω (1) 187Ω 70Ω – Z0 = 50Ω – U (H2) Note: 1. 100Ω receiver termination is not required if a Virtex-II Pro/X FPGA LVDS_25_DT receiver, a Spartan-3 FPGA LVDS_25_DCI receiver, or a Spartan-3E FPGA LVDS DIFF_TERM is used. X696_01_042308 Figure 1: Virtex-II Pro through Virtex-5 and Spartan-3/3E FPGA 2.5V LVPECL Termination Circuit © 2004–2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners. XAPP696 (v1.3) May 1, 2008 www.BDTIC.com/XILINX www.xilinx.com 1 R 3.3V LVPECL Output Specification Table 1: Xilinx Virtex-II Pro through Virtex-5 and Spartan-3 FPGA Differential Receiver DC Levels DC Parameter Symbol Condition Min Typ Max Differential Input Voltage (Data Sheet Specification) VIDIFF VCM = 1.25V 0.1V 1.0V Input Common-Mode Voltage (Data Sheet Specification) VICM VIDIFF = ±350 mV 0.3V 2.2V Simulated Differential Input Voltage VIDIFFSIM Measured from Figure 2 0.82V Simulated Common-Mode Input Voltage VICMSIM Measured from Figure 2 1.2V Figure 2: Virtex-II Pro FPGA 2.5V LVPECL Receiver Voltage Levels 3.3V LVPECL Output Specification Many parts used in high-speed transceiver designs use 3.3V LVPECL differential standard I/O. The 3.3V LVPECL output voltage levels vary from vendor to vendor. However, a maximum output level exceeding 2.5V is commonly specified in vendor data sheets. A common termination technique used for 3.3V LVPECL interfaces is shown in Figure 3. 2 www.BDTIC.com/XILINX www.xilinx.com XAPP696 (v1.3) May 1, 2008 R Interface Modification Advice Standard (non Xilinx) 3.3V LVPECL Driver DC 50Ω VCCO–2.0V Standard 3.3V LVPECL Receiver 50Ω Z0 = 50Ω + + Z0 = 50Ω – – X696_03_042308 Figure 3: Standard 3.3V LVPECL Termination Interface Modification Advice When interfacing a 3.3V LVPECL driver to a Virtex-II Pro through Virtex-5 or Spartan-3/3E FPGA 2.5V differential receiver, the output specification for the driver must be considered. If the output levels of the driver are within the Xilinx specified receiver levels, the standard receiver termination can be used. This typically consists of a 100Ωparallel termination, or 50Ωsplit termination to VCCO – 2.0V. For driver output levels that exceed the specified receiver input levels, custom termination techniques to reduce the common mode voltage level or the voltage swing can be used. DC-Coupled Receiver Common Mode Voltage Shift By replacing the standard receiver termination with a custom termination network, the common mode voltage can be reduced, while maintaining an optimal voltage swing. An example of such a technique is shown in Figure 4. Six termination resistors are required for each differential receiver. Standard (non Xilinx) 3.3V LVPECL Driver DC 130Ω Z0 = 50Ω + – 3.3V 130Ω 27Ω Virtex-II Pro/X FPGA 2.5V LVPECL/LVDS, or Spartan-3/3E FPGA LVDS Receiver U (D0) + U (A0) Z0 = 50Ω 27Ω – U (D2) U (A2) 56Ω 56Ω X696_04_042308 Figure 4: 3.3V LVPECL to 2.5V Differential Receiver DC-Coupled Interface The circuit shown in Figure 4 was simulated in IBIS. In the results in Figure 5, the common mode voltage was reduced from approximately 2.25V (at the driver output) to 1.5V (at the receiver input), comfortably meeting the Xilinx Virtex-II Pro through Virtex-5 and Spartan-3/3E FPGA differential receiver input specifications. The simulation results are summarized in Table 2. XAPP696 (v1.3) May 1, 2008 www.BDTIC.com/XILINX www.xilinx.com 3 R Interface Modification Advice Table 2: Summary of Figure 5 IBIS Simulation Results Parameter Symbol Typical Simulated Differential output voltage Vodiffsim 0.7V Simulated Output common-mode voltage Vocmsim 2.25V Simulated Differential input voltage Vidiffsim 0.5V Simulated Input common-mode voltage Vicmsim 1.5V Figure 5: 3.3V LVPECL to 2.5V Receiver IBIS Simulation Note: The termination network shown in Figure 4 is intended for reference purposes only. The optimal termination values are dependent on the driver output levels and could need to be adjusted to achieve optimal voltage levels at the receiver. AC-Coupled Receiver Common Mode Voltage Shift Inserting a series capacitor and biasing network into each leg of the differential receiver allows a reduction of the common mode voltage. This technique can provide protection against extreme DC voltages and can be useful for board-to-board or system-to-system interfaces. An example of such an interface is shown in Figure 6. AC coupling of links that have long idle periods, or where the signal is not DC balanced (the number of 1s and 0s average over time is not equal) might not be suitable. Also, the low frequency cut-off point of the high-pass filter formed by the series capacitor and receiver termination must be significantly lower than the minimum spectral frequency content, or data loss can occur. The component values shown in Figure 6 are suitable in applications where the minimum significant spectral content is about 1 MHz. 4 www.BDTIC.com/XILINX www.xilinx.com XAPP696 (v1.3) May 1, 2008 R Conclusion Standard (non Xilinx) 3.3V LVPECL Driver DC 50Ω 50Ω DC VCCO–2.0V Z0 = 50Ω 0.1 μF 100Ω 100Ω 2.5V Virtex-II Pro/X FPGA 2.5V LVPECL/LVDS, or Spartan-3/3E FPGA LVDS Receiver + + Z0 = 50Ω – 0.1 μF – 100Ω 100Ω X696_06_042308 Figure 6: 3.3V LVPECL to 2.5V Differential Receiver AC-Coupled Interface Driver VCCO Reduction The common mode output voltage can be reduced to a low enough level by reducing the driver VCCO value. This option can be evaluated by running an IBIS or SPICE simulation, or by bench testing. Conclusion Virtex-II Pro and Spartan-3/3E FPGA differential receivers typically cannot directly receive LVPECL 3.3V levels using standard 100Ωparallel receiver termination. However, by utilizing custom AC or DC-coupled termination schemes, such an interface can be effectively implemented. The LVPECL driver output voltage device specification should always be considered, and IBIS or SPICE simulation should be performed to determine the optimal interface termination scheme. Revision History The following table shows the revision history of this document. Notice of Disclaimer XAPP696 (v1.3) May 1, 2008 Date Version Revision 05/21/04 1.0 Initial Xilinx release. 03/07/05 1.1 Typographical edit. Updated Figure 3 and Figure 4. 01/25/08 1.2 Added references to Virtex-4, Virtex-5, and Spartan-3E FPGA families. 05/1/08 1.3 Updated Figure 4. Xilinx is disclosing this Application Note to you “AS-IS” with no warranty of any kind. This Application Note is one possible implementation of this feature, application, or standard, and is subject to change without further notice from Xilinx. You are responsible for obtaining any rights you may require in connection with your use or implementation of this Application Note. XILINX MAKES NO REPRESENTATIONS OR WARRANTIES, WHETHER EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, INCLUDING, WITHOUT LIMITATION, IMPLIED WARRANTIES OF MERCHANTABILITY, NONINFRINGEMENT, OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT WILL XILINX BE LIABLE FOR ANY LOSS OF DATA, LOST PROFITS, OR FOR ANY SPECIAL, INCIDENTAL, CONSEQUENTIAL, OR INDIRECT DAMAGES ARISING FROM YOUR USE OF THIS APPLICATION NOTE. www.BDTIC.com/XILINX www.xilinx.com 5