* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Chapter 1: A Tour of Computer Systems

Survey

Document related concepts

Transcript

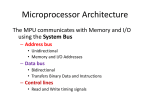

Chapter 1: A Tour of Computer Systems Bryant & O’Hallaron printf.o hello.c Source program (text) Prehello.i processor (cpp) Modified source program (text) Compiler hello.s (cc1) Assembly program (text) Assembler hello.o (as) Relocatable object programs (binary) Linker (ld) hello Executable object program (binary) CPU Register file PC ALU System bus Memory bus Main memory I/O bridge Bus interface I/O bus USB controller Mouse Keyboard Graphics adapter Disk controller Display Disk Expansion slots for other devices such as network adapters hello executable stored on disk CPU Register file PC ALU System bus Memory bus Main "hello" memory I/O bridge Bus interface I/O bus USB controller Mouse Keyboard User types "hello" Graphics adapter Disk controller Display Disk Expansion slots for other devices such as network adapters CPU Register file PC ALU System bus Memory bus "hello,world\n" Main memory hello code I/O bridge Bus interface I/O bus USB controller Mouse Keyboard Graphics adapter Disk controller Display Disk Expansion slots for other devices such as network adapters hello executable stored on disk CPU Register file PC ALU System bus Memory bus Main "hello,world\n" memory hello code I/O bridge Bus interface I/O bus USB controller Mouse Keyboard Graphics adapter Disk controller Display "hello,world\n" Disk Expansion slots for other devices such as network adapters hello executable stored on disk CPU chip Register file Cache memories ALU System bus Bus interface I/O bridge Memory bus Main memory L0: Regs Smaller, faster, and costlier (per byte) storage devices L1: L2: CPU registers hold words retrieved from cache memory. L1 cache (SRAM) L1 cache holds cache lines retrieved from the L2 cache. L2 cache (SRAM) L2 cache holds cache lines retrieved from L3 cache L3: L3 cache (SRAM) L3 cache holds cache lines retrieved from memory. Larger, slower, and cheaper (per byte) storage devices L4: L5: Main memory (DRAM) Main memory holds disk blocks retrieved from local disks. Local secondary storage (local disks) Local disks hold files retrieved from disks on remote network servers. L6: Remote secondary storage (distributed file systems, Web servers) Application programs Software Operating system Processor Main memory I/O devices Hardware Processes Virtual memory Files Processor Main memory I/O devices Process A Process B Time read User code Kernel code Disk interrupt Return from read Context switch User code Kernel code User code Context switch Kernel virtual memory Memory invisible to user code User stack (created at runtime) Memory mapped region for shared libraries printf function Run-time heap (created by malloc) Read/write data Read-only code and data 0x08048000 (32) 0x00400000 (64) 0 Loaded from the hello executable file CPU chip Register file PC ALU System bus Memory bus Main memory I/O bridge Bus interface Expansion slots I/O bus USB controller Mouse Keyboard Graphics adapter Disk controller Network adapter Disk Network Monitor 1. User types "hello" at the keyboard 5. Client prints "hello, world\n" string on display Local telnet client 2. Client sends "hello" string to telnet server 4. Telnet server sends "hello, world\n" string to client Remote telnet server 3. Server sends "hello" string to the shell, which runs the hello program, and passes the output to the telnet server All processors Multiprocessors Uniprocessors Multicore Hyperthreaded Processor package Core 0 Core 3 Regs L1 d-cache Regs L1 i-cache … L2 unified cache L1 d-cache L1 i-cache L2 unified cache L3 unified cache (shared by all cores) Main memory Virtual machine Processes Instruction set architecture Virtual memory Files Operating system Processor Main memory I/O devices