* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Device level

Invention of the integrated circuit wikipedia , lookup

Carbon nanotubes in photovoltaics wikipedia , lookup

Power electronics wikipedia , lookup

Thermal runaway wikipedia , lookup

Automatic test equipment wikipedia , lookup

Electronic engineering wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Radio transmitter design wikipedia , lookup

Surge protector wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Power MOSFET wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Night vision device wikipedia , lookup

Opto-isolator wikipedia , lookup

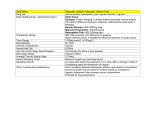

Total Dose Effects on Devices and Circuits -Principles and Limits of Ground Evaluation- Outline Sensitive structures and degradation processes Rules for effective device selection Limits of total dose evaluations Total Dose Effects on Devices and Circuits 2 Problematic of total dose ground evaluation Impossible to reproduce in-orbit device environment radiative environment complexity operating conditions(bias, temperature) Necessary to understand the physics to establish rules to extrapolate from ground to space Need of realistic data for non-hardened devices (COTS) Total Dose Effects on Devices and Circuits 3 One answer: reasonable conservativity Conservative conditions to assure that: a satisfying behaviour during device evaluation implies a satisfying in-orbit behaviour “Reasonable” for “not too much” These conditions must be defined regarding each experimental parameter modifying the device degradation Irradiation nature Dose rate/experiment duration Device bias and temperature Total Dose Effects on Devices and Circuits 4 Sensitive structures (Si technologies) nMOS transistor NPN bipolar transistor Surface passivation oxide Gate oxide Interface n+ n+ p-type Si substrate Interface n+ emitter p-type base n-type collector Total Dose Effects on Devices and Circuits 5 MOS structure degradation mechanism Gate (Vg) +-+- +-+-++-+-++- +- +++Oxide +- +- +- +- +-+- E +- +- +-+-+- ++- +- +-+++ Interface +++-+- ++- +Silicon +- +- +- +-+- + - +++ ++ + + ++ - - -+-- - Energy Total Dose Effects on Devices and Circuits 6 Ideal nMOS transistor Gate (Vgs) 0.4 0.3 Vth Ids (A) Gate oxide 0.2 Drain Source 0.1 p-type Si substrate 0 2 Total Dose Effects on Devices and Circuits 7 3 Vgs (V) 4 5 Ideal nMOS transistor: total dose D - Oxide trapped charge-induced degradation Vth 0.4 Gate (Vgs) Ids (A) 0.3 0.2 + + + ++ + + ++ ++ + ++ +++ + + - - - Drain - Source 0.1 0 2 Q Qit Vth ot Cox With h, fractional yield Qot .h.D Total Dose Effects on Devices and Circuits 3 Vgs (V) 4 8 5 Fractional yield dependencies Worst case regarding two parameters: 1- Nature of ionising source: Electrons or Co60 2- Electric field in sensitive oxide: Maximum value After Ma T.P., Dressendorfer P.V. (1983) Total Dose Effects on Devices and Circuits 9 Ideal nMOS transistor: stable state - Effect of oxide trapped charge annealing 0.4 Gate (Vgs) Ids (A) 0.3 - - - - - - Drain 0.2 Vth Source 0.1 0 2 3 Vgs (V) 4 - Theoretical condition: infinite post irradiation time - Practical conditions: 168 hours at 100°C is a compromise for large oxide charge annealing and slight interface traps annealing Total Dose Effects on Devices and Circuits 10 5 Parameter variation nMOS ideal case: time-dependant effect (TDE) -Qit 0 Vth tir tpi -Qot End of ground irradiation state Possible in-orbit Stable state states Interface states growth Total Dose Effects on Devices and Circuits 11 Parameter value Selection of MOS circuits x x: Measured values x : Specified limits PASS x x x x tpi D A device is selected if all the measurements are in the specified domain Total Dose Effects on Devices and Circuits 12 Selection of MOS circuits Parameter value x: Measured values x x : Specified limits x x x FAIL x tpi D Failure due to oxide trapped charge Total Dose Effects on Devices and Circuits 13 Selection of MOS circuits Parameter value x: Measured values : Specified limits x x x x x FAIL x tpi D Failure due to interface traps Total Dose Effects on Devices and Circuits 14 Ideal nMOS sensitive parameters (1) 0.4 Initial 100 Gy(Si) Circuit level Logic levels Propagation delays High speed performances 200 Gy(Si) 0.3 168h at 100°C Ids (A) Device level Threshold voltage (~ linear) Drive current Carrier mobility (second order) 0.2 0.1 0 2 Total Dose Effects on Devices and Circuits 15 3 Vgs (V) 4 5 Ideal nMOS sensitive parameters (2) 1 10-2 Ids (A) 10-4 Device level Leakage current (superlinear) 10-6 10-8 Initial 100 Gy(Si) 10-10 200 Gy(Si) Circuit level 10-12 Supply current (superlinear) 0 Design-dependant parametric degradation 168h at 100°C 1 2 3 Vgs (V) Leakage current Total Dose Effects on Devices and Circuits 16 4 5 Bipolar transistors degradation (1) Surface passivation oxide + + -+ ++- ++-+ +- + - +-+ Emitter Base Recombination rate in the emitter-base junction is modified: 1- In Si: surface potential shift induces change in the carrier densities 2- At the SiO2/Si interface: by the interface traps density increase and change in carrier densities The global resulting degradation strongly depends the transistor structure (design and type) and of the experimental conditions Total Dose Effects on Devices and Circuits 17 Bipolar transistors degradation (2) 100 60 The recombination fraction of the baseemitter current do not participate to the current amplification: 40 - The current gain (IC/IB) decreases Current gain (A/A) - 80 Initial 100 Gy(Si) 20 - The current gain degradation depends on VBE (non-linear effect) 200 Gy(Si) 500 Gy(Si) 0 0.4 0.5 0.6 VBE (V) 0.7 0.8 - Device level: Gain degradation has important impact in linear circuits - Circuit level: Leakage currents are induced in all circuit types Total Dose Effects on Devices and Circuits 18 Enhanced Low Dose Rate Sensitivity (ELDRS) - True dose rate effect - * Specific to bipolar technologies * Fractional yield dependence to dose rate (# from TDE) * No satisfying experimental method to bound its magnitude After Johnston et al. IEEE TNS (1994) Total Dose Effects on Devices and Circuits 19 Parameter value Selection of bipolar devices x: Measured values x : Specified limits x No signification: May be omitted x x x x PASS tpi D A device is selected if all the measurements are in the specified domain Design margins are recommended High dose rate at room temperature prohibited Total Dose Effects on Devices and Circuits 20 Main I.C. degradation mechanism - Leakage currents in isolating structures - Calculated current density at the silicon surface Z Z Drain Gate X X Total Dose Effects on Devices and Circuits 21 Source Standards for ground evaluation: Irradiation conditions - Worst-case conditions to test oxide charge-related failures Method SCC 22900.4 MIL 1019.6 Source Dose rate Bias Co or electron Standard: 36 to 360 Gy/h Worst case accelerator Low rate: 0.36 to 3.6 Gy/h 60 Co 50 to 300 rad/s Worst case (1800 to 10800 Gy/h) 60 -Maximum electric field in sensitive zones (fractional yield) -Avoid chip heating (thermal annealing) Higher fractional yield Compromise between: - benefit of TDE (annealing during irradiation) - cost of time consuming experiments Total Dose Effects on Devices and Circuits 22 Standards for ground evaluation: Post-irradiation conditions - Worst-case conditions to test interface traps-related failures Method SCC 22900.4 MIL 1019.6 Room temperature 24 h Time<D/Rmax Over test Accelerated annealing None 0.5xD (default) 168 h at 100°C 168 h at 100°C Bias Worst case Worst case Something simple ! SCC: time for Nit to reach maximum MIL: time less then irradiation time to anneal in the intended use One bias board only MIL: +50% of design margin (compensates possible Nit annealing) Total Dose Effects on Devices and Circuits 23 Displacements/ionisation cumulative effect - Dark current in Active Pixel Sensor Protons create ionisation (in SiO2) and displacements (in Si) Both interaction type can induce dark current 1010 protons/cm² Total Dose Effects on Devices and Circuits 24 Displacements/ionisation combined effects: Bipolar circuits After Rax et al. IEEE TNS (1998) A really extreme example of proton-induced fa ilure, but - a smaller effect can reduce bipolar technologies hardness, - RH means “PTDH” (Pure Total Dose Hard) Total Dose Effects on Devices and Circuits 25 Summary Ground evaluation of total dose effects are well defined and can assure devices hardness for most of device technologies device types mission profiles Some specific devices or applications need particular attention Necessary to study effect of device scaling Total Dose Effects on Devices and Circuits 26