* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download AIDA design review

Survey

Document related concepts

Transcript

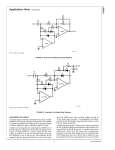

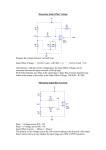

AIDA design review Davide Braga Steve Thomas ASIC Design Group 31 July 2008 Overview - x10 stage amplifier - Peak Hold circuit - Power supply stabilization - Bias circuit – 8 bit DACs - Offset (statistical analysis) and comparator threshold 31 July 2008 AIDA design review 2 Single channel simulation 31 July 2008 AIDA design review 3 Peak Hold Shaper_out • nMOS & pMOS Peak Hold in parallel, for both signal polarities • use of 5V transistors with low leakage to allow read out in ~ms time scale (~0.25V/s droop) pMOS PH Hold Reset Enable_pPH nMOS PH Hold 31 July 2008 Reset Enable_nPH AIDA design review 4 Peak Hold: linearity pMOS PH nMOS PH Good integral non-linearity over wide voltage range for both architectures 31 July 2008 AIDA design review 5 Peak Hold: minimum detectable signal • Minimum detectable signal affected by input offset • pMOS PH: nMOS PH: ~10mV ~4mV Input offset 31 July 2008 AIDA design review 6 Low Energy Channel 31 July 2008 AIDA design review 7 Bias circuit: current Biasing optimized to limit the current variation, but when preAmp output below ~200mV big change in current. For better power supply stabilization may be appropriate to limit ref_low to 200mV (→1.4V output swing) 31 July 2008 AIDA design review 8 Bias circuit References Several internal reference voltages need to be selectable in order to adjust the operating point of the circuit for the best performance 3 2.5 2.4 [V] 2 2 1.6 1.5 1.2 1 1 1 0.8 0.5 0 0.1 • preAmp input reference • Shaper/PeakHold reference • Shaper bias • preAmp bias 31 July 2008 AIDA design review 9 Bias circuit: 8bit DAC nMOS (up to Vdd) and pMOS (down to gnd) DAC for voltage setting Also comparator threshold must be selectable 31 July 2008 AIDA design review 10 Offset (Monte Carlo results) R 9R preAmp Shaper X10 stage • Offset preamp: σ~0.5mV • Offset shaper: σ~2mV • Offset x10 stage: σ~3mV • Offset comparator: σ~30mV! 31 July 2008 comparator (AC coupled to shaper, does not propagate to comparator) (~ 10 times offset previous stage!) AIDA design review 11 Offset Shaper input offset 31 July 2008 x10 stage in.offset AIDA design review Comparator in.offset 12 Offset reduction Some kind of offset cancellation technique must be implemented to achieve required comparator sensitivity X10 stage comparator comparator threshold: example of offset reduction technique 0.25%-10% FSR → after x10 stage 2.5%-100% FSR≈1.5V → ≈37.5mV 31 July 2008 AIDA design review 13 Conclusion - complete channel analog/digital simulation to be completed soon - next submission dates: end of September, end of October - limitations to low threshold operation identified, to be improved in a second iteration to avoid further delay -September timescale still feasible if layout straightforward 31 July 2008 AIDA design review 14