* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Summary - Intrel

Superheterodyne receiver wikipedia , lookup

Oscilloscope history wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Negative resistance wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Integrating ADC wikipedia , lookup

Index of electronics articles wikipedia , lookup

Phase-locked loop wikipedia , lookup

Surge protector wikipedia , lookup

Power MOSFET wikipedia , lookup

Current source wikipedia , lookup

Wilson current mirror wikipedia , lookup

Power electronics wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Regenerative circuit wikipedia , lookup

Radio transmitter design wikipedia , lookup

Voltage regulator wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Schmitt trigger wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mixing console wikipedia , lookup

Current mirror wikipedia , lookup

Operational amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

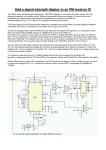

Memo.................. Box 1247, Nashua, NH 03061 [email protected] Tel: (603) 883-4815 mea_mix_sys_bal_sum_circuit-oh0.odt Created: 10-Jun-09 Mechanical Expansion Amplifier (US Patent 7,707,896) c 2012, James A. Kuzdrall, Some rights reserved. s b d Auto-Balance using Synchronous Detection, for MEA Sub-Millimeter Homodyne Mixers To: file Table of Contents 1.0 Circuit Description...........................................................2 2.0 Circuit Design ...............................................................5 2.1 Auto-Balance Input Subtracter OC01 R01 R02 R03 R04......................5 2.2 Loop Gain Requirement...................................................7 2.3 Synchronous Detector C03 C04 R08 U01....................................7 2.4 Clock Buffer Q01 R09 R10................................................8 2.5 Preamp A01a A01b C01 C02 DD01 R05 R06 R07...............................9 2.6 Loop Gain Amplifier A02 R11 R12 R13....................................10 3.0 Performance Results..........................................................11 4.0 Parts Summary................................................................11 Summary Local Oscillator (LO) noise is potentially the dominant noise in the MEA thermal homodyne mixer. However, much of the noise can be eliminated using the balanced mixer technique common in radio receivers at lower frequencies. The polarization-balanced mixer provides a practical solution for sub-millimeter microwave frequencies. Since the polarization technique has very good short time (seconds) stability, nulls are possible that are beyond the resolution of a manually adjusted potentiometer (about 1 in 3600). The circuit designed here autonomously provides resolutions on the order of 1 in 20,000. The circuit requires that the LO be modulated with a low-level marker which will be used to null the mixer balance. The marker frequency is about 10 times lower than the normal bandwidth limit of the homodyne mixer. At that frequency separation, the phase shift is -5.7 degrees. It is changing slowly with frequency and therefore is less affected by small differences in the bandwidths of the two mixers. Normal bandwidths range from 10Hz to 20KHz. 1/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 1/11 Automatic Nulling for Balanced Mixers The modulation depth of the marker is 20db greater than the oscillator noise level at the modulation frequency. Although the frequency is within the signal band, it will be nulled to a level below the noise level. Note that the oscillator noise level on which the modulation depth is based will decrease with the marker as the null deepens. The synchronous detector in the nulling circuit has a narrower bandwidth than the normal signal processing, allowing the marker to be suppressed below the signal processing noise level. 1.0 Circuit Description Figure 1 shows the circuit. It comprises 4 cascaded function blocks: 1. Input Auto-Balance Subtracter a) OC01 R01 R02 R03 R04 2. Preamp a) A01a A01b C01 C02 DD01 R05 R06 R07 3. Synchronous Detector a) C03 C04 Q01 R08 R09 R10 U01 4. Loop Gain Amplifier a) A02 Q02 R11 R12 R13 Figure 1: Circuit Diagram Auto-Balance Subtracter: The mixer outputs enter at Mixer A and Mixer B. A clock that is synchronous with the marker modulation enters at LO Marker Clock. The mixer signals must be phased correctly with respect to the clock signal; if they are not, the gain correction will go in the wrong direction. 2/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 2/11 Automatic Nulling for Balanced Mixers The LO signals from Mixer A and Mixer B are out of phase, but one may have a slightly higher gain than the other. OC01 is a photoresistor whose resistance is controlled by an LED. R04 keeps the drive current to the LED from exceeding the rated maximum. The series combination of the mid-range resistance of OC01 plus R01 in parallel with R02 equal the resistance of R03. Preamp: Preamp A01a buffers the relatively high impedance of the Subtracter to provide an output, Mixer Output, with about the same gain as the mixers themselves. R05 sets and inverting gain of one. The second amplifier stage, A01b, contributes to the forward gain of the feedback loop. It also mitigates the error caused by supplying bias current to A02 through the Synchronous Detector resistance R08. R06 and R07 set the non-inverting gain of A01b. C01 and C02 provide local power supply bypass. Synchronous Detector: Q01 buffers the synchronous clock and accepts a wide range of logic levels. R09 references the FET gate to ground when the line is open circuit. R10 is the load resistor, producing a 0 to +5V clock for U01. U01 is a triple 2-input analog data selector. Internal circuitry translates the 0V (Vss) to +5 (Vdd) input logic level to the +5V to -5V (Vee) levels needed by its transmission gates. When one gate is ON, the other is OFF. All 3 selectors are connected in parallel. C03 and C04 are equal. R08, C03, and C04 determine the bandpass or filter time constant of the detector. The time constant equals 3*R08*C03 for this circuit. Synchronous detector operation review: To review how the synchronous detector works, assume that a high mixer gain at Mixer A has created a marker sine wave at the output of A01b. The marker signal from A01b happens to be in phase with the LO Marker Clock. For a high LO Marker Clock (and positive half sine wave from A01b), the Q01 output is low, connecting the grounded (x) input of U01 to C03. The positive voltage from A01 charges C03 through R08. Since U01 is holding the its end of C03 at ground, the charging produces a negative voltage on the U01 end of C03 with respect to the A01b end. The resistance of R08 is too high to charge C03 to the drive voltage in one half-cycle. [Note that, while the half-sine charging voltage is always positive, it varies from zero, to a positive peak, and back to zero. The charging current varies over the half cycle. Each half cycle charges C03 a little, until the voltage on C03 is such that the end portions of the charging half-sine draw as much current out of C03 as the middle peak portion puts in. At that point, the DC voltage on C03 is equal to the 3/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 3/11 Automatic Nulling for Balanced Mixers mathematical average voltage of a half sine wave, .9 times the RMS voltage or about .63 times the peak voltage.] On the negative half cycle, U01 connects C03 to C04. The voltage from A01b is a negative half sine wave. R08, C03, and C04 are in series. C03 has acquired a charge which makes its A01 end positive with respect to the end connected to C04. Its negative voltage adds to that of A01b. Consequently, the negative voltage charging C04 through R08 is higher by the average voltage of a half sine wave. As in the case of C03, R08 is too large to charge C04 to the A01b output voltage immediately. Eventually, however, it will charge C04 to the average value of the negative half sine wave plus the average value of the positive half, or a DC value of 1.8 times the RMS voltage of the A01b imbalance output. The bandwidth of the synchronous detector in Hertz is fbw= 1/ (2*pi*3*R08*C03), where the capacitance of C03 and C04 are equal. The pass band extends to Fbw on either side of the drive frequency. Consequently, the noise bandwidth is √2*Fbw. (There is a signal sideband on both sides too.) The bandwidth is a factor of 3 narrower than one might expect. The reason may be understood intuitively. The time for the positive half cycle to charge C03 is proportional to R08*C03. But, C03 only charges for half of the time, so the total time to fully charge is 2*R08*C03. On the negative half cycle, the time to discharge C03 and charge C04 involves two equal capacitances in series; their effective capacitance is half that of either. Consequently, the positive half-cycle charge time constant is R08*(C03/2). Again, the time to fully charge is longer by a factor of 2 because charging takes place only half of the time. The total negative half cycle charge time is proportional to 2*R08*C03/2= R08*C03. Adding the two charge times, 2*R08*C03+R08*C03= 3*R08*C03. Loop gain amplifier: A02 is a DC voltage amplifier. It provides the gain for the feedback loop. R12 and R13 set the gain. R11 keeps the bias current from the A02 input from building up a large voltage on C04 if the Clock is not present. The synchronous detector would take a long time to bring C04 back to ground if it got too far from zero volts. A very high gain reduces the residual marker signal the furthest at null, giving a better balance. Two conditions may limit the allowed gain. First, the resistance of the opto-coupler is very nonlinear with respect to the LED control current; too much gain will produce oscillation. Second, when the gain is adequate to reduce the signal-to-noise ratio at A01a to 1, there is no further benefit in more gain. 4/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 4/11 Automatic Nulling for Balanced Mixers 2.0 Circuit Design Some design decisions require details of the mixer requirements. The following assumptions should be fairly typical. Insert the appropriate conditions for your design in the calculations which follow. Parameter Min Mixer noise at 10Hz (without LO noise) Mixer signal output range Nom Max .3 300e-9 Local Oscillator (LO) noise sideband level uV/√Hz 30e-3 Vrms 3000 uV/√Hz Mixer gain imbalance Resistive load ±20 % 5.0 K ohms Mixer output voltage (non-operational) Mixer bandwidth ±14 V 2250 2500 2750 Hz 250 Hz 30 mV 6 mV Marker frequency Marker amplitude, at each mixer Marker amplitude, worst case imbalance Required marker suppression at null Ambient temperature Units -86 15 db 25 35 ¡C Table 1: Design Specifications Example 2.1 Auto-Balance Input Subtracter OC01 R01 R02 R03 R04 The opto-coupler, OC01, is the key part and must be chosen first. A suitable and available part is the Silex NSL32, similar to the once popular Clairex CLM6000. The practical resistance range is 400 to 16K ohms, from the data sheet graph. The midpoint is sqrt(400*16K)= 2530 ohms. The required adjustment range, adj_rng, is ±20% minimum for this application. Operate OC01 from minimum to maximum resistance while covering the adjustment range. This gives its nonlinear "gain" the least contribution to the total gain of the loop. If so, the relationship between R01 and R02 is: Relationship equations: (r01+roc_max)*r02/(r01+roc_max+r02)= (1+adj_rng)*rn= 1.2*rn (r01+roc_min)*r02/(r01+roc_min+r02)= (1-adj_rng)*rn= .8*rn Solving for R01: 5/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 5/11 Automatic Nulling for Balanced Mixers R01 = ((sqrt(5)*sqrt(5*(roc_min)^2+(-10*roc_max-48*rn)*roc_min +5*(roc_max)^2 +48*rn*roc_max)-5*roc_min-5*roc_max)/10) Evaluate with: rn:10.0K, roc_min:400, roc_max:16.0K: R01 = 12662.4 -> 12.7K 1% metal film Substitute R01 in the first equation and solve for R02: r02 = ((6*rn*roc_max+6*r01*rn)/(5*roc_max-6*rn+5*r01)) Evaluate with: rn:10.0K, roc_min:400, roc_max:16.0K, R01:12662.4 r02 = 20642.2 -> 20.5K 1% metal film If the mixers happen to be balanced, the resistance of OC01 should be at its geometric mean, roc_mid= sqrt(16K*400)= 2530 ohms. R03 must equal the resistance of the Mixer A input branch under these conditions. R03 = (r01+roc_mid)*r02/(r01+roc_mid+r02) = (12.7K+2530)*20.5K/( 12.7K+2530+20.5K) = 8738 -> 8.66K 1% metal film R04 limits OC01's LED current to a safe level. The rated maximum is 40mA. On the other hand, the current required to reach the minimum OC01 resistance is 20mA. The minimum resistance for R04 gives a current no greater than 40mA if the LED drop were zero and the Q02 negative output reached the -5V supply: R04 > 10V/40mA= 250 ohms. The maximum resistance at R04 must is maximum and the Q02 output does not drop is 2V. Allow 1.0V across PNP Q02 rail-to-rail input and output device. ohms. assure that 20mA flows when the LED drop reach the -5V supply. The maximum LED when saturated, assuming A02 is a typical The maximum R04 is (10V-2V-1V)/.02A= 350 Choose the mid-value resistance for R04, 300 ohms, 5%. Part Value Description OC01 Pkg - Mfgr Mfg_nr Note SILEX NSL32 R01 12.7K RES 10-2.2M 1% .125W mf 1206 PANINDU ERJ-8ENF1272V 135 R02 20.5K RES 10-2.2M 1% .125W mf 1206 PANINDU ERJ-8ENF2052V 135 R03 8.66K RES 10-2.2M 1% .125W mf 1206 PANINDU ERJ-8ENF8661V 135 R04 300 *0.0-6.2M 5% .25W CF 1206 PANINDU ERJ-8GEYJ301V 93 Table 2 Auto-Balance Input Subtracter Parts Summary 6/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 6/11 Automatic Nulling for Balanced Mixers 2.2 Loop Gain Requirement The remaining function blocks depend on the loop gain of the circuit. What loop gain is needed to suppress the LO noise to the inherent mixer noise level? Calculate the "gain" blocks along the feedback path: The balance arm resistance adjustment resolution for a -86db null is: droc = (drn * (roc_nom + r02 + r01)^2)/(r02^2) For: drn=8660/20000 (for 86db suppression), roc_nom= 2530, r01= 12.7K, r02= 20.5K: droc = 1.31536 ohms At mid-resistance, the NSL32 opto-resistor (OC01) changes about 1000 ohms for a 200uA change in LED current. The LED current change for 1.3 ohms is 200uA*1.3/1000= 0.260uA. The voltage change across R04 that results in a 260nA current change is 260uA*R04= 260uA*300= 78uV. The gain needed to bring the 300nV inherent mixer noise to 78uV is 78uV/300nV= 260. 2.3 Synchronous Detector C03 C04 R08 U01 The synchronous detector other of two inputs. Either because both contain a level the clock to the Vdd to -Vee requires switches that alternately select one or the a 74HC4053 or a CD4053 would make a good choice converter that extends the 0V to Vdd logic level of level needed to control the analog switches. The 74HC4053 has a lower, but adequate operating voltage range than the CD4053. It happens to also have a lower ON-resistance, but either is adequate. Choose the 74HC4053. Although the circuit requires only one selector pair the package contains 3. Rather than leave two unused, connect all three in parallel. The tripled input capacitance and leakage is not an issue at these low frequencies. Filter bandwidth: The pole created by the synchronous detector RC filter (R08 C03 C04) has two criteria to meet: First, to get adequate ripple filtering, the the RC filter should be 100 times longer than the signal period. For the 250Hz marker frequency, the filter pole would be at 2.5Hz. Second, the filter pole must not interact with the slow, nonlinear transfer function of the photoresistor, OC01. The photoresistor has a small-signal pole at about 8.0Hz (-45 degree phase shift). To avoid oscillation, the RC filter must bring the loop gain of 260 down to 1.0 at 8Hz, making its pole frequency 8Hz/260= 31mHz or a time constant of 1/(2*pi*31mHz)= 5.1s. 7/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 7/11 Automatic Nulling for Balanced Mixers The second criterion is the most stringent, to it determines the design. Since the pole location of the photoresistor is not precise, increase the time constant by 2x to 10.0 seconds to provide a tolerance margin. R08 can be as high as a few megohms, putting C03 and C04 in the 10uF range. There is a reason, however, for making the capacitance as large as practical. Any bias current required by A02 must be supplied through R08. The voltage drop caused by the bias current limits the null that can be achieved. [Bias current through R08? Why not through R11? Well, if R11 is made lower than R08, the voltage on C04 will not reach its full value. Consider R11 infinite. On each cycle, the A02 bias current is drawn from C04, changing its voltage. The lower voltage on C04 causes a change in the photoresistor, which in turn, changes the signal level into the synchronous detector. At equilibrium, the residual marker signal into the synchronous detector is just large enough to recharge C04 of every cycle. The nulled marker must somewhat higher than the level calculated for the loop.] The reduce the amount of residual marker needed to supply A02 bias current, choose A02 for low bias current, make C04 large so the voltage changes less for the current drawn (and the resistance of R08 is lower), and amplify the marker as much as possible before it reaches the synchronous detector. C03 C04 R10: A 10 second time constant is long, so the capacitance should be as large as practical. Film capacitors have the best leakage, dielectric absorption, and capacitance stability, but they are very bulky. Multilayer ceramic is the next best choice. The preferred ceramic is NP0, but it does not have a high enough dielectric constant to reach the required capacitance level. The X7R is the next best choice. Use a 10.0uF 16V 1206-size surface-mount for both capacitors, Panasonic ECJ3YX1C106K. The minimum insulation resistance is 50M ohms at 125¡C. To get the 10 second time constant, use a 1.00M ohm 1% metal film resistor for R08. 2.4 Clock Buffer Q01 R09 R10 The requirements for the Q01 N-channel MOS-FET are not very demanding. A 2N7002 is satisfactory. Use Diodes 2N7002 60V .115A 7.5 ohms@5Vgs 2.5Vth (Ref. 91). R09: R09 keeps Q01 OFF when there is no connection to the LO Marker Clock input. The highest resistance it can have is that which keeps the gate leakage from generating a voltage equal to the typical turn-ON threshold, 1 volt. The maximum gate leakage is 100nA. R09< 1V/100nA= 10M ohms. 8/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 8/11 Automatic Nulling for Balanced Mixers The drive capability of a CMOS gate determines lowest value for R09. The CD4000 family has the lowest high-level drive capability, 400uA. This drive must bring the R09 voltage up to the maximum 2N7002 threshold voltage, 2.5V: R09 > 2.5V/400uA= 6250. Use the geometric mean, R09= sqrt(6250*1e7)= 250K -> 100K ohms. R10 provides a threshold logic-high for U01 when Q01 is at its threshold drain current, 250uA. The threshold logic high for the 74HC4053 is 3.75V for Vcc= 5.0V. R10= 3.75V/250uA= 15K ohms. 2.5 Preamp A01a A01b C01 C02 DD01 R05 R06 R07 Opamp A01a restores a low source resistance for the Mixer Output after the resistive sumer. Opamp A01a: ✿ ✿ ✿ ✿ ✿ ✿ ✿ ✿ ✿ The requirements for A01a are not very demanding: Operating voltage: ±5V Common mode input range: no requirement Output voltage: rail-to-rail Output drive: > ±1.0mA (5K ohm load) Closed loop bandwidth: > 10*mixer_bw= 10*2.5KHz= 25KHz Gain: -1x Gain bandwidth product: > 1*25KHz= 25KHz Noise at 10Hz: < 100nV/√Hz Available in dual opamp package Both the AD820 and TLV272 are suitable as shown in Table 3. for lower cost and better availability. Parameter AD822ARZ TLV272IDBVR Cost each, 25 quantity ($) 3.16 .71 Relative availability (#) .9 31 Supply voltage, maximum (V) 36 16 9.835 9.91 Input noise at 10Hz (nV/Hz) 25 90 Gain-bandwidth product (MHz) 1.9 3 Input bias current (pA) 10 60 Input offset voltage (mV) 1 5 Output voltage, 5K load (Vpp) Use the TLV272 Table 3: A01 Opamp Candidates R05: 9/11 The input resistance at balance is 8.66K. R05 is 8.66K 1% metal film. mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 9/11 Automatic Nulling for Balanced Mixers DD01: If the input from the mixer is at a maximum, 14V, R05 saturates and cannot keep the inverting input near zero volts. The voltage can increase beyond the supply voltage, potentially damaging the opamp. DD01 clamps the input voltage to 600mV in the case of an input overload. The MMBD4148SE provides the function in an SOT-23 package. C01 C02: The relatively low frequency opamps do not require much bypassing. However, some must be included on the board in case the bypassed supply is at a distance. A 2.2uF surface capacitor is series resonant in the vicinity of the unity gain frequency of A01. Use tantalum capacitor 2.2uF 20% 16V in a 3216 surface-mount package, Nichicon F931C225MAA. A01b gain: A01b provides as much gain as possible to reduce errors caused by A02 bias current. From the specifications, the maximum expected input signal is 30mVrms from the mixers. Since these signals will add, the maximum input to A01b is 60mVrms or 2*sqrt(2)*60mV= 170mVpp. Since A01 has a rail-to-rail output, the output can be as high as 10Vpp. The maximum gain 10V/170mV= 59-> 50, making the maximum output 8.5Vpp. R06 R07: Keep the load on A01b light so it can drive rail-to-rail. 48.7K and R06 1.00K 1% metal film. Make R07 2.6 Loop Gain Amplifier A02 R11 R12 R13 The gain required of A02 is 260/50= 5.2x. The input bias current of A02 should be very small, allowing R11 to be much larger than R08. If R11 is small, it will change the bandwidth of the synchronous detector filter. CMOS opamps are good candidates for A02, but the offset voltage must not create a nulling error. The nulling resolution sought by the design is equivalent to an input noise voltage of 70uV. Since A01b has a gain of 50, A02 can have an input offset voltage as large as 70uV*50/3= 1.2mV, taking a third of the total 70uV error budget. The average bias current can cause an error on the order of 3.5mV/3 at A01b output. For R08 at 1.00M, the input bias current can be 3.5mV/(3*1.00M)= 1.2nA. The Analog Devices AD8661ARZ CMOS opamp that meets the requirements with Vos< 160uV and Ib< 1.0pA. It operates with voltages as high as 16V. 10/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 10/11 Automatic Nulling for Balanced Mixers R11: R11 supplies bias current to A02 when there is no synchronous signal present. If R11 were not present, the voltage on C04 would drift to the positive or negative supply in time, causing a long delay when the synchronous signal returns as R08 works on discharging C04 back down to zero volts. A 22 megohm resistor, the largest available thick film resistance, keeps C04 within 22e6*4e-12= 88uV of ground when there is no marker signal. It is also only 5% of the R08 resistance, keeping the synchronous filter accurate. R12 R13: The gain needed is about 5x. The largest value for R12 would be that for which the bias current causes a voltage drop equal to the offset voltage: R12 < Vos/Ib= 160uV/1pA= 160M ohms. R13 would be 4*160M= 640M. The largest current R13 should draw is that which increases the output saturation voltage to 400mV, 20mA according to chart 30 of the specifications. That would require R13 to be (5V-.4V)/20mA= 230 ohms. The geometric mean of the extremes is sqrt(230*640M)= 384K-> 365K, 1% metal film. R12 is R13/4 to get a gain of 5. R12= 365K/4= 91K-> 90.9K 1% metal film. Q02: A large amount of output current heats an opamp causing larger voltage offset and bias current errors. Any PNP transistor with a beta larger than 100 will do. Use the commonly available 2N2907A in an SOT-23 case. 3.0 Performance Results Here. 4.0 Parts Summary From 1966. 11/11 mea_mix_sys_bal_sum_circuit-oh0 Revised: 22-Aug-12 11/11