* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Time Domain Modeling of Pin Control and Limiter Diodes

Survey

Document related concepts

Transcript

TIME DOMAIN MODELING OF PIN CONTROL AND LIMITER DIODES

Robert H. Caverly and Michael J. Quinn

Department of Electrical and Computer Engineering

Villanova University

Villanova, PA 19085

ABSTRACT

A time domain model for the microwave and RF

PIN switching diode is presented. The model is

suitable for use in such time domain simulators

as SPICE and simulates the important I-region

charge storage phenomenon and its effect on the

PIN diode behavior in active circuits such as

switches, attenuators and power limiters. For a

SPST switch, the variation in PIN diode

impedance is shown to affect the insertion loss

in the switch. For microwave power limiters,

spike leakage variation versus frequency for

different RF voltages is also presented, showing

the reduction in power limiting with increasing

frequency for a given PIN diode.

1. INTRODUCTION

PIN diodes are used in a wide variety of

commercial and defense applications which

include antenna switching and attenuator

applications.

Microwave and RF design

engineers frequently use time domain simulators

such as SPICE or one of its derivatives for

computer aided design of microwave circuits

and systems using these devices. In spite of the

widespread use of PIN diodes in microwave and

RF circuits and systems, there has been slow

progress toward developing a time domain

model that adequately simulates the PIN diode.

One time domain model that has already been

advanced is strictly a current controlled

resistance with package parasitics [1]. This

model does not include such important effects as

I-region charge storage, which is the dominant

mechanism in governing such PIN diode

behavior

as

the

impedance-frequency

characteristic, or its transient response in

passive or quasi-active microwave power limiter

circuits.

This paper presents a model for the PIN diode

that allows time domain simulation using circuit

simulators such as SPICE. The model includes

both junction effects (making it suitable for dc

bias simulation) as well as low and high

frequency I-region charge storage and transient

phenomenon. The model will allow design

engineers to use SPICE or other time domain

CAD tools to perform simulation of PIN diodes

and ancillary circuitry such as switch drivers.

The model is easily embedded in more complex

circuits for use in full system simulation since it

uses standard SPICE and PIN diode electrical

parameters. Verification of the new model is

made by comparing analytic and experimental

results.

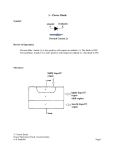

2. THEORETICAL DISCUSSION

The PIN diode is characterized by a lightly

doped intrinsic (or I-) region sandwiched

between heavily doped p-type and n-type

regions. The electrical structure arising from

this physical structure is of two PN-type

junctions on either end of a highly resistive

region (I-region) subject to conductivity

modulation by an applied dc forward current.

For time domain simulation, the PI and IN

junctions can be characterized by the usual PN

junction diode circuit elements. Modeling the Iregion is more problematic since this region

exhibits charge storage phenomenon due to

conductivity modulation which is manifested in

the charge-current (or Q-I) relationship. Several

circuit simulation models exist (APLAC and HP

LIBRA, for example) that have a PIN diode

element in their libraries, but none of these

CAD tools include I-region charge storage

effects. It is the I-region charge storage effect

that governs such PIN diode behavior as the

impedance-frequency characteristic, insertion

loss and limiter behavior.

The I-region charge storage phenomenon in PIN

diodes is described by the ambipolar carrier

transport equation:

0-7803-5135-5/99/$10.00 (c) 1999 IEEE

∂ 2 n( x , t ) n( x , t ) 1 ∂n( x , t )

(1)

=

+

dx 2

Daτ

Da

dt

This mathematical representation of the I-region

charge storage effect has been successfully

combined with the PN junction portions of the

PIN diode and implemented as an analytical

model [2-5]. Implementation of Equation 1 in

the time domain model is performed by applying

boundary value conditions and deriving the

stored charge-current relationship in the Iregion in the s-domain [6]. The resulting

SPICE implementation uses standard simulation

parameters and includes such effects as unequal

carrier mobilities (for silicon and gallium

arsenide PIN diode simulations) as well as

unequal junction characteristics.

The parameters in the time domain model are

common to other models [1-5]. In addition to

the standard PN junction simulation parameters

(reverse saturation current and the diode ideality

factor), the model requires knowledge of the Iregion width and ambipolar carrier lifetime.

Limiting resistance values Rmin (minimum high

current resistance) and Rmax (zero bias

resistance) are easily added [1]. Extrinsic

parameters such as junction and package

capacitances and bond wire inductances can be

included in the model.

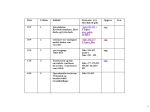

3. APPLICATIONS AND RESULTS

3.1 SPST Switch Application

Simulations using a commercial version of

PSPICE were performed to compare the model

described with previously published analytical

results [2-5]. Figure 1 shows the resistive and

reactive impedance components of a PIN diode

using the proposed model plotted with the

analytical results for a gallium arsenide device

with a 3 µm I-region width and 5.6 nanoseconds

carrier lifetime at 1 mA dc forward current [2].

Plotted with the simulated results are

experimental data (circles) taken on a PIN diode

with the same characteristics. The agreement

between the PSPICE and analytical results and

the experimental data is very good, validating

the model for use in simulating the PIN diode

impedance-frequency characteristic.

Impedance (Ohms)

Resistive Component

Reactive Component

Frequency (Hz)

Figure 1. Comparison of SPICE and analytical

models with experimental data (circles) for a gallium

arsenide PIN diode.

The impedance-frequency characteristic will

influence the insertion loss of a microwave and

RF circuit that uses this PIN diode as the control

element. Figure 2 shows simulated resistance

for a PIN diode (W=25 microns, τ=100 nS)

biased at 10 mA as a function of frequency,

indicating that the resistance monotonically

decreases up to 1000 MHz. Note that the diode

resistance varies from approximately 5 Ohms

down to 3.25 Ohms over the frequency range of

the switch. Figure 3 shows that the insertion

loss of a SPST switch using the above device

varies from approximately 0.4 dB at 10 MHz to

0.25 dB at 1000 MHz. Note that the insertion

loss curve tracks with the resistance curve,

indicating the change in insertion loss with

frequency is primarily caused by the diode and

not the dc biasing network (which was included

in the simulation structure).

0-7803-5135-5/99/$10.00 (c) 1999 IEEE

5

Load Voltage (V)

Spike Leakage

Turn off

0

Flat Leakage

-5

Time (nS)

Figure 2. Simulated resistance of the PIN diode

using the time domain model described in the paper.

Figure 4. Full waveform of two anti-parallel silicon

PIN diodes in a fully passive microwave limiter. The

10 volt RF pulse begins at 50 nS and ends at 150 nS.

Figure 5 summarizes the results of a number of

simulations for the 2 diode limiter, showing the

input/output power curve, indicating the

increase in flat leakage with increasing input

power.

Figure 3. Insertion Loss (dB) as a function of

frequency for the SPST switch shown in Figure 2A.

3.2 Limiter Application

PIN diodes are often used in applications that

limit the level of microwave voltage on sensitive

receiver components [7]. A major difficulty in

limiter modeling is describing spike and flat

leakage during the turn-on and turn-off

transients. The model described here was

applied to a 2 diode passive PIN diode limiter (Iregion thickness of 5 microns, carrier lifetime of

10 nS) with the diodes separated by 0.1λ

transmission lines. Figure 4 shows the response

of this circuit to a 10 volt 1.0 GHz microwave

pulse. The spike leakage is prominently shown

in Figure 4, with the simulation showing spike

leakage lasting

for

approximately 10

nanoseconds.

Figure 5. Input/output power curves for a 2 diode

antiparallel PIN diode limiter (same diode

characteristics as Figure 4).

Figure 6 shows limiter diode spike leakage

under three different microwave pulsed voltage

conditions as a function of frequency. The spike

leakage increases with frequency for a given

microwave voltage applied to the circuit. This

increase in spike leakage is due to the short RF

cycle of the higher frequency signals not

providing sufficient time for carriers to transit

the I-region and set up the high conductance Iregion.

0-7803-5135-5/99/$10.00 (c) 1999 IEEE

6. A. Strollo, “A New SPICE Model of Power P-I-N

Diode based on Asymptotic Waveform Evaluation”,

IEEE Trans. Power Electronics, vol. 12(1), pp. 1220, Jan. 1997.

7. A. Ward,; R. Tan, and R. Kaul, “Spike leakage of

thin Si PIN limiters”, IEEE Trans. Microwave Theory

and Tech., vol. 42(10), pp. 1879-1885, 1994.

7. APPENDIX

SPICE Subcircuit Template

Figure 6. Spike leakage (load voltage) for 5.0, 10.0

and 20.0 volt RF pulses as a function of frequency.

The simulations were performed with the same

circuit and PIN diodes as used for Figure 4.

4. CONCLUSIONS

A method has been presented for time domain

modeling of the PIN diode. Using this model,

microwave and RF engineers designing with

PIN diodes can readily use time domain circuit

simulators such as SPICE to study PIN diode

effects in circuits and systems more easily. The

new model has been validated using both

analytical

models

and

experimental

measurements.

5. ACKNOWLEDGMENT

This material is based upon work supported by

the National Science Foundation under Grant

No. CCR-9805718.

6. REFERENCES

1. J. Walston, “Spice Circuit yields recipe for PIN

diode”, Microwaves and RF, pp. 78-89, Nov. 1992

2. R. Caverly and G. Hiller, "The Small Signal ac

Impedance of Gallium Arsenide and Silicon PIN

Diodes," Solid-State Electronics, vol. 33(10), Oct.,

1990.

3. R. Caverly and G. Hiller, "The Frequency

Dependent Impedance of p-i-n Diodes”, IEEE Trans.

Microwave Theory and Tech., vol. 37(4), pp. 787790, April, 1989.

4. Lebedev, I.V.; Drozdovskaya, L.M.; Drozdovskij,

N.V.; Shnitkov, A.S., “Determination of the active

component of pin-diode impedance”, Radiotekhnika i

Elektronika, vol. 41(3), pp. 370-373, Mar., 1996.

5. R. Varshney, D. Roulston, and S. Chamberlain,

“Some properties concerning the a.c. impedance of PI-N and P-N-N+ diodes”, Solid-State Electronics, vol.

17, p. 699, 1974.

.subckt pin 9 20 params: is=1e-10,

+ n=1, ikf=3, phi=.7,

+ rlim=1.8m, repi=800k, cj=0.5pf,

+ tau=.116u, w=10u,

+ lbond=0.5nh, cpack=0.25pf

* b=3 for silicon; b=15 for GaAs

+ b=3

.param to={w*w/.001935/4}

.param v1={w*w/tau/0.1}

.param alf={to/tau}

.param npi={2*n/(1+b)}

.param nin={2*b*n/(1+b)}

cpack 9 20 {cpack}

lbond 9 10 {lbond}

cjunc 10 20 {cj}

repi 10 12 {repi}

rlim 10 11 {rlim}

grmod 11 12 value={2*(v(11,12)*v(2,3)/v1)}

gpin 12 20 value={i(vs2)}

rpin 10 20 1e12

ej 30 0 value={v(12,20)}

vs1 30 31 0

* two different junction models needed for

* Dember contribution

dpi 31 32 dj1

din 32 0 dj2

.model dj1 d (is={is},ikf={ikf},n={npi})

.model dj2 d (is={is},ikf={ikf},n={nin})

e1 1 0 value={i(vs1)}

vs2 1 2 0

* 6th order approximation for base region

rp1 2 3 1

cp1 2 3 {tau}

rs1 3 0 {alf/3}

rp2 3 4 5

cp2 3 4 {tau/5}

rs3 4 0 {alf/7}

rp4 4 5 9

cp4 4 5 {tau/9}

rs5 5 0 {alf/11}

.ends

0-7803-5135-5/99/$10.00 (c) 1999 IEEE