* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Power Sequence and Reset Utilizing the Intel EP80579 Integrated

Power factor wikipedia , lookup

Voltage optimisation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Wireless power transfer wikipedia , lookup

History of electric power transmission wikipedia , lookup

Standby power wikipedia , lookup

Electric power system wikipedia , lookup

Electrification wikipedia , lookup

Alternating current wikipedia , lookup

Audio power wikipedia , lookup

Power over Ethernet wikipedia , lookup

Distribution management system wikipedia , lookup

Mains electricity wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Microprocessor wikipedia , lookup

Power engineering wikipedia , lookup

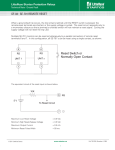

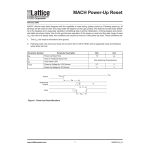

Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note December 2008 Author: Julio Pineda Order Number: 320471-001US INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Legal Lines and Disclaimers Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-5484725, or by visiting Intel’s Web Site. Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor_number for details. Intel, Intel logo, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, and Intel EP80579 are trademarks of Intel Corporation in the U.S. and other countries. *Other names and brands may be claimed as the property of others. Copyright © 2008, Intel Corporation. All rights reserved. Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 2 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset Contents 1.0 Introduction .............................................................................................................. 5 1.1 Reference Documents .......................................................................................... 5 1.2 Abbreviations...................................................................................................... 6 2.0 Core and Standby Power Supply Rails........................................................................ 6 3.0 Power Sequence With Suspend Power Management .................................................. 6 3.1 Implementation .................................................................................................. 9 4.0 Power Sequence Without Suspend Power Management ............................................. 9 4.1 Hardware Interface POR ..................................................................................... 11 5.0 Troubleshooting for POR.......................................................................................... 15 5.1 Power Supplies ................................................................................................. 15 5.2 Clock Synthesizer Enable.................................................................................... 15 5.3 Power Good and Power OK ................................................................................. 16 6.0 Conclusion............................................................................................................... 16 Figures 1 2 3 4 5 Suspend and Core Power Rail Sequence .......................................................................... 8 Core Power Rail Sequence (No Suspend) ....................................................................... 10 IspPAC Sequence Controller Interface ........................................................................... 12 Intel® EP80579 Integrated Processor Sequence Controller Interface.................................. 14 Reset Sequence ......................................................................................................... 16 December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 3 Power Sequence and Reset—Application Note Revision History Date Revision Description December 2008 001 Initial release Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 4 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset 1.0 Introduction In the earlier days of Intel Architecture (IA), system designs for power sequence and reset circuitries were simpler and used fewer components to monitor power and power control signals. With fewer power rails, the power sequence was also less complicated. Currently, due to an increased need to support a variety of logic voltage levels—some being legacy, some being new lower levels for supporting higher speeds such as DDR, and some being high speed differentials—the number of required power rails has increased dramatically. These factors have caused the power sequence and reset to become far more complex. Therefore to bring a processor out of reset, the number of power monitors and sequences between supplies requires careful design to meet the specified timings required by the chip set or System on Chip (SoC) devices. Since there is currently no off-the-shelf power supply brick capable of generating the power sequence and all of the required power good signals, designers are required to design with discrete components. This requires a good understanding of how the power sequence and reset functions. This document will help designers meet the required sequence and timing specified in the datasheet. There are also three main points of focus in this application note. The first one is to provide design considerations when implementing Power Sequence and Reset for the Intel® EP80579 Integrated Processor with and without Suspend Power Management. The second is to provide an alternative solution that can eliminate the Super I/O in designs that do not require additional peripherals supported by Super I/O and BOM cost reduction is important. The third point of point of focus in this document is to present relevant information and considerations for successfully bringing out of reset the processor. Note: This Applicaton note has not been validated in hardware, however it has been verified with simulations. Note: The example provided in this document is an example only, Intel does not endorse any specific device or vendor. 1.1 Reference Documents This document is a supplement to the Data Sheet and Platform Design Guide. The reader of this document must be familiar with the materials and concepts presented in the following documents: • Intel® EP80579 Integrated Processor Product Line Datasheet • Intel® EP80579 Integrated Processor Product Line Platform Design Guide It is highly recommended that Designers review these documents before proceeding. Unless otherwise noted, technical documents are available from your Intel field sales representative or http://www.intel.com/go/soc. December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 5 Power Sequence and Reset—Application Note 1.2 Abbreviations The following table provides a description of the acronyms used in this document. Acronym 2.0 Definition BOM Bill of Materials CPU Central Processing Unit CRU Clock Recovery Unit FET Field-Effect Transistor I/O Input/Output IA Intel Architecture PLD Programmable Logic Device POR Power-on Reset RTC Real Time Clock SOC System on a Chip Core and Standby Power Supply Rails The Intel® EP80579 Integrated Processor product line supports Wake-up from Sleep States, such as S3, S4, and S5. The sleep states are used to save power when the system is not performing transactions or computations. The wake-up function activates the system and resumes operation from the sleep state. Two power well/rail groups are required to support these functions: Suspend (Standby) and Core. The Suspend power wells are necessary to keep portion of the processor alive in order to wake up the rest of the processor and initiate the Core power well supplies. The Core power wells on the other hand are the power supplies required to power the core and allow full operation of the processor. A total of four Suspend (Standby) Power Wells and six Core power wells are required to power the processor. These power wells/rails must be supplied and turned on, one by one, in a sequential order as shown in Figure 1 and Figure 2. The timing sequence for initiating each supply must be carefully met to ensure proper functionality. The following sections will describe how to accomplish Power-on Reset (POR) in two manners: POR with Suspend Power Management and POR Without Suspend Power Management. 3.0 Power Sequence With Suspend Power Management Various methods exist to sequentially turn on the power supplies in a sequential manner using either a regular programmable logic device (PLD) and additional analog logic circuitry to monitor voltage levels, a programmable Power Supply Sequencing Controller to monitor voltage levels within a specific window range (i.e., Lattice Semiconductors ispPAC-POWR1014/1220), or other similar integrated analog and digital devices. The following information highlights the critical sequence and timing requirements, as described in the datasheet and Figure 1, that need to be implemented during POR to ensure proper operation and reliability of the system. Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 6 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset VCCPRTC During the initial power up sequence, the first power rail that needs to be present is VCCPRTC. This rail is required by the Real Time Clock (RTC) and must maintain power at all times to keep the RTC functioning. Normally, this voltage level is provided by a back-up lithium battery. As VCCPRTC becomes stable, it is required to maintain the RTC circuit in reset. Notice in Figure 1 that T1 has a minimum of 18ms, which is the minimum time required to maintain RTEST# low, keeping the RTC circuit in reset, until VCCPRTC becomes stable. Note: An RC circuit time delay can be used to maintain RTEST# low and meet the 18ms minimum as described in the Platform Design Guide. RSMRST# The second critical timing that must be met is that of the RSMRST# (Resume Reset). This signal is typically generated by the Super I/O device, but it can also be generated by other devices such as a PLD or the ispPAC-POWR1014. The RSMRST# signal must be released at T2 minimum of 10ms after VCC1P2USBSUS, the last suspend core supply that has been stabilized. VRMPWRGD The third critical timing that is required to be met is the minimum time for the clock synthesizer to stabilize before asserting VRMPWRGD. The minimum requirement is 2ms (T3) to allow the CRU Clock to become stable before VRMPWRGD is asserted. SYS_PWR_OK/PWROK/PWRGD The fourth critical timing that must be met is that of the three power good and power OK input signals: SYS_PWR_OK, PWROK, and PWRGD. These signals can be combined together so that they are generated from a single source. They can also be generated from a PLD or the ispPAC-POWR1014. SYS_PWR_OK, PWROK, and PWRGD must be initiated as a result of the last stable core voltage, VCCVC (CPU core power supply), to come up. Therefore, SYS_PWR_OK, PWROK, and PWRGD inputs must be held low at T4 for a minimum of 100ms after VRMPWRGD has been generated. This ensures that after VCCVC has come up and become stable; power good for VCCVC is generated with signal VRMPWRGD going from low to high; and, SYS_PWR_OK, PWROK, and PWRGD are released from low to high at the same time. December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 7 Power Sequence and Reset—Application Note Figure 1. Suspend and Core Power Rail Sequence T1 = M in 18m s VC C PR TC (3.3v) > 0m s VC C 50_SU S (5v) > 0m s VC C PSU S (3.3v) VC C G BEPS U S (3.3v) > 0m s VC C SU S 25 (2.5v) VC C SU S 1 (2.5v) > 0m s VC C 1P2_U SBS U S (1.2v) > 0m s G BE _AU X _P W R _G O O D (2.5v) R TEST # (3.3V) T2 = M in 10m s R SM R ST # (3.3V) > 0m s VC C 50 (5v) > 0m s VC C 33 (3.3v) > 0m s VC C 25 (2.5v) > 0m s VC C 18 (1.8v) > 0m s D D R VTT (0.9v) > 0m s VC C (1.2v) > 0m s VC C VC (1.0v -1.3v) > 0m s VTT_PW R G D _N (C K410) T3 = M in 2m s VR M P W R G D (3.3v) T4 = M in 100m s SYS _PW R _O K / PW R O K / PW R G D (3.3v) R evision 001 Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 8 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset 3.1 Implementation The POR sequence described in this section can be implemented in a similar fashion as the example shown in Section 4.0. This would require more resources; therefore, a larger part with more flip-flops and output would be required. An estimated of 48 flip flops might be sufficient, but it will depend if your design requires additional logic implementation. One option can be the Lattice Semiconductors ispPAC-POWR1220. This component can provide enough resources to implement the POR described in this section including the Suspend (Standby) and Core supply voltages required to support Sleep States. Good practice would be to implement the sequence code and simulation to ensure that your design will fit in the device you are selecting. This will help avoid potential problems such as running out of resources after you have routed the board and might need a larger part. Refer to Section 4.0 as the starting point to begin your design. Make the changes necessary to implement the sleep states, and bypass the Super I/O when it is not required in the design. Note: Intel does not guaranteed the functionality of the Lattice device nor do we solely endorse specific vendors for this application. 4.0 Power Sequence Without Suspend Power Management For applications that do not require power management, the power sequence becomes simpler since the number of power supplies are reduced to one supply per power level, therefore Core and Suspend rails can be combined into a single source, reducing almost by half the number of supplies required. Often, embedded applications do not require certain peripherals such as a keyboard, mouse, etc. which are commonly found on PCs. Thus, there is no need to integrate a Super I/O device. A benefit of eliminating the Super I/O, and the glue logic needed to support it, is a reduced BOM cost. Simplifying the system and using less components has another benefit: the need for heat dissipation is reduced which helps to maintain the enclosure cooler. This section provides an example that bypasses or eliminates the Super I/O for designs that have no need for it. Figure 2 was created from information obtained from the datasheet and includes additional signals (also referred to as NETS) required to enable system clocks and power good. The figure shows the timing for POR signals used to generate and monitor the sequence. A programmable Reset Generator and Sequencing Controller is used to control signals, turn on regulators, monitor voltage levels, and generate power good for the system. When looking at Figure 2 we have two naming conventions: one labeled PIN and the other, NET. PIN refers to the pin package in the Intel® EP80579 Integrated Processor, and NET refers to the signals used in Figure 3 and Figure 4. PIN and NET are used to differentiate between the signals to interconnect pins between the two main components. Note: The code required to control the signals shown in Figure 2 has been provided for your use as a reference only and as is. This code can be modified to fit your specific design, however keep in mind not to violate the timing shown in the figures and datasheet. The code is provided in a zip file within this document, the name is December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 9 Power Sequence and Reset—Application Note ispPCA_POWR1014_EP80579.PAC, and it is commented well to help you understand its sequence and implementation. Figure 2. NET Core Power Rail Sequence (No Suspend) ____ PIN ATX_3.3_Volt T1 = Min 18ms VCCPRTC (3.3v) >0ms VCC_5P0 VCC50 (5V) VCC50_SUS (5v) VCC_3P3 VCC33 (3.3v) VCCPSUS (3.3v) VCCGBEPSUS (3.3v) VCC_2P5 VCC25 (2.5v) VCCSUS25 (2.5v) VCCSUS1 (2.5v) >0ms >0ms >0ms VCC_1P8 VCC18 (1.8v) >0ms VCC_0P9 DDRVTT (0.9v) VCC_1P2 VCC (1.2v) VCC1P2_USBSUS (1.2v) >0ms >0ms VCC_CPU VCCVC (1.0v -1.3v) RTC_RST_N RTEST# (3.3V) T2 = Min 10ms IMCH_RSMRST_N RSMRST# (3.3V) >0ms CK410_PWRGD_N VTT_PWRGD_N (CK410) T3 = Min 2ms CPU_VRM_PWR_GD VRMPWRGD (3.3v) T4 = Min 100ms SYS_PWR_OK SYS_PWR_OK / PWROK / PWRGD (3.3v) GBE_AUX_PWR_GOOD (2.5v) Revision 001 Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 10 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset 4.1 Hardware Interface POR Power-on Sequence can be a challenge for the system designer. It can be dependent upon a number of things, from crossing the threshold for Vmin, to time requirement to stabilize and latch signals. The complexity is compounded by the number of power supplies required by the system and the timing required to turn each one on. Figure 3 and Figure 4 provide examples showing how to accomplish the POR described in Figure 2. These examples can be used or modified for user application. Power Supply In Figure 3, the main source power supply can be an ATX silver box or a single supply capable of providing sufficient power to the system. For this particular example there are three power source Vin—12V, 5V, and 3.3V—are required which can be obtained from a Power Brick or an ATX Silver Box. This example can be easily modified to a single voltage power supply of 12V or 5V capable of delivering sufficient power to the system. Reset Generator and Sequencing Controller Figure 3 shows how to connect the Reset Generator and Sequencing Controller to enable and sequence the turning on of all regulators used to bring the processor out of reset. Also shown is a requirement for Power-down, which is simply the reverse order of Power-on. December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 11 Power Sequence and Reset—Application Note Figure 3. IspPAC Sequence Controller Interface 100 Ω=°° FET 5P0 EN From ATX 5.0 Volt Inverter Level converter From ATX 12 Volt Note1: 100 Ω=°° FET 3P3 EN 4.7 KΩ=° ° From ATX 3.3 Volt 10 KΩ=°° 2N3904 From ATX 3.3 Volt 2P5_EN From ATX 3.3 Volt From ATX 3.3 Volt VCC_1P8 (1.8 V) 100 KΩ=°° VCCJ VCCINP VCCA VCCD HVOUT2 OUT4 VCC_2P5 (2.5 V) V_IN 1P8_EN Note1 ADJ 100 KΩ=°° V_OUT REF_EN VCNTL VCC_0P9 (0.9 V) ON/OFF From ATX 12 Volt VCC_5P0 VMON7 V_OUT Switching Regulator 1.2V VCC_3P3 IspPAC® POWR1014 VMON5 VMON6 1P2_EN Note1 Linear Regulator 0.9V OUT8 VMON4 VCC_1P2 (1.2 V) V_IN OUT7 VMON2 VMON3 ON/OFF From ATX 12 Volt OUT5 OUT6 VMON1 V_OUT Switching Regulator 1.8V RT91173A V_IN VCC_1P8 (1.8 V) V_IN V_OUT SHDN VCC_3P3 (3.3 V) From ATX 12 Volt Linear Regulator 2.5V 4.7 KΩ=° ° HVOUT1 VCC_5P0 (5.0 V) VCC_CPU (1.0-1.3 V) V_IN VCC_EN Note1 V_OUT ON/OFF Switching Regulator 1.0 – 1.3V VCC_5P0 VCC_3P3 VCC_CPU VCC_1P2 VCC_0P9 VCC_2P5 VCC_1P8 VCC_3P3 (3.3 V) 4.7 KΩ=° ° SYS_PWR_OK CPU_VRM_PWR_GD IMCH_RSMRST_N OUT9 OUT10 OUT11 OUT12 CK410_PWR_GD Reset Generator and Sequencing Controller VTT_PWERGD_N CLOCK OUT Clock Synthesizer for Intel SCL SDA VSBY_SMBCLK VSBY_SMBDAT CPU_THERMTRIP_N RTC_RST_N VCCD GNDD IN1 IN2 Note1: Might require to step up logic level of ON/OFF signal of switching regulator. Vout of IspPAC® POWR1014 is only 3.3 Volt level. Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 12 Revision 001 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset SYS_PWR_OK Figure 4 shows some of the main signals required for POR. Notice that NET SYS_PWR_OK can be used to connect to signals PWRGD, PWROK, SYS_PWR_OK and GBE_AUX_GOOD. As this example does not support Suspend Power Wells, Wake on LAN is not supported either; therefore, GBE_AUX_GOOD can be connected to NET SYS_PWR_OK. Reset A Reset button has been provided to generate a warm Reset. The Intel® EP80579 Integrated Processor has an internal debouncer for the switch, so there is no need to provide an external debouncer circuit. The FET transistor Q3 is required, when resetting via the watchdog timer, to pull SYS_RESET_N low. Note that an inverter U5 is necessary to invert the logic and turn on Q3. Debug Port If you are using a debugger such as ITP, consult with the debugger vendor for hardware design requirements. This document does not take into account hardware requirements for ITP except for power good and reset as shown in Figure 4. SMBus The SMBus can be used to obtain the status of the voltage levels of the various supplies, which can then be used to determine the condition and report diagnostic status of the system. This can be very useful for debug and diagnose a problem in the voltage rails. THRMTRIP# Signal THRMTRIP# is generated by Intel® EP80579 Integrated Processor which signals a catastrophic Thermal Protection. In this example the signal is used by the Reset Generator and Sequencing Controller to shut down power to force a power shut down of the device. One of the internal timers in the Reset Generator and Sequencing Controller is programmed to maintain the power enables disables in case of a thermal trip condition. The datasheet recomends that power must be turned off to the Intel® EP80579 Integrated Processor to prevent silicon damage due to thermal runaway. December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 13 Power Sequence and Reset—Application Note Figure 4. Intel® EP80579 Integrated Processor Sequence Controller Interface Intel® EP80579 POWER GOOD SYS_PWR_OK PWRGD PWROK SYS_PWR_OK GBE_AUX_PWR_GOOD CPU_VRM_PWR_GD VRMPWRGD IMCH_RSMRST_N RSMRST# VCC_3P3 (3.3 V) BOARD_RST_N PLTRST# RSTIN# VCC_3P3 (3.3 V) 10 KΩ RESET BUTTON SYS_RESET# 10 KΩ WDT_TOUT# SLP_S5# SLP_S4# SLP_S3# NC NC NC VCC_3P3 (3.3 V) 10 KΩ CPUPWRGD_OUT PWRGOOD 10 KΩ CPURST# DBR RESET VCC_3P3 (3.3 V) ITP CONNECTOR 8.2 KΩ VSBY_SMBCLK VSBY_SMBDAT SMBDATA SMBCLK VCC_3P3 (3.3 V) 10 KΩ CPU_THERMTRIP_N THRMTRIP# VCC_3P3 (3.3 V) 10 KΩ A20GATE From ATX 3.3 Volt 20 KΩ RTC_RST_N RCIN# RTEST# VCCPRTC 1 KΩ 1 uF 1 uF 3.0 Volt Battery Revision 001 Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 14 December 2008 Order Number: 320471-001US Application Note—Power Sequence and Reset 5.0 Troubleshooting for POR Various checks are possible when attempting to isolate a power reset problem. Though there is no preference on how to trace signals, a common approach is to check that all powers rails are properly up, and to ensure that no steps were missed when troubleshooting the problem. The following sections will guide designers in looking for the important signals that are expected to become active at the precise time, as specified in the datasheet. 5.1 Power Supplies If your specific design uses “Power Sequence With Suspend Power Management”: • Ensure that all Suspended voltages are on and that they came up in the sequential order as shown in Figure 1. • Ensure that RTEST_N is high and it has a minimum of 18ms from the positive edge of VCCPRTC. • Ensure that after rail VCC1P2_USBSUS is fully up, the time interval to the positive edge of RSMRST_N has a minimum of 10ms. • Ensure that all Core voltages are turned on, and that they have come up in the sequential order as shown in Figure 1. If your specific design uses “Power Sequence Without Suspend Power Management”: • Ensure that all Suspended and Core voltages are on and that they come up in the sequential order as shown in Figure 2. • Ensure that RTEST_N is high and it has a minimum of 18ms from the positive edge of VCCPRTC. • Ensure that after rail VCC/VCC1P2_USBSUS is fully up, the time interval to the positive edge of RSMRST_N has a minimum of 10ms. 5.2 Clock Synthesizer Enable Note: This verification applies to both “Power Sequence With Suspend Power Management” and “Power Sequence Without Suspend Power Management”. After verifying that the power supplies have come up correctly, ensure that the Clock Synthesizer has been enabled correctly, as shown in either Figure 1 or Figure 2. The clock is required to be enabled as soon as VCCVC (main core voltage for the Intel® EP80579 Integrated Processor) is within the max/min voltage reange as pecified in the datasheet. As shown in the example in Section 4.1, “Hardware Interface POR” on page 11, the Reset Generator and Sequence Controller monitors VCCVC, once the voltage is stable and within VCCVC+/-2%, VTT_PWRGD_N is asserted LOW which enables the Clock Synthesizer. December 2008 Order Number: 320471-001US Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 15 Power Sequence and Reset—Application Note 5.3 Power Good and Power OK • Ensure that VRMPWRGD (VRM Power Good) has asserted 2ms (T3 in Figure 2) after the Clock Synthesizer has been enabled. This delay allows the clock to become stable before asserting VRMPWRGD. This signal tells the Intel® EP80579 Integrated Processor that the VRM power rail has been delivered correctly. • Ensure that SYS_PWR_OK (System Power OK) has asserted 100ms (T4 Figure 2) after VRMPWRGD. This signal tells the Intel® EP80579 Integrated Processor that all core supplies are active and that the system is ready to be removed from reset. • Ensure that PLTRST_N is asserted approximately 1ms after SYS_PWR_OK (Figure 5). This is asserted by the Intel® EP80579 Integrated Processor signaling that the System is ready to be taken out of reset. • Ensure that CPURST_N has asserted 1.12ms after PLTRST_N (Figure 5). This signal tells the outside world the state of the processor either being in Reset or Out of Rest. Normally, this signal is used by the ITP to verify the state of the processor. Figure 5. Reset Sequence Approximately 2.12ms SYS_PWR_OK / PWROK / PWRGD (3.3v) GBE_AUX_PWR_GOOD (2.5v) 1ms PLTRST# RSTIN# GDELAY PCIRST# 1.12ms 1ms + 10,000x10ns + 2,000x10ns CPURST# Revision 001 6.0 Conclusion Power-on Reset is a challenging area for any design. It requires proper planning and calculation to ensure a successful bring up of the system. The reset sequence of power rails for the Intel® EP80579 Integrated Processor, as illustrated in this document, is logical and easy to follow. POR can be accomplished employing various methods—there is no single solution for every design. Following the guidelines presented in this document will ensure proper synchronization of the system voltage rails. Power Sequence and Reset Utilizing the Intel® EP80579 Integrated Processor Product Line Application Note 16 December 2008 Order Number: 320471-001US