* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Chapter 7 Memory Testing C apte Me oy est g

Survey

Document related concepts

Transcript

Chapter

C

apte 7 Memory

Me o y Testing

est g

Jin-Fu Li

Advanced Reliable Systems (ARES) Laboratory

Department of Electrical Engineering

National Central University

JJhongli,

g , Taiwan

Outline

Importance of Embedded Memories

RAM Functional Faults

March Tests

C

Converting

ti Bit

Bit-Oriented

O i t d RAM Tests

T t into

i t WordW d

Oriented RAM Tests

RAM BIST

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

2

Embedded Memory–The Key to SOC

Embedded memory is becoming more central to

integrated

g

circuit design

g

Historically, ICs were dominated by the logic

functions, with memory being external

Today, an SOC contains many memory blocks of

different sizes,

sizes shapes and functionality

Typically, embedded memories represent about

30%~50%

30%

50% SOC area

The Semiconductor Industry Association (SIA)

predicts that 90% of the SOC’s

SOC s surface will be

memory by 2011

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

3

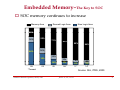

Embedded Memory–The Key to SOC

SOC memory continues to increase

Memory Area

Reused Logic Area

New Logic Area

20%

16%

64%

52%

71%

90%

94%

4%

2%

14*

16%

32%

99

83%

02

13%

9%

16%

8%

6%

4%

05

08*

11*

*Foreast

Advanced Reliable Systems (ARES) Lab.

Source: SIA

SIA, ITRS

ITRS, 2000

Jin-Fu Li, EE, NCU

4

Embedded Memory–Quality

During manufacture

Yield

Exponential yield model

Y = e− AD , where A and D denote the area and

defect density, respectively

After manufacture

Reliability

During use

Soft error rate

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

5

Quality During Manufacture

Issues of embedded memory

As the density

y of transistors is increased, the D is

increased compared to logic

About 2X logic for high density 6-T SRAM

Solutions

Redundancy

y & laser repair

p using

g ATE

Error correction code (ECC)

Redundancy & repair

Achieve yield parity with logic, or better

About 3% area overhead

Recommended over 1Mb

Laser repair manufacturing flow

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

6

Quality During Manufacture

ECC

Detect/repair defects in individual words

25-30% area overhead

Ex: 6 extra bits for single

g bit correction in 32 bit words

Latency penalty

At least one clock cycle

y latency

y penalty

y

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

7

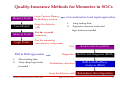

Quality-Insurance Methods for Memories in SOCs

.Large Capture Memory

Conventional test and repair approaches

Memory Tester .Redundancy analysis

Laser Repair

Memory Tester

Logic Tester

.Swap the defective

cells

1

1.

Long testing time

2.

Expensive memory tester and

logic tester are needed

.Test

T t the

th repaired

i d

memories

.Test the remaining

non-memory components

.Test

BIST & BISR approaches

1.

Short testing time

2.

Only cheap logic tester

is needed

Advanced Reliable Systems (ARES) Lab.

.Diagnostics

Built-In Self-Test (BIST)

Built-In Self-Diagnosis (BISD)

.Redundancy allocation

Built-In

l

Redundancy

d d

Analyzer (BIRA)

.Swap the defective cells

Redundancy Reconfiguration

Jin-Fu Li, EE, NCU

8

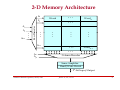

2-D Memory Architecture

S0

A0

A1

Wordi-1

...

...

...

A0

Aj-1

...

...

...

Sn-1

...

...

...

Ak-1

Row Deecoder

S1

Word0

Wordni-1

Column Decoder

Sense Amplifier

Read/Write Circuit

2m-bit

bit Input/Output

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

9

Blo

ock

Co

olumn

Row

3-D Memory Architecture

Input/Output

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

10

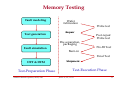

Memory Testing

Fault modeling

Test generation

Wafer

f b i ti

fabrication

Repair

Die separation,

separation

packaging

Fault simulation

Probe test

Post-repair

Probe test

Pre-BI Test

Burn in

Burn-in

Final Test

DFT & DFM

Test Preparation Phase

Test-Preparation

Advanced Reliable Systems (ARES) Lab.

Shipment

Test-Execution

Test

Execution Phase

Jin-Fu Li, EE, NCU

11

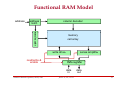

Functional RAM Model

address

address

latch

column decoder

rrow deco

oder

memory

cell array

write

it d

driver

i

read/write

ead/ te &

enable

sense amplifier

lifi

d t register

data

i t

data

in

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

data

out

12

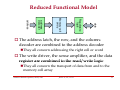

Reduced Functional Model

data

Rea

ad/write

llogic

Mem

mory cell

array

a

ad

ddress

de

ecoder

address

The address latch,, the row,, and the columndecoder are combined to the address decoder

They

y all concern addressing

g the right

g cell or word

The write driver, the sense amplifier, and the data

register are combined to the read/write logic

They all concern the transport of data from and to the

memory cell array

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

13

Reduced Functional Faults

S k fault

Stuck-at

f l (SAF)

Definition:

The logic

Th

l i value

l off a stuck-at

k (SA) cell

ll or line

li is

i

always 0 or 1.

It is always

y in state 0 or in state 1 and cannot be

changed to the opposite state

Detection requirement:

F

From

each

h cell

ll or line,

li

a 0 or 1 mustt be

b read

d

Transition fault (TF)

D fi i i

Definition:

A cell that fails to undergo a 0 to 1 transition when it

is written is said to contain an up transition fault

A down transition fault indicates that a cell fails to

undergo a 1 to 0 transition

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

14

Reduced Functional Faults

A TF can be thought of as a set/reset (S/R)-type flipflop with a SAF on the set or reset input

SA0

S

Q

R

Q

Detection requirement:

Each cell should undergo up and down transitions and be read

after each transition before undergoing further transitions

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

15

State Diagram for SAFs & TFs

w1

w0

S0

w0

S1

w1

State diagram of a good cell

w1

w0

0

S0

w1

1 w0

0

S1

w1

1

w0

0

S0

w0

S1

w1

SA0 fault

Advanced Reliable Systems (ARES) Lab.

SA1 fault

TFu

Jin-Fu Li, EE, NCU

16

Reduced Functional Faults

Coupling faults (CFs)

2-cell coupling faults

Different types of CFs

Inversion CF (CFin)

Idempotent CF (CFid)

State CF (CFst)

Dynamic CF (CFd)

CFin

A 0 to

t 1 (or

( 1 tto 0) ttransition

iti iin one cell

ll iinverts

t th

the

content of a second cell

An CFin can be thought of as a D-type

D type flip-flop

flip flop with an

extra clock input Cd and the Q’ output tied to the D

input,

p , as depicted

p

in the following

g figure.

g

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

17

Reduced Functional Faults

D

CFid

Cn

Cd

Q

Q

A 0 to 1 (or 1 to 0) transition in one cell forces the

content of a second cell to a certain value

value, 0 or 1.

1

An idempotent coupling fault can be thought of as an

S/R type flip-flop

S/R-type

flip flop with an OR-gate

OR gate in the Set or Reset

line, as depicted in the following figure. Sn is the normal

set input

p whereas Sd is the undesired set input

p due to

coupling with one or more other flip flops.

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

18

Reduced Functional Faults

Sn

Sd

S

Q

Rn

R

Q

CFst

CF t

A 0 or 1 state in one cell forces the content of a second

cell to a certain value,

value 0 or 1

It can be thought of as a D-type flip-flop with an

OR/AND gate in the data line (D)

OR/AND-gate

(D), as depicted in the

following figure. Dn is the normal set input whereas Dd

is the undesired set input

p due to coupling

p g with one or

more other flip flops

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

19

Reduced Functional Faults

Dn

Dd

clk

D

Q

Q

Dynamic

D

i Coupling

C

li Fault

F lt (CFd)

Occur between cells in different words. A read or write

operation on one cell forces the content of the second

cell either 0 or 1.

Denoted as <rx|wy; z> where | denotes the or of the

read and write operations

Four possible CFd faults

<r0|w0;0>, <r0|w0;1>,<r1|w1;0>, and <r1|w1;1>

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

20

State Diagrams for CFin & CFid

w1/j

w0/i,

w0/j

w0/i

1/i

w1/i,

w0/j

S00

w0/j

w0/i

w1/i

w1/jj

S10

S01

w0/j

S11

w0/i,

w1/j

w1/i

w1/i,

w1/i

w1/j

State diagram of two good cells

w0/i,

w0/jj

w0/i

S00

w0/j

S01

w1/j

1/j

w1/i

w0/i,

w1/jj

w0/i,

w0/jj

S00

S10

S01

w0/i,

w1/j

w1/j

w0/i

w0/i

w1/i

w0/j

S11

w1/i,

w1/j

State diagram of an CFin<u;i>

Advanced Reliable Systems (ARES) Lab.

w1/i,

w0/j

w0/i

w1/i

w1/j/j

w1/i,

w0/j

w0/j

S10

w1/j

w0/j

S11

w1/i

w1/i,

1/i

w1/j

State diagram of an CFid<u;1>

Jin-Fu Li, EE, NCU

21

Summary of CFs

Note

N t that

th t all

ll d

definitions

fi iti

talk

t lk about

b t single-way

i l

faults, that is, the presence of a CF from cell i to cell

j does

d

nott imply

i l the

th presence off a CF ffrom cell

ll j to

t

cell i.

Suppose that a transition or state in cell j can

induce a coupling fault in cell i. Cell i is then said

to be coupled cell (or victim); cell j is called the

coupling cell (or aggressor).

A test that has to detect and locate all coupling

faults should satisfy

y

For all coupled cells, each cell should be read after a

series of possible coupling faults may have occurred

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

22

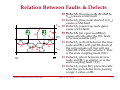

Relation Between Faults & Defects

R

d5

d1

R

d3 d2

BL

Advanced Reliable Systems (ARES) Lab.

D

Defect

f t d1 (inverse

(i

node

d shorted

h t d tto

Vdd) causes a SA0 fault

Defect d2 (true node shorted to Vss)

causes a SA0 fault

Vdd Defect d (open true node gate)

3

cause a SA1 fault

d7

Defect

D f t d4 (an

( open word

d line)

li )

causes all cells after the WL fault

d4

WL

to be inaccessible (AF)

Defect d5 (a short between the true

node and BL) will pull BL down if

d6

the cell contains a 0, but will not

Vss

affect BL if the cell contains 1. This

is the state coupling fault <0;0>

Defect d6 (short between inverse

BL

node and BL’)) is similar, as is the

state coupling fault <1;1>

Defect d7 (open BL’) prevents cells

after the open defect from passing

a logic

l i 1 value

l on BL’

Jin-Fu Li, EE, NCU

23

Relation Between Faults & Defects

R

R

d3

d1

d2

BL

Advanced Reliable Systems (ARES) Lab.

Defect d1 (a word line connected to Vss)

causes all cells in the word line

to be stuck open.

A defect

d f t in

i the

th poly

l silicon

ili

layer

l

Vdd

covering a diffusion region may result

in the creation of an extra pass

transistor This defect (d2) causes a

transistor.

transition fault.

WL

Defect d3 (a broken pull up resistor)

introduces a data retention fault.

fault If the

cell is not accessed, the cell node with

the broken pull up resistor can be

Vss

floating high or active low.

low If the node

is floating high, the leakage current

from the cell node to the substrate will

BL

decline the voltage at the node.

node If the

node voltage passes the threshold

voltage Vth the data in the cell will

invert. If the node is active low,, the cell

will function correctly.

Jin-Fu Li, EE, NCU

24

March Tests

A march test consists of a finite sequence of march

elements

A march element

A finite sequence of Read and/or Write operations

applied to every cell in memory in either increasing

address order (cell 0 to cell n-1) or decreasing address

order (cell n-1 to cell 0)

All operations

p

of a march element are done

before proceeding to the next address

preferred method for RAM

The march tests are a p

testing

Linear

Linear complexity, regularity, and symmetry

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

25

March Test Notation

rx: a read x operation

wx: a write

it x operation

ti

⇑ : increasing addressing sequence (from 0 to n1)

g addressing

g sequence

q

((from n-1 to

⇓ : decreasing

0)

8 : either increasing or decreasing addressing

sequence

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

26

An Example of March Test

An example of march test {⇑ ( w1); ⇑ ( r1, w 0 )}

Addressing

Add

i

cell 0

(w1)

Addressing

Add

i

cell 1

Addressing

Add

i

cell 2

Addressing

Add

i

cell 3

1

X

1

1

1

1

1

1

X

X

X

X

1

X

1

1

Initial state

X

X

X

X

Addressing

cell 0

Addressing

cell 1

Addressing

cell 2

Addressing

cell 3

1

1

0

1

0

0

0

0

1

1

1

1

1

1

0

1

0

1

0

0

0

0

0

0

1

1

1

1

0

1

0

0

(r1,w0)

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

27

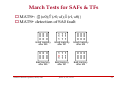

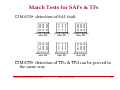

March Tests for SAFs & TFs

MATS+: {8 (w0);⇑ (r0, w1);⇓ (r1, w0)}

MATS+ detection of SA0 fault

0 0 0

0 0 0

0 0 0

1 1 1

1 1 1

1 1 1

0 0 0

0 0 0

0 0 0

Good

G

d memory

after M0

Good

G

d memory

after M1

Good

G

d memory

after M2

0 0 0

0 0 0

0 0 0

1 1 1

0 1 1

1 1 1

0 0 0

0 0 0

0 0 0

Bad memory

after M0

Bad memory

after M1

Bad memory

after M2

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

28

March Tests for SAFs & TFs

MATS+ detection of SA1 fault

0 0 0

0 0 0

0 0 0

1 1 1

1 1 1

1 1 1

0 0 0

0 0 0

0 0 0

Good memory

after M0

Good memory

after M1

Good memory

after M2

0 0 0

1 0 0

0 0 0

1 1 1

1 1 1

1 1 1

0 0 0

1 0 0

0 0 0

Bad memory

after M0

Bad memory

after M1

Bad memory

after M2

MATS+

MATS detection

d

i off TF

TFu & TFd can b

be proved

d iin

the same way

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

29

Tests for Detecting SAFs & TFs

Conditions for detecting SAFs & TFs

SAFs & TFs can be detected by

y a march test which

contains the following two march elements (or single

march element containing both elements)

(..., w0, r 0,...) to detect SA1 faults and TFd

((..., w1, r1,...)) to detect SA0 faults and TFu

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

30

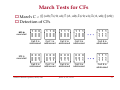

March Tests for CFs

March C -: {8 (w0);⇑ (r0, w1);⇑ (r1, w0); ⇓ (r0, w1); ⇓ (r1, w0);8 (r0)}

Detection of CFs

M1 is

executed

M3 is

executed

1 0 0

0 0 0

0 0 0

1 1 0

0 0 0

0 0 0

1 1 1

0 0 0

0 0 0

1 1 1

1 0 0

0 0 0

1 1 1

1 1 1

1 1 1

Cell 0 is

addressed

Cell 1 is

addressed

Cell 2 is

addressed

Cell 3 is

addressed

Cell 8 is

addressed

0 0 0

0 0 0

0 0 1

0 0 0

0 0 0

0 1 1

0 0 0

0 0 0

1 1 1

0 0 0

0 0 1

1 1 1

1 1 1

1 1 1

1 1 1

Cell 0 is

addressed

Cell 1 is

addressed

Cell 2 is

addressed

Cell 3 is

addressed

Cell 8 is

addressed

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

31

March Tests for CFs

Conditions

C diti

for

f detecting

d t ti CFs

CF

A march test which contains one of the two pairs of march

elements of Case A & Case B can detect simple CFs (CFin, CFst,

CFid)

Case A

1. ⇑ (rx,", wx) ⇑ (r x,", wx)

2. ⇓ (rx, " , w x) ⇓ (r x, ", wx)

Case B

1. ⇑ (r x, " , wx ) ⇑ (rx, " , w x)

2. ⇓ (r x, " , wx ) ⇓ (rx, " , w x)

A.1 (A.2) will sensitize the CFs, and it will detect

the fault, when the value of the fault effect is x’ ((x),

)

by the rx (rx’) operation of the first (second) march

element when the coupled cell has a higher (lower)

address than the coupling cell

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

32

March Tests for DRFs

Data retention faults (DRFs)

DRF has two subtypes

A stored ‘1’ will become a ‘0’ after a time T

A stored ‘0’ will become a ‘1’ after a time T

Conditions

d

for

f detecting

d

DRFs

Any march test can be extended to detect DRFs

The detection of each of the two DRF subtypes requires

that a memory cell be written into the corresponding

l i states

logic

t t

If we are interested in detecting simple DRFs only

The delay elements can be placed between any two

pairs of march elements, e.g., ⇑ (rx,", wx) ; Del; ⇓ (r x,", wx)

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

33

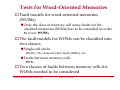

Tests for Word-Oriented Memories

Fault models for word-oriented memories

(WOMs)

Only the class of memory cell array faults for bitoriented memories (BOMs) has to be extended in order

t cover WOM

to

WOMs

The fault models for WOMs can be classified into

two classes

l

Single-cell faults

SAFs, TFs, data retention faults (DRFs), etc.

Faults between memory cells

CFs

CF

Two classes of faults between memory cells for

WOM needed

WOMs

d d to b

be considered

id d

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

34

Tests for Word-Oriented Memories

CFs in BOMs

CFs in WOMs

Inter-word CFs & intra-word CFs

Intra-word

CF

Advanced Reliable Systems (ARES) Lab.

Inter-word

Inter

word

CF

Jin-Fu Li, EE, NCU

35

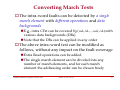

Converting March Tests

Any given BOM march test can be converted to a

WOM march

a c test

With additional tests to cover intra-word faults

A WOM march test is a concatenation of two

march tests

{Inter word march test

{Inter-word

test, intra-word

intra word march test}

The inter-word march test can directly be

obtained

bt i d from

f

the

th BOM march

h ttestt

Replace the bit-operation “r0”, “w0”, “r1”, and “w1”

with the word-operation

word operation “rD”

rD , “wD”

wD , “rD’”

rD , and

“wD’”, where D is called data background

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

36

Converting March Tests

The intra-word faults can be detected by a single

march element with different

ff

operations

p

and data

backgrounds

E.g.,

g intra CFst can be covered by

y (wd1, rd1,...,wdn , rdn ) with

various data backgrounds (DBs)

Note that the DBs can be applied in any order

The above intra-word test can be modified as

follows,, without any

y impact

p

on the fault coverage

g

Extra Read operations can be added

Thee single

s g e march

a c eelement

e e t ca

can be divided

d ded into

to any

a y

number of march elements, and for each march

element the addressing order can be chosen freely

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

37

Compact WOM Tests

If you have a bit-oriented march test, then you can

obtain a compact

p

WOM test with

Replace the bit-operation “r0”, “w0”, “r1”, and “w1”

with all-0 and all-1 data backgrounds

Concatenate a march element ( wd , w d , r d , wd , rd ) for

d={0101..01,0011..11, …}

For example,

l the

h March

h C- can be

b extended

d d as

follows to test a memory with 4-bit words

{8 ( w 0000 ); ⇑ ( r 0000 , w11111 ); ⇑ ( r11111 , w 0000 );

⇓ ( r 0000 , w1111 ); ⇓ ( r1111 , w 0000 ); 8 ( r 0000 );

8 ( w 0101 , w1010 , r1010 , w 0101 , r 0101 );

8 ( w 0011 , w1100 , r1100 , w 0011 , r 0011 )}

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

38

Memory Organization & WOM Tests

WOMs can be organized internally in many

different ways

Adjacent; interleaved; sub-arrays

adjacent

j

interleaved

sub-array

For sub-array organized WOMs, the BOM tests for

CFs will detect the CFs within a B-bit word such that

no intra-word tests are required

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

39

RAM BIST

A typical RAM BIST consists of the following

components

p

Controller, test pattern generator, and comparator

Controller

Generate control signals to the test pattern generator &

the memory under test

Test pattern generator (TPG)

Generate the required test patterns and Read/Write

signals

Comparator

Evaluate the response

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

40

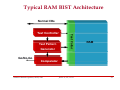

Typical RAM BIST Architecture

Normal I/Os

Test Pattern

Generator

Test Collar

C

T t Controller

Test

C t ll

RAM

Go/No-Go

Comparator

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

41

RAM BIST

In general, two BIST approaches have been

proposed

p

p

for the RAMs

FSM-based RAM BIST

ROM-based RAM BIST

Controller

Generate control signals to the test pattern generator &

the memory under test

Test pattern generator (TPG)

Generate the required test patterns and Read/Write

signals

Comparator

Evaluate the response

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

42

Controller

An example of the state diagram of controller

Advanced Reliable Systems (ARES) Lab.

W0

S0

R0

S1

W1

S2

R1

S3

W0

S4

R0

S5

W1

S6

End

S7

NOT last address?

NOT last address?

NOT first address?

NOT first address?

Jin-Fu Li, EE, NCU

43

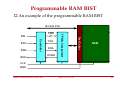

Programmable RAM BIST

An example of the programmable RAM BIST

Normal I/Os

BRS

Co

ontrollerr

BSC

BGO

TGO

ENA

DONE

Test Collar

BSI

TPG & Comparator

CMD

RAM

CLK

BNS

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

44

FSM State Diagram of the Controller

Idle

BRS=1

BSC=1

DONE=1

Shift

Shift_cmd

d

BSC=0

Get_cmd

Apply

ENA=1

DONE=0

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

45

Programmability

The programmability can be achieved by using

test command

The test command format

/

OP

Data background

g

U/D

U/D: ascending/descending address sequence

OP: test operations

OP:

For example, wa, rawa’, rawa’ra, warawa’ra’, etc.

Data

Data backgrounds

The width of each field affects the

programmability of the BIST design

For example, if 4 bits are used for OP, then only 16

possible test operations can be generated

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

46

FSM State Diagram of the TPG

ENA=0

Idle

ENA=1

Init

DONE/GO

Null=1

Null=0

Ifetch

Exec

Dfetch

No-Go

Error=1

Advanced Reliable Systems (ARES) Lab.

Compare

Error=0

Jin-Fu Li, EE, NCU

47

ROM-Based BIST

A typical ROM model

X

p

m

ROM

2 m+ p × (n + p)

p

n

Register

n

Y

Source: R. Senhadji-Navarro, et al., Electronic Letters, 2004

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

48

ROM-Based BIST

A typical ROM model for March test elements

h

March

Address

000_000

element

CEN WEN

Invert

Addr Incr

Addr_Incr

State

Idle

0

0

0

0

000

1

0

0

1

000

010_000

1

1

0

1

000

ra

011_000

1

1

0

0

001

ra

011_001

1

0

1

1

000

wa’

100_000

1

1

1

0

001

ra’

100_001

1

0

0

1

000

wa

001_000

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

wa

49

Serial BIST

Today’s telecommunication ICs often have a

variety

y of multi-port

p

memories on one chip

p

Typical RAM BISTs evaluate all the bits of a

memory word in parallel as it is read

We can encounter significant problems when

applying these BIST schemes to chips that have

multiple embedded RAMs of varying sizes and port

configurations

The area cost of these BIST designs would be

unacceptably high

One better solution is a serial BIST technique

To share BIST design among several RAMs

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

50

Benefits of Serial BIST

Only a small amount of additional circuitry is

required

Only a few lines are needed to connect the RAM to

the

h test controller

ll

Several RAM blocks easily share the BIST

controller hardware

p

the

The serial-access mode does not compromise

RAM cycle time

Existing memory designs do not need any

modification to use the serial interface

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

51

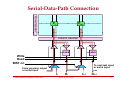

Serial-Data-Path Connection

Row d

decoder

Ci

Ci+1

Column decoder

L t h

Latch

L t h

Latch

Write

Read

BIST on

To next test input

or serial input

From previous output

or serial input

Ii

Advanced Reliable Systems (ARES) Lab.

Oi

Jin-Fu Li, EE, NCU

Ii+1

Oi+1

52

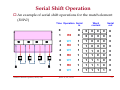

Serial Shift Operation

An example of serial shift operations for the match element

(R0W1)

Time Operation Serial

in

0

0

11

010

00

000

00

00

000

1

X

1

Advanced Reliable Systems (ARES) Lab.

000

0

X

Word

content

Serial

out

X

0

0

0

0

X

1

R0

X

0

0

0

0

0

2

W1

1

1

0

0

0

0

3

R0

1

1

0

0

0

0

4

W1

1

1

1

0

0

0

5

R0

1

1

1

0

0

0

6

W1

1

1

1

1

0

0

7

R0

1

1

1

1

0

0

8

W1

1

1

1

1

1

0

Jin-Fu Li, EE, NCU

53

Serial March (SMarch)

Assume that a RAM has W words, and each word

contains C bits

A Read operation is denoted by R0, R1, or Rx,

depending on the expected value at the serial

output (x=don’t care)

For a write operation,

operation the terms W0 or W1 are used

and only the serial input is forced to the value

indicated

The SMarch modified from March C- is as follows

C

C

C

C

8

(

R

RxW

W

0

)

(

R

0

,

W

0

)

;

⇑

(

R

0

,

W

1

)

(

R

1

,

W

1

)

⇑ ( R 1, W 0 ) C ( R 0 , W 0 ) C ; ⇓ ( R 0 , W 1) C ( R 1, W 1) C

⇓ ( R 1, W 0 ) C ( R 0 , W 0 ) C ; ⇓ ( R 0 , W 0 ) C ( R 0 , W 0 ) C

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

54

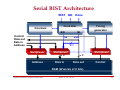

Serial BIST Architecture

BIST GO Done

Counters

SO

Control

Data out

Data in

Address

Timing

generator

Controller

SI

lsb

msb

C-1

M ltiple er

Multiplexer

Address

Add

M ltiple er

Multiplexer

M ltiple er

Multiplexer

C

C

Data

D t iin

Data

D t outt

Control

C t l

RAM (W words of C bits)

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

55

References

[1]

[ ] M. Sachdev,”Defect

,

Oriented Testing

g for CMOS Analog

g and Digital

g

Circuits”, Kluwer Academic, 1999.

[2] M.-L. Bushnell and V.-D. Agrawal,”Essentials of Electronic Testing for

Digital, Memory & Mixed-Signal VLSI Circuits”, Kluwer Academic, 2000.

[3] A.

A J.

J van de

d Goor

G

and

d C.

C A.

A Verruijt,”An

V

ij ”A Overview

O

i

off Deterministic

D

i i i

Functional RAM Chip Testing”, ACM Computing Surveys, vol. 22, no. 1,

March 1990.

[4] A. J. van de Goor, I. B. S. Tlili, and S. Hamdioui,”Converting

Hamdioui, Converting March Tests

for Bit-Oriented Memories into Tests for Bit-Oriented Memories”, MTDT, pp.

46-52, 1998.

[5] A. J. van de Goor and G. N. Gaydadjiev,”March U: a test for unlinked

memory faults”,

f lt ” IEE P

Proc. Circuit

Ci it D

Devices

i

Syse.,

S

vol.144,

l 144 no. 3,

3 pp.155-160,

155 160

1997.

[6] D. S. Suk and S. M. Reddy,” A march test for functional faults in

semiconductor random

random-access

access memories

memories” IEEE Trans. Comput., C-30,

C 30, 12,

pp.982-985, 1981.

[7] K. L. Cheng, M. F. Tsai, and C. W. Wu,”Neighborhood pattern-sensitive

fault testing and diagnostics for random-access memories”, IEEE Trans. CAD,

vol.21,

l 21 no.11,

11 pp. 1328-1336,

1328 1336 nov., 2002

2002.

[8]C. F. Wu, C. T. Huang, and C. W. Wu”RAMSES: a fast memory fault

simulator,” DFT99, pp.199-202, 1996.

[9] B.

B Nadeau-Dostie

Nadeau-Dostie, A.

A Silburt,

Silburt and V.

V K.

K Agarwal

Agarwal,”Serial

Serial interfacing for

embedded-memory testing”, IEEE D&T, pp.52-63, apr. 1990.

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

56

References

[10] C. W. Wu,”VLSI testing & design for testability II: Memory built-in

self-test”, http://larc.ee.nthu.edu.tw/~cww/

[11] A. J. van de Goor and C. A. Verruijt,”An Overview of Deterministic

Functional RAM Chip Testing

Testing”, ACM Computing Surveys

Surveys, vol

vol. 22

22, no

no. 11,

March 1990.

[12] A. K. Sharma,”Semiconductor Memories – Technology, Testing, and

Reliability”,

y IEEE PRESS, 1997.

[13] R. Dekker, F. Beenker, and L. Thijssen,”Fault Modeling and Test

Algorithm Development for Static Random Access Memories”, Int. Test

Conf., pp. 343-352, 1988.

[14] M.

M S

Sachdev,”Defect

hd ”D f t O

Oriented

i t dT

Testing

ti ffor CMOS A

Analog

l and

d Di

Digital

it l

Circuits”, Kluwer Academic, 1998.

[15] B. F. Cockburn,”Tutorial on Semiconductor Memory Testing”, JETTA,

pp. 321

321-336,

336, 1994.

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

57